# Università degli Studi di Padova

#### Dipartimento di Ingegneria dell'Informazione

MASTER THESIS IN ELECTRONIC ENGINEERING

# Co-design of a Class-D Oscillator and Dedicated DC-DC Power Converter

Academic Year: 2022/2023

10 October 2023

ii

# Abstract

This thesis analyses the design problems behind the realization of an integrated oscillator directly powered by a switching voltage regulator. Additionally, the possibility of using the oscillator itself to provide the switching frequency for the converter is explored. The building blocks constituting the circuit are analysed focusing on the different design challenges of each component, on how they interact with each other and if it is possible to obtain a fully integrated design. Some possible design solutions are then provided at the end of the thesis including simulation results for the presented circuits.

# Contents

| In     | Introduction                   |                                |                                                  | 1  |  |

|--------|--------------------------------|--------------------------------|--------------------------------------------------|----|--|

| 1      | LC                             | LC Harmonic Oscillators Theory |                                                  |    |  |

|        | 1.1                            | Feedb                          | ack Theory Analysis                              | 5  |  |

|        | 1.2 Negative Resistance Method |                                |                                                  | 7  |  |

|        | 1.3                            | 3 The Cross-Coupled Pair       |                                                  |    |  |

|        | 1.4                            | Class-                         | B Oscillators                                    | 10 |  |

|        |                                | 1.4.1                          | Voltage and Current Limited Regime               | 12 |  |

|        | 1.5                            | Phase                          | Noise                                            | 13 |  |

|        |                                | 1.5.1                          | Phase Noise in Oscillators - LTI Approach        | 15 |  |

|        |                                | 1.5.2                          | Phase Noise in Oscillators - LTV Approach        | 18 |  |

|        |                                | 1.5.3                          | The Figure of Merit                              | 23 |  |

|        |                                | 1.5.4                          | Effects of Phase Noise                           | 23 |  |

|        | 1.6                            | Frequ                          | ency Pushing                                     | 28 |  |

| 2      | Clas                           | ss-D Os                        | scillators                                       | 31 |  |

| 2.1 To |                                | Topol                          | ogy Overview                                     | 31 |  |

|        |                                | 2.1.1                          | Oscillation Frequency                            | 32 |  |

|        |                                | 2.1.2                          | Voltage Waveforms                                | 37 |  |

|        |                                | 2.1.3                          | Current Consumption                              | 38 |  |

|        |                                | 2.1.4                          | Phase Noise of a Class-D Oscillator              | 38 |  |

|        | 2.2                            | Class-                         | D VCO                                            | 39 |  |

| 3      | Switched Capacitor Converters  |                                |                                                  |    |  |

|        | 3.1                            | Theor                          | etical Analysis and Derivation of an Ideal Model | 43 |  |

|        |                                | 3.1.1                          | Modelling of the Output Resistance               | 45 |  |

|        |                                | 3.1.2                          | Output Voltage Ripple                            | 48 |  |

|              |                                     | 3.1.3   | Symmetric Charge-Discharge Topology              | 50 |  |  |

|--------------|-------------------------------------|---------|--------------------------------------------------|----|--|--|

|              |                                     | 3.1.4   | Phase Interleaving                               | 52 |  |  |

|              | 3.2 Derivation of Efficiency Limits |         | tion of Efficiency Limits                        | 53 |  |  |

|              |                                     | 3.2.1   | Sizing of the Mosfets                            | 57 |  |  |

|              |                                     | 3.2.2   | Partial Charging                                 | 59 |  |  |

|              | 3.3                                 | Outpu   | t Voltage Control                                | 60 |  |  |

|              |                                     | 3.3.1   | Digital Capacitance Modulation                   | 62 |  |  |

|              | 3.4                                 | Additi  | onal Circuits                                    | 64 |  |  |

|              |                                     | 3.4.1   | Non Overlapping Clock Generator                  | 64 |  |  |

|              |                                     | 3.4.2   | Start-Up Circuit                                 | 65 |  |  |

| 4            | Circ                                | uit Des | ign and Simulation                               | 67 |  |  |

|              | 4.1                                 | Desigr  | n of a Class-D VCO                               | 67 |  |  |

|              |                                     | 4.1.1   | Simulation of the VCO                            | 69 |  |  |

|              | 4.2                                 | Desigr  | of the SC Converter                              | 72 |  |  |

|              |                                     | 4.2.1   | Simulation of the SC Converter                   | 74 |  |  |

|              | 4.3                                 | Simula  | ation of the SC Powered Class-D VCO              | 75 |  |  |

|              |                                     | 4.3.1   | Considerations on the use of External Capacitors | 82 |  |  |

|              |                                     | 4.3.2   | Simulation with Phase Interleaving               | 83 |  |  |

| Conclusions  |                                     |         |                                                  |    |  |  |

| Bibliography |                                     |         |                                                  |    |  |  |

| Ac           | Acknowledgements                    |         |                                                  |    |  |  |

# List of Figures

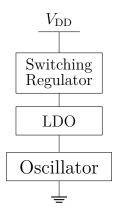

| 1    | Power supply scheme for a conventional oscillator            | 2  |

|------|--------------------------------------------------------------|----|

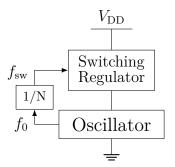

| 2    | Power supply scheme for the oscillator in our thesis         | 2  |

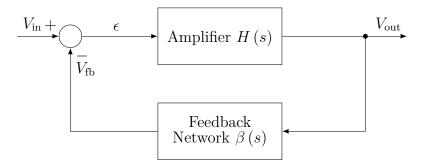

| 1.1  | General model of a feedback system                           | 6  |

| 1.2  | Response of an unstable system oscillating at $\omega_0$     | 7  |

| 1.3  | Lossless <i>LC</i> tank                                      | 7  |

| 1.4  | Lossy <i>RLC</i> tank                                        | 8  |

| 1.5  | Harmonic <i>RLC</i> oscillator                               | 8  |

| 1.6  | Cross-coupled pair                                           | 9  |

| 1.7  | Equivalent small signal scheme of a cross-coupled pair       | 9  |

| 1.8  | Class-B oscillator                                           | 10 |

| 1.9  | Equivalent circuit of a Class-B oscillator                   | 11 |

| 1.10 | $\hat{V}_{ m LO}$ as a function of $I_{ m bias}$             | 13 |

| 1.11 | Output waveforms for an ideal and a noisy oscillator         | 13 |

| 1.12 | Comparison between ideal and noisy spectra of an oscillator  | 14 |

| 1.13 | Specification of phase noise                                 | 15 |

| 1.14 | Equivalent circuit of a noisy harmonic <i>RLC</i> oscillator | 15 |

| 1.15 | Phase noise behaviour of a real oscillator                   | 18 |

| 1.16 | Impulse response of a <i>LC</i> tank                         | 19 |

| 1.17 | Comparison between ISF and output waveform of an oscillator  | 20 |

| 1.18 | Noise folding principle                                      | 21 |

| 1.19 | Receiver scheme                                              | 23 |

| 1.20 | Downconversion with an ideal LO                              | 24 |

| 1.21 | Downconversion with a noisy LO                               | 24 |

| 1.22 | System model for digital transmission of an isolated pulse   | 25 |

| 1.23 | Examples of QAM constellations                               | 26 |

| 1.24 | Examples of PSK constellations                                                              | 27 |

|------|---------------------------------------------------------------------------------------------|----|

| 1.25 | Output spectrum of an oscillator with ripple on the power supply                            | 29 |

| 2.1  | Class-D oscillator scheme                                                                   | 31 |

| 2.2  | Equivalent scheme of a Class-D oscillator with floating capacitance                         | 33 |

| 2.3  | Equivalent scheme of a Class-D oscillator with single-ended capacitance                     | 33 |

| 2.4  | Currents on the inductors $L_a$ and $L_b$                                                   | 34 |

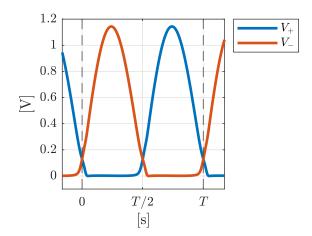

| 2.5  | Output voltage waveforms for a Class-D oscillator                                           | 37 |

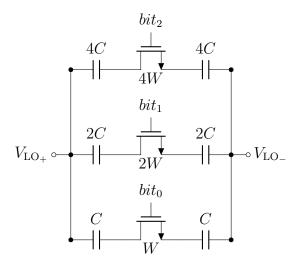

| 2.6  | 3bit floating capacitor bank                                                                | 40 |

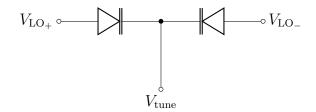

| 2.7  | Circuit for fine tuning of the oscillation frequency                                        | 40 |

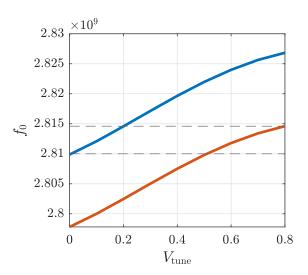

| 2.8  | Example of tuning range behaviour for a VCO                                                 | 41 |

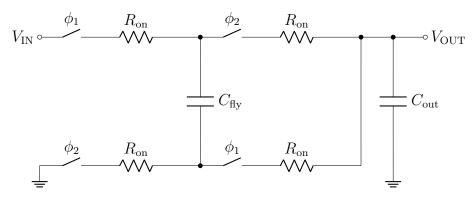

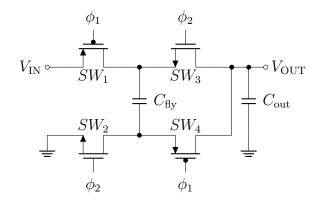

| 3.1  | Simplified schematic of a 1/2 SC converter                                                  | 43 |

| 3.2  | Variation of the SC converter topology based on $\phi_{1,2}$                                | 44 |

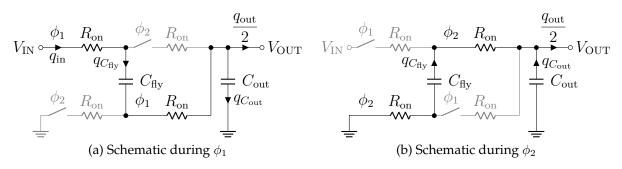

| 3.3  | Ideal transformer model                                                                     | 45 |

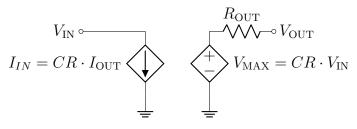

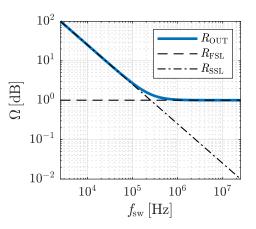

| 3.4  | Example of the frequency behaviour of resistance $R_{OUT}$                                  | 45 |

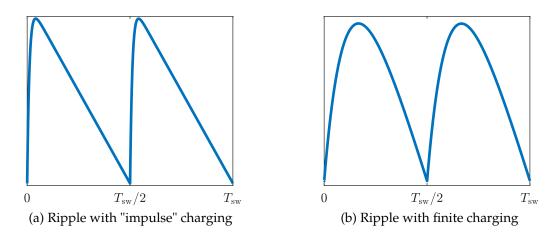

| 3.5  | Ripple behaviour                                                                            | 48 |

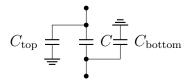

| 3.6  | Top and bottom plate capacitance in a capacitor                                             | 50 |

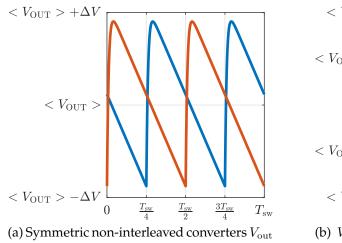

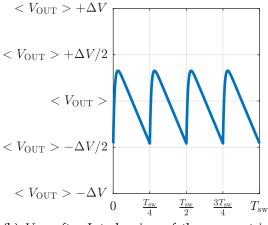

| 3.7  | Comparison of voltage ripple between converters                                             | 50 |

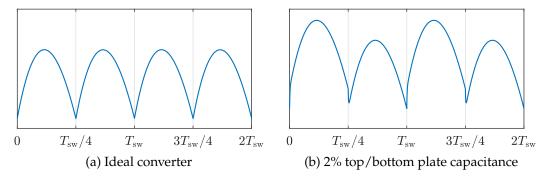

| 3.8  | Asymmetric converter topology                                                               | 50 |

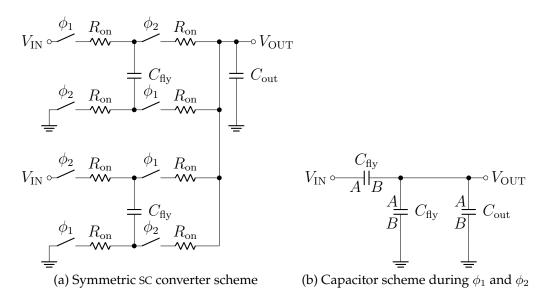

| 3.9  | Symmetric converter topology                                                                | 51 |

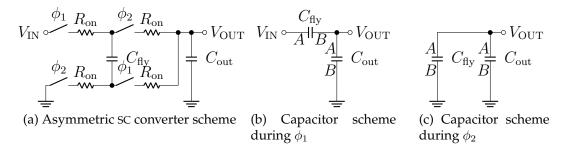

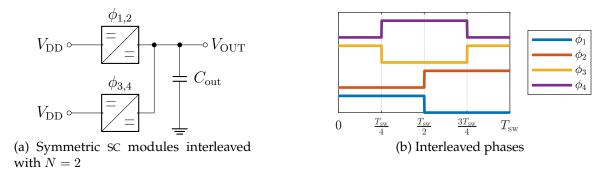

| 3.10 | Phase utilization and topology of a phase interleaved converter                             | 52 |

| 3.11 | Comparison of voltage ripple between converters                                             | 52 |

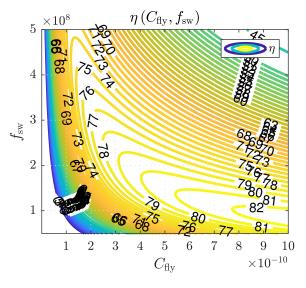

| 3.12 | $\eta\left(C_{\mathrm{fly}}, f_{\mathrm{sw}}\right)$ using technology values                | 56 |

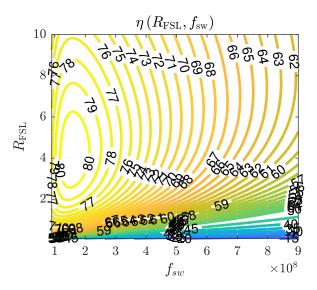

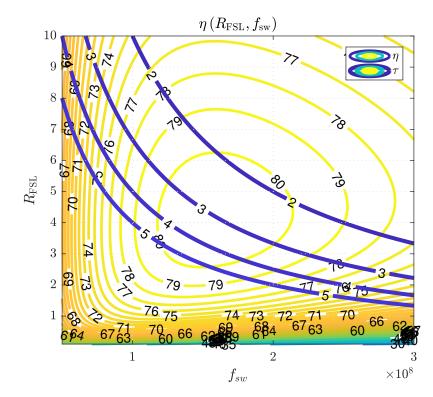

| 3.13 | $\eta(R_{\rm FSL}, f_{\rm sw})$ using technology values                                     | 56 |

| 3.14 | SC converter scheme with real mosfet switches                                               | 57 |

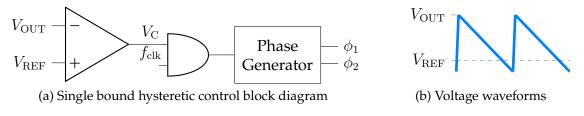

| 3.15 | Voltage control using PFM technique                                                         | 60 |

| 3.16 | SWM principle                                                                               | 61 |

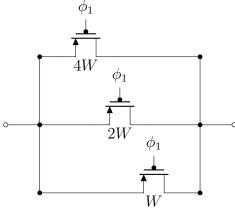

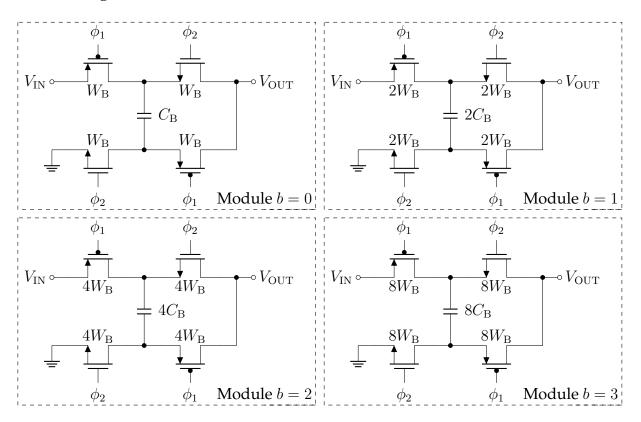

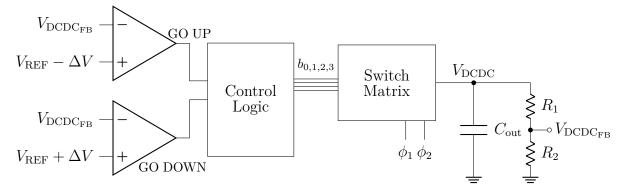

| 3.17 | DCM converter scheme for $b = 4$                                                            | 62 |

| 3.18 | Equivalent scheme of a converter employing DCM                                              | 63 |

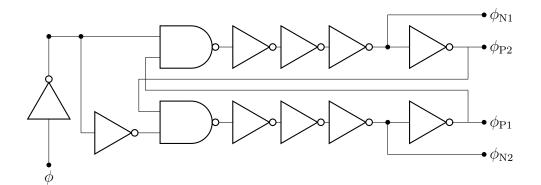

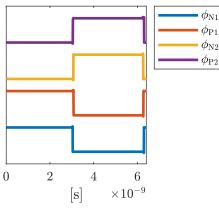

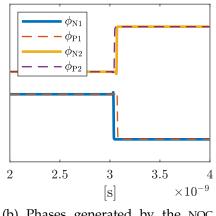

| 3.19 | Circuit scheme of a NOC generator                                                           | 64 |

| 3.20 | Phases generated by a NOC circuit                                                           | 64 |

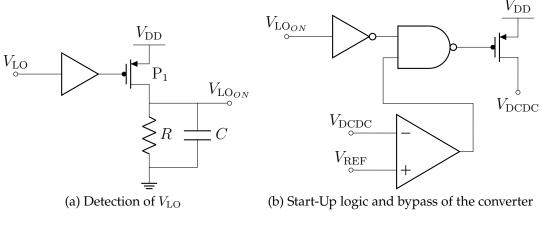

| 3.21 | Start-Up circuit scheme                                                                     | 66 |

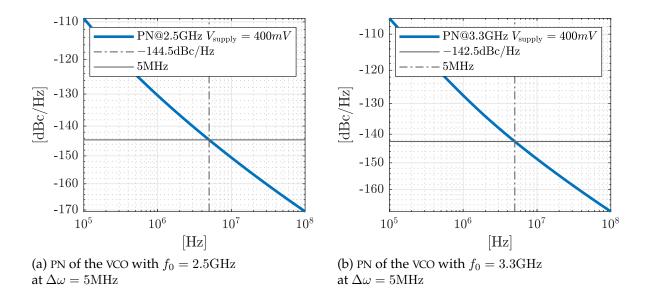

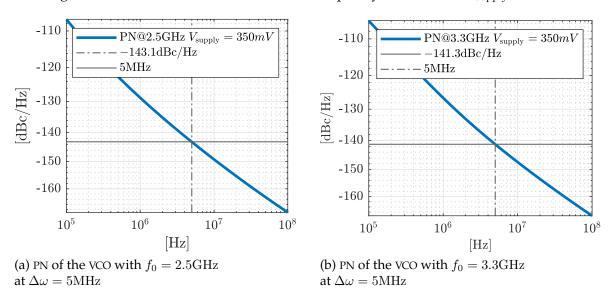

| 4.1  | PN of the VCO at its oscillation frequency extremes for $V_{\text{supply}} = 400 \text{mV}$ | 69 |

| PN of the Voltage Controlled Oscillator (VCO) at its oscillation frequency                                                     |                                   |

|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| extremes for $V_{\text{supply}} = 350 \text{mV}$                                                                               | 69                                |

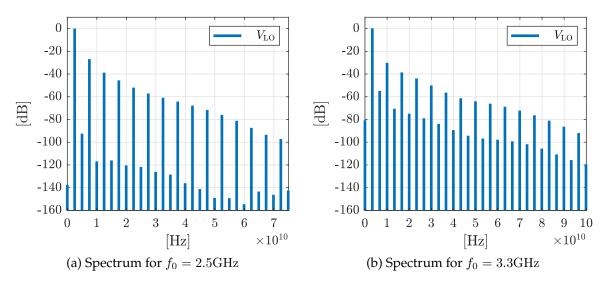

| Output spectrum of the VCO for ideal power supply                                                                              | 70                                |

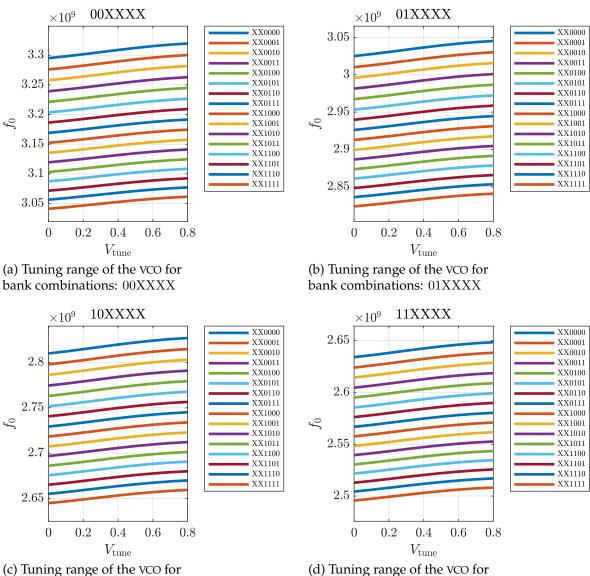

| Tuning range of the VCO                                                                                                        | 71                                |

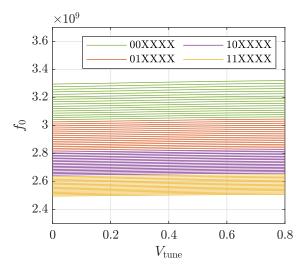

| Tuning range of the VCO - All curves together                                                                                  | 71                                |

| Efficiency as a function of $f_{\rm sw}$ and $C_{\rm fly}$ fixing 4 time constants $\tau$                                      | 72                                |

| Efficiency as a function of $f_{sw}$ and $R_{FSL}$                                                                             | 73                                |

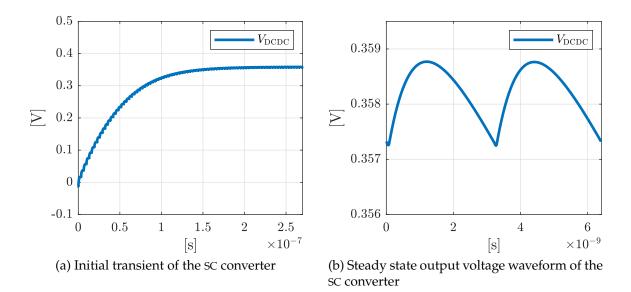

| Simulation of the SC converter with $C_{\rm out} = 10$ nF, $f_{\rm sw} = 156$ MHz and ideal                                    |                                   |

| load current $I_{\rm DC} = 12.4 \text{mA}$                                                                                     | 74                                |

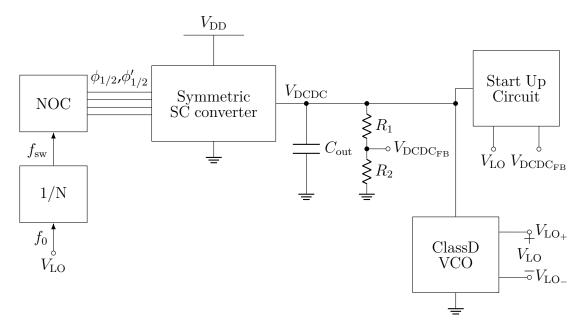

| Block diagram of the SC powered Class-D VCO                                                                                    | 75                                |

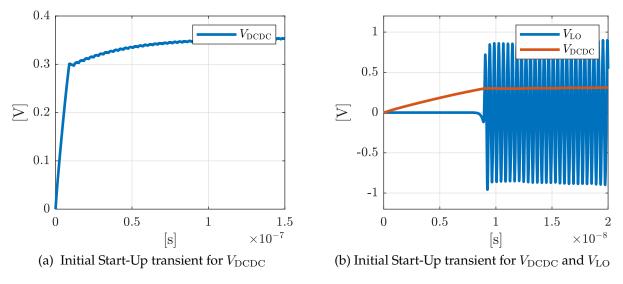

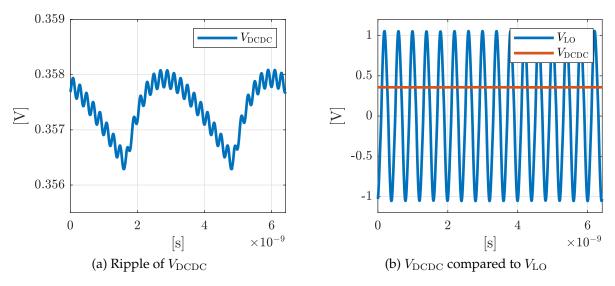

| Transient simulation of $V_{\text{DCDC}}$ and $V_{\text{LO}}$                                                                  | 76                                |

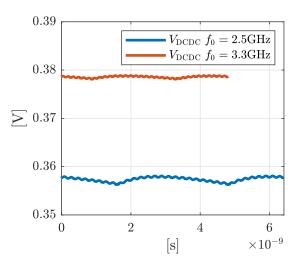

| $V_{\text{DCDC}}$ and $V_{\text{LO}}$ in a period for $f_0 = 2.5 \text{GHz}$                                                   | 77                                |

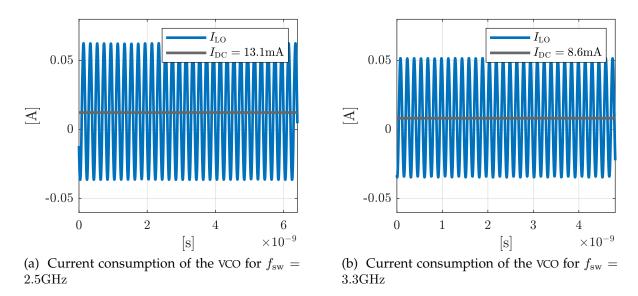

| Current consumption of the VCO for different $f_0$                                                                             | 77                                |

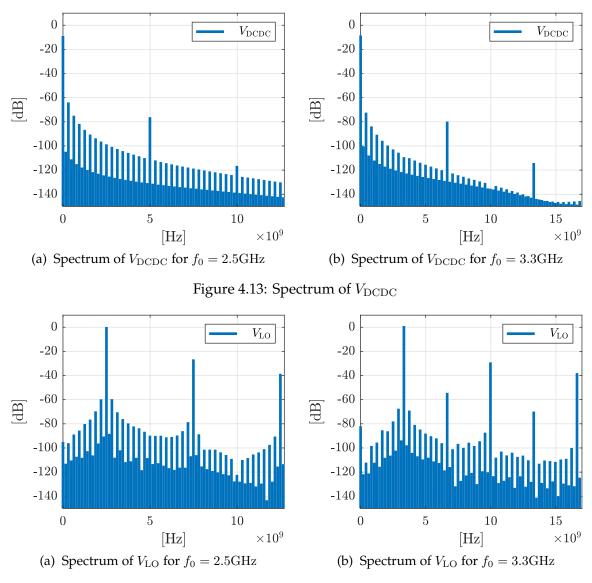

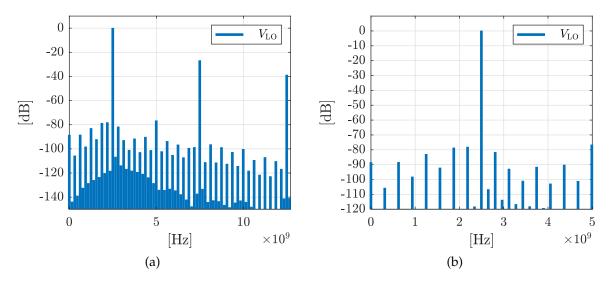

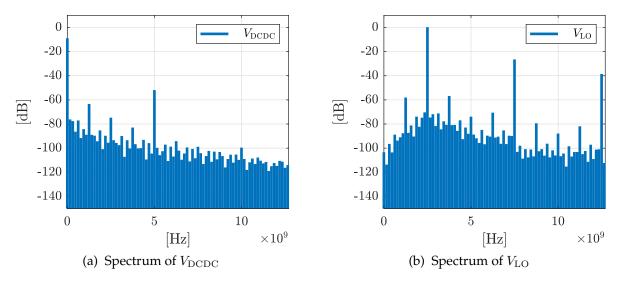

| Spectrum of $V_{\text{DCDC}}$                                                                                                  | 78                                |

| Spectrum of $V_{\rm LO}$                                                                                                       | 78                                |

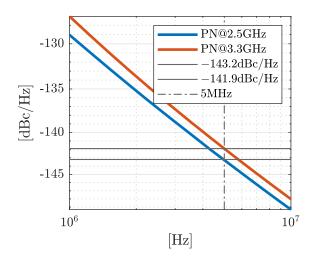

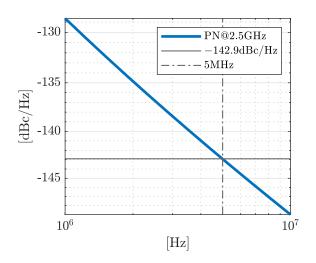

| PN of the SC powered Class-D VCO for $f_{\rm sw}=2.5{\rm GHz}$ and $f_{\rm sw}=3.3{\rm GHz}$ .                                 | 79                                |

| Comparison of $V_{\text{DCDC}}$ for different $f_0$ of the VCO $\ldots \ldots \ldots \ldots \ldots$                            | 79                                |

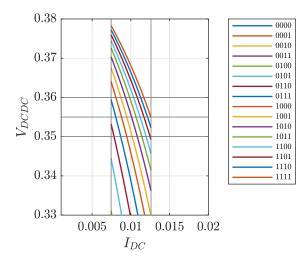

| Model of $V_{\text{DCDC}}$ based on the operating point of the VCO $\ldots \ldots \ldots$                                      | 80                                |

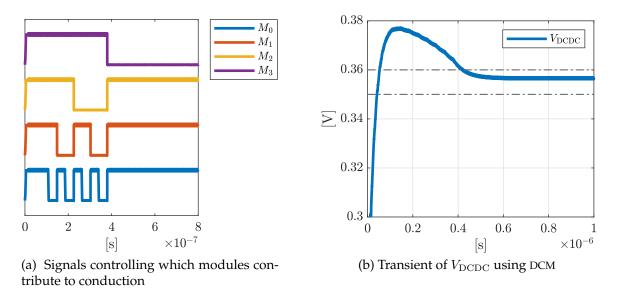

| Regulation of the output voltage with DCM                                                                                      | 81                                |

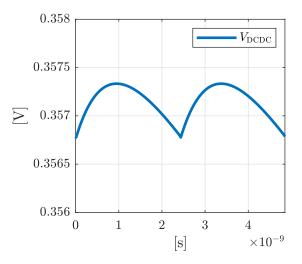

| $V_{ m DCDC}$ in a period $T_{ m sw}$ for a simulated converter employing DCM $\ldots$                                         | 81                                |

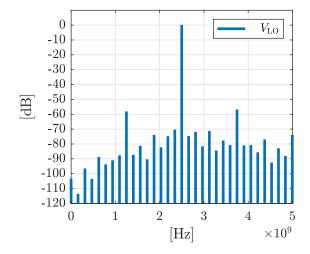

| Spectrum of $V_{\text{LO}}$ for $f_0 = 2.5 \text{GHz}$ with $C_{\text{out}} = 100 \text{nF}$                                   | 82                                |

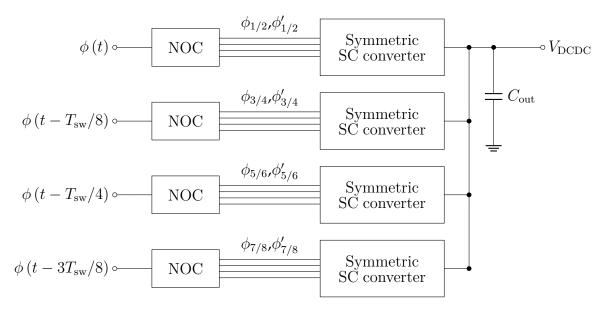

| Block diagram of the interleaved converter with $N = 4$                                                                        | 83                                |

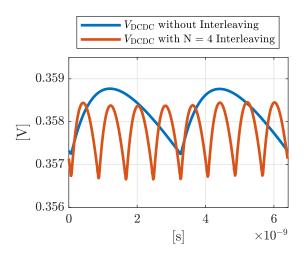

| Comparison of $V_{\text{DCDC}}$ between interleaved and non-interleaved designs .                                              | 84                                |

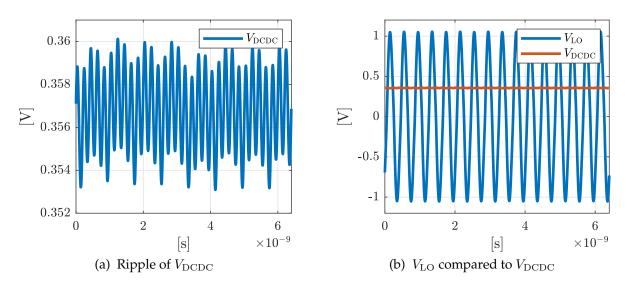

| $V_{ m DCDC}$ and $V_{ m LO}$ in a period for $f_0 = 2.5  m GHz$ with $C_{ m out} = 625  m pF$ and $N = 4$                     | 85                                |

| Spectrum of $V_{\text{LO}}$ and $V_{\text{DCDC}}$ for $f_0 = 2.5 \text{GHz}$ with $C_{\text{out}} = 625 \text{pF}$ and $N = 4$ | 85                                |

| Spectrum of $V_{\rm LO}$ zoomed around the carrier $\ldots \ldots \ldots \ldots \ldots \ldots$                                 | 86                                |

| PN for $f_0 = 2.5$ GHz with $C_{out} = 625$ pF and $N = 4$                                                                     | 86                                |

|                                                                                                                                | extremes for $V_{supply}$ = 350mV |

### Acronyms

- SoC System-on-Chip

- **VLSI** Very Large Scale Integration

- **VR** Voltage Regulators

- **RF** Radio Frequency

- **IF** Intermediate Frequency

- LO Local Oscillator

- LDO Low-Dropout Regulator

- sc Switched-Capacitor

- LTI Linear Time Invariant

- LTV Linear Time Variant

- **FSL** Fast Switching Limit

- SSL Slow Switching Limit

- **PSK** Phase Shift Keying

- **QAM** Quadrature Amplitude Modulation

- **PFM** Pulse-frequency Modulation

- SWM Switch Width Modulation

- **DCM** Digital Capacitance Modulation

- PN Phase Noise

- ISF Impulse Sensitivity Function

- FoM Figure of Merit

- **NOC** Non-Overlapping Clock

- **vco** Voltage Controlled Oscillator

# Introduction

In order to maximize the utilization of chip area and lower power consumption, the concept of System-on-Chip (SoC) has been introduced. The basic idea behind SoC is to integrate all the electronic components into a single chip. However, as different on-chip components require different voltages to operate, the role of voltage regulation becomes more important than ever in Very Large Scale Integration (VLSI). By tailoring the level of the supply voltage for the specific needs of each component we are in fact able to significantly diminish power dissipation in the system.

Although Voltage Regulators (VR) were traditionally realized as off-chip devices the requirements of nowadays complex integrated circuits, require the use of on-chip VR to be able to quickly adjust voltage during the operation of the circuit. Two different types of VR are mostly encountered in the recent literature: Switching VR and linear VR. Switching VR offer the highest efficiency, while linear VR are free from any switching noise, possesses ripple rejection capacity, low voltage noise, fast response time and smaller area overhead, but their efficiency is lower compared to that of switching VR.

In this work we focus on the power management of a particular Radio Frequency (RF) building block: the Local Oscillator (LO). We note however that most of the components present in a RF system are supply-sensitive blocks and the LO is no exception. This means that the LO may show an unwanted behaviour if there are disturbances in the power supply. Generally speaking, a cascade of switching and linear regulators is commonly used to drive an oscillator. In this scheme, showed in Figure 1, the switching VR initially converts the supply voltage in an efficient way and then, in order to guarantee the best performance for the LO, linear VR are often used, in the form of a low-noise Low-Dropout Regulator (LDO), to generate a "clean" supply for the oscillator.

Figure 1: Power supply scheme for a conventional oscillator

Low noise LDOs however come at the cost of an additional quiescent current, which impacts the system power efficiency significantly. To improve the efficiency of the circuit one idea is to try and remove the low-noise LDO and to power the LO directly with a switching voltage regulator.[1, 12]

In this thesis we are therefore going to analyse the problem of realizing an oscillator directly powered by a switching voltage regulator. The switching regulator has to be designed in a way that doesn't interfere with the performance of the oscillator. Moreover, to save chip area, the regulator may use as its clock signal the output of the oscillator divided by an appropriate frequency divider. The equivalent block scheme of this circuit is shown in Figure 2. The final aim of this thesis is to understand if it is possible to realize such a circuit and whether or not it is possible to integrate all of its components. The oscillator topology that is going to be used in this thesis is that of a Class-D oscillator, which requires low supply voltage values in order to perform at its best. A Switched-Capacitor DC-DC converter is therefore employed to step down the supply voltage and directly power the oscillator.

Figure 2: Power supply scheme for the oscillator in our thesis

The thesis is organized as follows. In chapter one the working principles of an RF oscillator and the design challenges that it involves are presented. In chapter two the Class-D oscillator is analysed in order to understand why this particular topology is so attractive. In chapter three a deep review of the design of Switched-Capacitor (SC) converters is carried out with specific considerations stemming from our particular design case. In chapter four a design prototype, first employing an off-chip capacitor for filtering the supply disturbances, is designed and its simulated performance is presented. Finally in the same chapter a second prototype is developed, this time using an on-chip capacitor, and the results that have been obtained are showed as well.

# CHAPTER 1

## LC Harmonic Oscillators Theory

In this chapter an introductory summary of the working principles of LC harmonic oscillators is made. We start from theoretical notes on how oscillation is achieved, first from a feedback theory standpoint and then in a more qualitative way. We proceed by analysing the building blocks that are necessary to realize an oscillator. Additionally, design problems such as phase noise and frequency pushing are analysed in this chapter in order to get a better insight on how oscillator design works.

#### 1.1 Feedback Theory Analysis

An oscillator is an autonomous system capable of continuously generating a periodic output signal at a frequency of oscillation  $\omega_0$ . Oscillators in electronics are divided into 2 types: harmonic oscillators, which produce a sinusoidal (or mostly sinusoidal) output signal, and relaxation oscillators which produce a non-sinusoidal input. For RF applications, relaxation oscillators are rarely used in high-performance transceivers because they generate signals of inadequate spectral purity[8], that is why in this work we are going to focus only on harmonic oscillators.

Oscillators in order to function must have a self-sustaining mechanism that allows its own noise to grow and eventually become a periodic signal[13]. This behaviour can be studied by means of feedback theory by representing the oscillator as in Figure 1.1, where  $V_{in} = 0$  being the oscillator an autonomous system. Note however that  $V_{in}$  could also be viewed as the noise of the oscillator itself.

Figure 1.1: General model of a feedback system

For simplicity we can represent the transfer function of the system in Figure 1.1 as:

$$\frac{Y(s)}{X(s)} = \frac{H(t)}{1 + \beta(s)H(s)} = \frac{K}{(s - p_1)(s - p_2)}$$

(1.1)

Then since the oscillator is an autonomous system and  $V_{in} = 0$  we have that the natural response of the system is:

$$v_{\text{out}}(t) = a_1 e^{p_1 t} + a_1 e^{p_2 t} \tag{1.2}$$

where  $a_1$  and  $a_2$  are the initial condition of the system. In order to observe oscillation at the frequency  $\omega_0$ , the system must have in its root locus conjugate imaginary poles positioned at  $p_{1,2} = \sigma \pm j\omega_0$ , with  $\sigma \ge 0$ . If these conditions are realized the natural response of the system, assuming  $a_1 = a_2^*$ , can be rewritten as:

$$v_{\rm out}(t) = 2|a_1|e^{\sigma t}\cos(\omega_0 t + \underline{a_1})$$

(1.3)

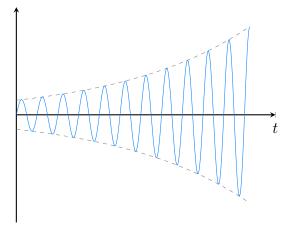

The time evolution of  $v_{out}(t)$  has been plotted in Figure 1.2 and we can clearly see how the amplitude of oscillation exponentially increases, while oscillating at  $\omega_0$ . Note however that in real circuits, due to various non-linear effects, the amplitude of oscillation eventually reaches a steady state value and ceases to increase.

Alternatively, the requirements for a system to oscillate at  $\omega_0$ , can also be formulated mathematically in the form of the "Barkhausen Criteria". Assuming that in Figure 1.1 the feedback network is such that  $\beta(s) = 1$ , then the Barkhausen Criteria are as follows:

$$|H(j\omega_0)| = 1 \tag{1.4}$$

$$/H(j\omega_0) = 180^{\circ} \tag{1.5}$$

Figure 1.2: Response of an unstable system oscillating at  $\omega_0$

When referring to Figure 1.1, the conditions described by Equation 1.4 and Equation 1.5 mean that any noise signal  $V_n$  at  $\omega_0$  present on  $V_{in}$  will generate a signal  $V_{fb} = -V_n$  which will the add up with  $V_{in} = V_n$ , causing  $\epsilon$  to increase and creating a positive feedback loop that eventually will build into an oscillation at  $\omega_0$ .

#### 1.2 Negative Resistance Method

Another more intuitive way to understand the behaviour of a harmonic oscillator comes from modelling it as a combination of a lossy resonator (a circuit having resonant behaviour) and an active circuit that cancels the loss. Resonators can be realized by using quarter-wave pieces of transmission line or even quartz crystals, but the most common way to realize a resonator is by the means of a RLC tank, which is the implementation used by the oscillators presented in this work. To better understand this concept, an equivalent model of an ideal lossless LC tank is first shown in Figure 1.3.

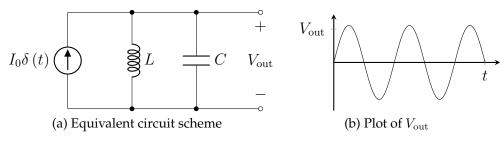

Figure 1.3: Lossless *LC* tank

If we apply a current impulse,  $I_0\delta(t)$ , to the lossless tank of Figure 1.3 the impulse is entirely absorbed by C, generating a voltage of  $I_0/C$ . The charge on C then begins to flow through L, and the output voltage falls. When  $V_{\text{out}}$  reaches zero, C carries no energy, but L has a current equal to  $L\frac{dV_{\text{out}}}{dt}$ , which charges C in the opposite direction, driving  $V_{\text{out}}$  toward its negative peak. This periodic exchange of energy between C and L continues indefinitely, with an amplitude given by the strength of the initial impulse.

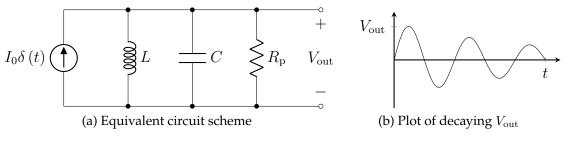

Considering now the model of a real lossy RLC tank, shown in Figure 1.4, we have that such a circuit behaves similarly, except that the resistance  $R_p$  consumes some of the capacitor energy in every cycle, causing an exponential decay in the amplitude.

Figure 1.4: Lossy RLC tank

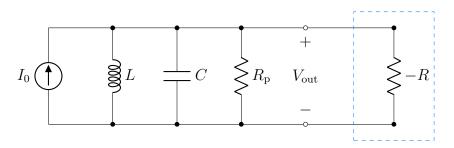

As anticipated, by combining a lossy RLC tank with an active element that realizes a "negative resistance" -R we are capable of restoring the loss caused by  $R_p$  and have the circuit continuously oscillate as in Figure 1.3b. The equivalent model of a harmonic oscillator realized in this way is shown in Figure 1.5.

Figure 1.5: Harmonic *RLC* oscillator

By writing the transfer function of the system from the input current  $I_0$  to the output voltage  $V_{out}$ , which corresponds to the impedance of the equivalent circuit, we get the following expression:

$$Z_{0} = \frac{V_{\text{out}}}{I_{0}} = \left(\frac{1}{sL} + sC + \frac{1}{R_{\text{p}}} - \frac{1}{R}\right)^{-1} = \frac{sLR_{\text{p}}R}{s^{2}LCR_{\text{p}}R + sL\left(R - R_{\text{p}}\right) + RR_{\text{p}}}$$

(1.6)

If we impose in Equation 1.6 the condition  $R \ge R_p$  we have that the transfer function becomes that of an unstable system having conjugate imaginary poles placed at  $p_{1,2} = \sigma \pm j\omega_0$  with  $\sigma \ge 0$ . This means that the equivalent circuit of Figure 1.5 correctly realizes a harmonic oscillator of oscillating frequency  $\omega_0 = 1/\sqrt{LC}$ .

#### 1.3 The Cross-Coupled Pair

Now that we have understood the basic principles behind the behaviour of LC harmonic oscillators, we are going to briefly touch on how to realize the active circuit that allow us to implement a negative resistance. The most popular solution to implement a negative resistance is by the means of the so called "cross-coupled pair" which is depicted in Figure 1.6.

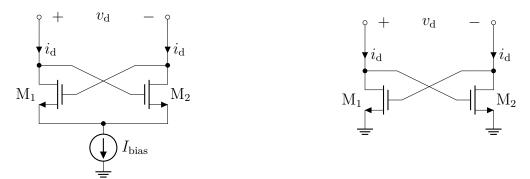

(a) Cross-coupled pair with current tail generator

(b) Cross-coupled pair with no current tail generator

Figure 1.6: Cross-coupled pair

This topology owes its name to the particular way in which the two mosfets  $M_1$  and  $M_2$  are connected. Note that the current source  $I_{\text{bias}}$ , shown in Figure 1.6a, is inserted to correctly bias the pair. Cross-coupled oscillators realized in this way take the name of "tail-biased oscillators". However, as we will see later, there exist other oscillator topologies, such as Class-D oscillators, which don't make use of this biasing current and have the cross-coupled pair realized as in Figure 1.6b.

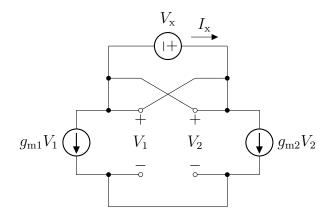

We focus now on the equivalent small signal scheme of the cross-coupled pair of Figure 1.6a which is shown in Figure 1.7.

Figure 1.7: Equivalent small signal scheme of a cross-coupled pair

We want to prove that by looking inside the terminals of the crossed-coupled pair we see a negative resistance. Note that in order to simplify the calculations we assume that the small-signal resistance  $r_0$  can be neglected ( $r_0 \gg 1/g_m$ ) and we don't take into account the parasitic capacitances of the transistors. We have that:

$$I_{\rm x} = -g_{\rm m1}V_1 = -g_{\rm m2}V_2 \tag{1.7}$$

and since  $V_x = V_1 - V_2$  we can write:

$$\frac{V_{\rm x}}{I_{\rm x}} = -\left(\frac{1}{g_{\rm m1}} + \frac{1}{g_{\rm m2}}\right) \tag{1.8}$$

which, by imposing  $g_m = g_{m1} = g_{m2}$  can be reduced to:

$$\frac{V_{\rm x}}{I_{\rm x}} = -\frac{2}{g_{\rm m}} \tag{1.9}$$

which clearly shows that the resistance of the crossed-coupled pair is negative.

#### 1.4 Class-B Oscillators

We now have all the elements to understand the working principles behind the behaviour of *LC* harmonic oscillators. If we combine the cross-coupled pair of Figure 1.6a with a *RLC* resonator, such as the one in Figure 1.4, we end up with the very popular topology of a Class-B oscillator, which is depicted in Figure 1.8:

Figure 1.8: Class-B oscillator

If the negative resistance, provided by the cross-coupled pair as in Equation 1.9, is sufficient to cancel the loss due to the resistance of the tank we have that oscillation in the Class-B oscillator starts up. The oscillation frequency for a Class-B oscillator is of:

$$f_0 = \frac{\omega_0}{2\pi} = \frac{1}{2\pi} \sqrt{\frac{1}{LC}}$$

(1.10)

The amplitude of oscillation  $\hat{V}_{\rm LO}$  of the differential signal between nodes  $V_{\rm LO_+}$  and  $V_{\rm LO_-}$  called  $V_{\rm LO}(t)$  increases as in Figure 1.2 and eventually reaches a steady state value instead of continuously growing. This is because as  $\hat{V}_{\rm LO}$  increases the switches of the cross-coupled pair start to operate in hard switching. As a result M<sub>1</sub> and M<sub>2</sub> continuously alternate between an OFF state, where they are not conducting, and an ON state, where they work in the triode region, causing a decrease in  $g_{\rm m}$  that leads  $\hat{V}_{\rm LO}$  to stop growing and reach steady state. An intrinsic consequence of hard switching is that when, for example, M<sub>1</sub> is in the ON state, M<sub>2</sub> is in the OFF state and vice versa. This aids our analysis aimed at understanding what is the steady state value of  $\hat{V}_{LO}$ . By considering only one of the transistors of the pair during a period of oscillation it's easy to see that the current  $I_{\rm M}$  absorbed by the transistor is square-wave like. Therefore, since we know the Fourier expansion for a square wave, we have that:

$$I_{\rm M} = \frac{I_{\rm bias}}{2} + \sum_{n=1,3,5,\dots}^{\infty} \frac{2I_{\rm bias}}{n\pi} \sin\left(2\pi f_0 \cdot n \cdot t\right)$$

(1.11)

Note how by summing  $I_{M1}$  and  $I_{M2}$  we get back the current  $I_{bias}$ .

We now take a look at the equivalent *AC* model of the oscillator shown in Figure 1.9.

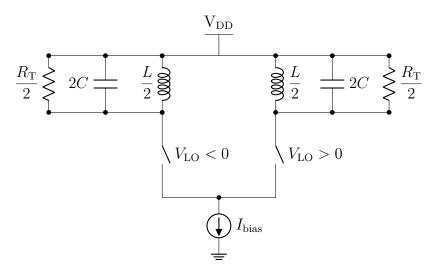

Figure 1.9: Equivalent circuit of a Class-B oscillator

We have that the tank has been divided into 2 separate portions where  $R_{\rm T}$  is the equivalent parallel resistance of the inductor parasitic resistance and it's equal to:

$$R_{\rm T} \simeq Q_{\rm L}^2 * R_{\rm L} \simeq Q_{\rm L} \omega_0 L_{\rm T} \tag{1.12}$$

The impedance of one of the portions of the tank at the resonance frequency is:

$$Z_{\rm T}(\omega_0) = 2C / \frac{L}{2} / \frac{R_{\rm T}}{2} = \frac{R_{\rm T}}{2}$$

(1.13)

while for other frequencies multiple of  $\omega_0$  we have that  $Z_T(\omega) \simeq 0$ . From Equation 1.11 we can then calculate the current in the tank for  $\omega_0$ :

$$I_1 = \frac{2}{\pi} I_{\text{bias}} \tag{1.14}$$

Putting all equations together, the voltage on nodes  $V_{LO_+}$  and  $V_{LO_-}$  is given by:

$$V_{\rm LO_{+}}(t) = V_{\rm DD} + \frac{R_{\rm T}}{2} I_1 \sin(\omega_0 t) = V_{\rm DD} + \frac{2}{\pi} I_{\rm bias} \frac{R_{\rm T}}{2} \sin(\omega_0 t)$$

(1.15)

$$V_{\rm LO_{-}}(t) = V_{\rm DD} - \frac{R_{\rm T}}{2} I_1 \sin(\omega_0 t) = V_{\rm DD} - \frac{2}{\pi} I_{\rm bias} \frac{R_{\rm T}}{2} \sin(\omega_0 t)$$

(1.16)

Therefore we have a formula for the oscillation amplitude of the Class-D oscillator:

$$\hat{V}_{\rm LO} = \frac{2}{\pi} R_{\rm T} I_{\rm bias} \tag{1.17}$$

#### 1.4.1 Voltage and Current Limited Regime

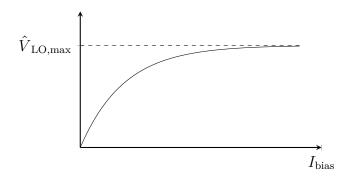

As a result of Equation 1.17 the oscillation amplitude of the Class-B oscillator  $\hat{V}_{\rm LO}$  depends on the value of  $I_{\rm bias}$ . This means that if we are interested in increasing  $\hat{V}_{\rm LO}$  we can do so by raising the value of  $I_{\rm bias}$  at the obvious cost of more power consumption. However there comes a point in the operation of the Class-B oscillator where  $\hat{V}_{\rm LO}$  saturates to  $\hat{V}_{\rm LO} = V_{\rm DD} - V_{\rm S}$ , with  $V_{\rm S}$  the voltage on the source terminal of the switches, and no longer increases as  $I_{\rm bias}$  does. The only way to increase  $\hat{V}_{\rm LO}$  then is by raising  $V_{\rm DD}$ . The oscillator therefore based on the values of  $I_{\rm bias}$  and  $V_{\rm DD}$  moves between two different regimes. In the "current limited regime"  $\hat{V}_{\rm LO}$  is proportional to  $I_{\rm bias}$  as we have come to expect. On the other hand, in the "voltage limited regime"  $\hat{V}_{\rm LO}$  is proportional to  $I_{\rm bias}$  has no effect on  $\hat{V}_{\rm LO}$ . This behaviour is shown in Figure 1.10.

Figure 1.10:  $\hat{V}_{LO}$  as a function of  $I_{\text{bias}}$

Note that, as we have anticipated, Class-D oscillators don't include a tail generator in their cross-coupled pair that limits the absorbed current to a value  $I_{\text{bias}}$ . Therefore we can expect the Class-D oscillator to operate in the "voltage limited regime" and have their oscillation amplitude depend only on  $V_{\text{DD}}$ .

#### 1.5 Phase Noise

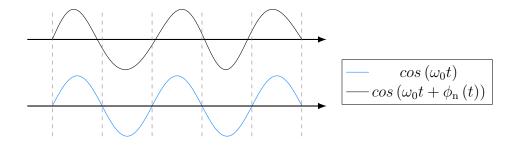

An ideal oscillator, as explained in Section 1.1, is capable of continuously generating a periodic output signal at a frequency of oscillation  $\omega_0$ . This signal, in the ideal case, can be written as  $x(t) = \cos(\omega_0 t)$  and is such that its zero crossing occurs at exact integer multiples of  $T = 2\pi/\omega_0$ . In reality however the noise of the oscillator randomly perturbs the zero crossing. To model this behaviour we rewrite x(t) as:

$$x(t) = \cos\left(\omega_0 t + \phi_n(t)\right) \tag{1.18}$$

where the term  $\phi_n(t)$  is a small random phase quantity that deviates the zero crossing from the integer multiples of *T* and it's what we call Phase Noise (PN). An example of this effect in the time domain, although greatly exaggerated, is shown in Figure 1.11.

Figure 1.11: Output waveforms for an ideal and a noisy oscillator

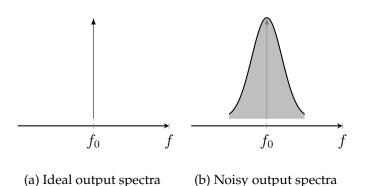

The perturbations of the zero crossing of the waveform, given by phase noise, have another effect that can be appreciated by looking at the waveform in the frequency domain. We know that frequency can be expressed as  $f_0 = 1/T$ . However by considering a noisy oscillator the value of *T* is no longer fixed, as now *T* randomly fluctuates due to  $\phi_n$ . This leads the frequency of the waveform to fluctuate as well. By looking at the spectrum of the output waveform of a noisy oscillator, instead of observing a pure impulse centered at  $f_0$ , as we would expect from a sinusoidal source, we will see that the spectrum has "broadened". The difference between these spectra is illustrated in Figure 1.12.

Figure 1.12: Comparison between ideal and noisy spectra of an oscillator

This behaviour can be formulated mathematically by rewriting the time-domain expression in the following way:

$$x(t) = A\cos\left(\omega_0 \cdot t + \phi_n(t)\right) \tag{1.19}$$

$$\simeq A\cos\left(\omega_{0} \cdot t\right) - A\sin\left(\omega_{0}t\right)\sin\left(\phi_{n}\left(t\right)\right)$$

(1.20)

$$\simeq A\cos\left(\omega_{0} \cdot t\right) - A\phi_{n}\left(t\right)\sin\left(\omega_{0}t\right)$$

(1.21)

Then since  $X(\omega) := \mathcal{F}[x(t)]$  and  $\Phi_n(\omega) := \mathcal{F}[\phi_n(t)]$ , by applying some simple signals theory for  $\omega > 0$  we get the following spectrum:

$$X(\omega) = \frac{A}{2} \cdot \left(\delta\left(\omega + \omega_0\right) + \Phi_n\left(\omega + \omega_0\right)\right)$$

(1.22)

We have that Equation 1.22, as expected, shows that the spectrum of x(t) is composed of an impulse centered in  $\omega_0$  and of the spectrum of  $\phi_n(t)$  translated to the center frequency  $\omega_0$ . The composition of  $\Phi_n(\omega)$  is going to be analysed later, but for now it's important to note that  $\Phi_n(\omega)$  decreases as we move away from  $\omega_0$ .

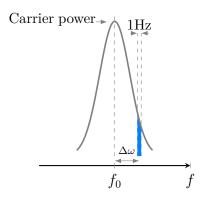

Figure 1.13: Specification of phase noise

Phase noise is thus measured with respect to a certain "frequency offset"  $\Delta \omega$  from the carrier. Referencing Figure 1.13, we have that PN is defined by first considering a 1Hz bandwidth of the noise spectrum at an offset  $\Delta \omega$  from the carrier, then measuring the power in this bandwidth and finally normalizing the result to the "carrier power" which can be viewed as the peak of the spectrum. The unit used to measure PN is called dBc/Hz which stands for "dB with respect to the carrier" reflecting on this procedure.

#### 1.5.1 Phase Noise in Oscillators - LTI Approach

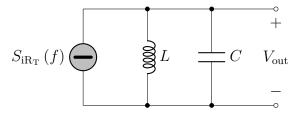

Let's consider the equivalent *RLC* model of a harmonic oscillator under Linear Time Invariant (LTI) conditions, as the one depicted in Figure 1.4. We model the noise current in the tank as a white thermal source  $S_{iR_T}(f)$  given by the tank resistance  $R_T$ , with mean squared spectral density of:

$$S_{\mathrm{iR}_{\mathrm{T}}}(f) = \frac{\overline{i_{\mathrm{n}}^{2}}}{\Delta f} = \frac{4k_{\mathrm{B}}T}{R_{\mathrm{T}}}$$

(1.23)

with  $k_{\rm B}$  the Boltzmann constant and T the temperature. In order to carry out our analysis, we assume that the negative resistance -R, perfectly compensates, at steady state, the losses given by the tank resistance  $R_{\rm T}$ , but not its noise as seen in Figure 1.14

Figure 1.14: Equivalent circuit of a noisy harmonic RLC oscillator

For  $\Delta \omega \ll \omega_0$  the impedance of the LC tank of Figure 1.14 may be approximated as:

$$Z\left(\omega_{\rm o} + \Delta\omega\right) \simeq -j \cdot \frac{\omega_{\rm o}L}{2\frac{\Delta\omega}{\omega_{\rm 0}}} \tag{1.24}$$

which can be rewritten, by considering  $L = R_T / (\omega_0 Q)$  where Q is the quality factor of the unloaded tank, as follows:

$$|Z\left(\omega_{\rm o}+\Delta\omega\right)| \simeq \frac{\omega_{\rm 0}R_{\rm T}}{2Q\Delta_{\omega}} \tag{1.25}$$

In this way we emphasize the dependence of  $|Z(\omega_o + \Delta \omega)|$  from Q and  $R_T$  as opposed to L. Next, we calculate the spectral density of the mean square noise voltage:

$$S_{\rm v_n}(f) = \frac{\overline{v_n^2}}{\Delta f} = |Z|^2 \cdot \frac{\overline{i_n^2}}{\Delta f} = 4k_{\rm B}TR_{\rm T} \left(\frac{\omega_0}{2Q\Delta\omega}\right)^2$$

(1.26)

We note that  $S_{v_n}(f) \propto^{-1} \Delta \omega^2$  due to the filtering action of the tank. This  $1/f^2$  behaviour simply reflects the fact that the voltage frequency response of an *RLC* tank rolls off as 1/f to either side of the center frequency and power is proportional to the square of voltage. Moreover we notice that by increasing Q the value of  $S_{v_n}(f)$  decreases while keeping all the other parameters constant, underlining the importance of employing a good resonator to realize an oscillator.

To proceed with our analysis we have to consider that  $S_{v_n}(f)$  introduces both amplitude noise and PN, however we have seen that the amplitude of oscillation  $\hat{V}_{LO}$  has a self-limiting effect and eventually reaches a steady state value. This leads us to consider that only half of  $S_{v_n}(f)$  contributes to PN. Referencing the previous notation we therefore have that  $\Phi_n(f) = S_{v_n}(f)/2$ . We can then derive the expression of PN as seen in Section 1.5. By normalizing  $S_{v_n}(f)/2$  to the mean square carrier voltage  $P_{LO} = \hat{V}_{LO}^2/2$  and report the ratio in decibels, obtaining the normalized single-sideband noise spectral density, which is what we call PN and is expressed in dBc/Hz:

$$\mathcal{L}(\Delta\omega) = 10\log_{10} \left[ \frac{4k_{\rm B}TR_{\rm T}}{2} \cdot \frac{1}{P_{\rm LO}} \cdot \left(\frac{\omega_0}{2Q\Delta\omega}\right)^2 \right] = 10\log_{10} \left[ \frac{4k_{\rm B}TR_{\rm T}}{\hat{V}_{\rm LO}^2} \cdot \left(\frac{\omega_0}{2Q\Delta\omega}\right)^2 \right]$$

$$= 10\log_{10} \left[ \frac{k_{\rm B}T}{\hat{V}_{\rm LO}^2} \cdot \frac{R_{\rm T}}{Q^2} \left(\frac{\omega_0}{\Delta\omega}\right)^2 \right]$$

(1.27)

From this expression we immediately notice how PN improves as both  $P_{\text{LO}}$  and Q increase. This result is consistent with what we expect, increasing  $P_{\text{LO}}$  improves PN because the thermal noise is fixed, while increasing Q improves PN quadratically because the tank's impedance falls off as  $1/(Q\Delta\omega)$ .

However due to the many simplifying assumptions that we have made in order to obtain Equation 1.27, the accuracy of the formula that we have found, unsurprisingly, shows some discrepancies when compared with a real oscillator spectra.

First, while in real spectra there exist a region where the spectral density is proportional to  $1/(\Delta \omega)^2$  the magnitudes are typically quite a bit larger than predicted. This is because there are additional noise sources besides the tank's losses, such as the transistors that realize the cross coupled pair, which contribute to PN. Moreover a real measured spectra eventually stops decreasing as it flattens out hitting what it's called a "noise floor". Finally there is almost always a  $1/(\Delta \omega)^3$  region for small values of  $\Delta \omega$ . This region is given by another noise source, that we have neglected until now, called "flicker noise". Contrary to thermal noise which has its PSD constant over the entire frequency range, the PSD of flicker noise is such that  $S_{i,flicker} \propto^{-1} \omega$ . Therefore since noise gets "multiplied" by a factor  $1/f^2$  when becoming phase noise, flicker noise originates a  $1/f^3$  region in the phase noise.

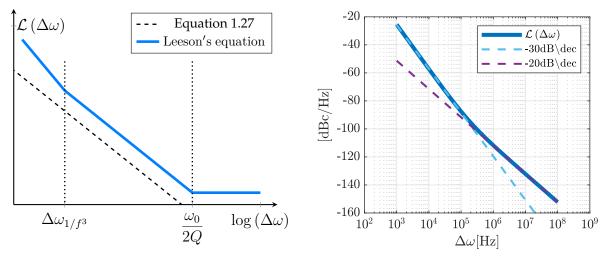

In order to take into account these effects we have to modify Equation 1.27 obtaining what is generally referred to as "Leeson's equation":

$$\mathcal{L}(\Delta\omega) = 10\log_{10}\left[\frac{2Fk_{\rm B}T}{P_{\rm LO}}\left\{1 + \left(\frac{\omega_0}{2Q\Delta\omega}\right)^2\right\}\left\{1 + \frac{\Delta\omega_{1/f^3}}{|\Delta\omega|}\right\}\right]$$

(1.28)

The modification of Equation 1.27 made by Leeson, consist in the addition of a factor F to account for the increased noise in the  $1/(\Delta \omega)^2$  region, an addictive factor of 1 (inside the braces) to model the noise floor and finally a multiplicative factor (inside the second set of braces) to provide a  $1/(\Delta \omega)^3$  behaviour at small offset frequencies. In Figure 1.15a we plot the PN given by Equation 1.28 and compare it with the model given by Equation 1.27, while in Figure 1.15b the phase noise of a simulated Class-B oscillator is shown, as an example, to better understand the phase noise behaviour in the  $1/f^3$  region.

(a) Comparison of Leeson's equation with simplified (model

(b) Phase noise of a simulated Class-B oscillator

Figure 1.15: Phase noise behaviour of a real oscillator

We note however how the parameter F is an empirical fitting parameter and the same could be said for  $1/(\Delta \omega)^3$  meaning that they must be obtained from measurements, diminishing the predictive power of Equation 1.28. The model also predicts that the frequency at which the  $1/f^2$  and  $1/f^3$  regions in the phase noise meet, called the " $1/f^3$  corner frequency", is the same at which the thermal and flicker noise PSD are equal, which is respectively called the "1/f corner frequency" This behaviour however is generally hardly observed in practical measurements. The frequency at which the noise floor should start is also not always well predicted by the model. In order to solve these issues a new model has to been developed and it's going to be explained in the next subsection.

#### 1.5.2 Phase Noise in Oscillators - LTV Approach

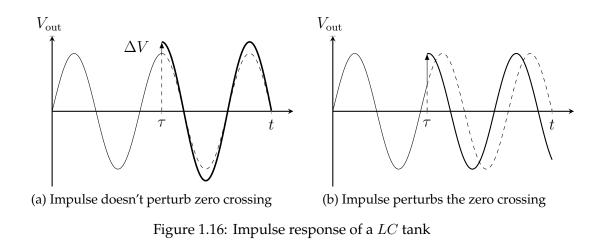

To improve upon the evident limits of the Leeson model, Hajmiri and Lee [8] formulated a new theory regarding phase noise by modelling the oscillator as a Linear Time Variant (LTV) system. In order to show that an oscillator is indeed a time variant system we take, as an example, the same ideal LC tank of Figure 1.3a, which has been oscillating with a constant amplitude just like Figure 1.3b for an indefinite amount of time, given the lack of a resistance  $R_{\rm T}$  that consumes the energy of the tank. If we apply an impulse at different time instants, we are able to see that the system reacts differently based on when the impulse was applied.

With respect to the waveform shown in Figure 1.16a, we consider the case where the time instant, in which the impulse is injected into the oscillator, coincides with a voltage maximum of the oscillator output waveform. This leads to a temporary increase in the oscillation amplitude by an amount  $\Delta V$ , but because the response to the impulse superimposes exactly in phase with the pre-existing oscillation the timing of the zero crossing does not change. In contrast an impulse injected at some other time as shown in Figure 1.16b generally effects the timing of the zero crossing. Since, as already discussed, we can consider the timing of the zero crossing as a measure of phase, we clearly see that the effect of the impulse changes based on when the injection occurs in time. The principle of time-invariance for oscillators therefore fails to hold and we have to treat them as LTV systems.

The impulse response of the oscillator, going forward, has to be formulated in its LTV form, which is given by:

$$h_{\phi}(t,\tau) = \frac{\Gamma(\omega_0\tau)}{q_{\max}}u(t-\tau)$$

(1.29)

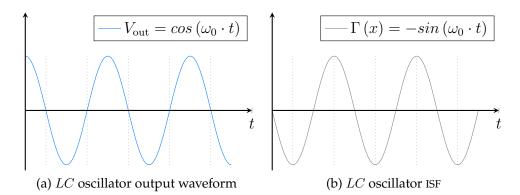

where u(t) is the unit step function. The function  $\Gamma(x)$  is normalized by  $q_{\text{max}}$  which corresponds to the maximum charge displacement in the capacitors.  $\Gamma(x)$  is called the Impulse Sensitivity Function (ISF), which is a dimensionless, frequency and amplitude independent function periodic in  $2\pi$ . The ISF encodes information about the sensitivity of the oscillator to an impulse injected at phase  $\omega_0 t$ . An example of the ISF for a *LC* harmonic oscillator is shown in Figure 1.17 where we can appreciate how  $\Gamma(x) = 0$  for the time instants where  $V_{\text{out}}$  is at its maximum, meaning that no phase perturbation can be applied to the system, which is consistent with the example of Figure 1.16.

Figure 1.17: Comparison between ISF and output waveform of an oscillator

While its most practical to determine the ISF through simulation, there are also analytical methods that apply in certain scenarios. In any case once the ISF has been determined, we can compute the excess phase due to an arbitrary noise signal, through use of the superposition integral, as follows:

$$\phi(t) = \int_{-\infty}^{\infty} h_{\phi}(t,\tau) i(\tau) d\tau = \frac{1}{q_{\max}} \int_{-\infty}^{t} \Gamma(\omega_{0}\tau) i(\tau) d\tau$$

(1.30)

where  $\phi$  is the phase noise term seen in Equation 1.18. We can rewrite Equation 1.30, by rewriting the ISF as its Fourier series:

$$\Gamma\left(\omega_{0}\tau\right) = \frac{c_{0}}{2} + \sum_{n=1}^{\infty} c_{n} \cos\left(n\omega_{0}\tau + \theta_{n}\right)$$

(1.31)

where the  $c_n$  coefficients are real and  $\theta_n$  is the phase of the n-th harmonic of the ISF. Note however that we assume the noise components as uncorrelated so their relative phase  $\theta_n$  in irrelevant. Putting Equation 1.30 and Equation 1.31 together we get:

$$\phi(t) = \frac{1}{q_{\text{max}}} \left[ \frac{c_0}{2} \int_{-\infty}^t i(\tau) \, d\tau + \sum_{n=1}^\infty c_n \int_{-\infty}^t i(\tau) \cos\left(n\omega_0\tau\right) \, d\tau \right]$$

(1.32)

The physical meaning of Equation 1.32 can be understood by considering to inject in the system a sinusoidal current whose frequency is near an integer multiple m of the oscillation frequency, being:

$$i(t) = I_{\rm m} \cos\left[\left(m\omega_0 + \Delta\omega\right)t\right] \tag{1.33}$$

Assuming  $\Delta \omega \ll \omega_0$ , we can then plug Equation 1.33 into Equation 1.32 and obtain Equation 1.35.

$$\phi(t) = \frac{1}{q_{\text{max}}} \begin{bmatrix} \frac{c_0}{2} \int_{-\infty}^t I_{\text{m}} \cos\left[\left(m\omega_0 + \Delta\omega\right)\tau\right] d\tau \\ + \sum_{n=1}^{\infty} c_n \int_{-\infty}^t I_{\text{m}} \cos\left[\left(m\omega_0 + \Delta\omega\right)\tau\right] \cos\left(n\omega_0\tau\right) d\tau \end{bmatrix}$$

(1.34)

$$\phi(t) = \frac{1}{q_{\text{max}}} \begin{bmatrix} \frac{c_0}{2} \int_{-\infty}^t I_{\text{m}} \cos\left[\left(m\omega_0 + \Delta\omega\right)\tau\right] d\tau \\ + \sum_{n=1}^{\infty} \frac{c_n}{2} \int_{-\infty}^t I_{\text{m}} \cos\left[\left(\left(n - m\right)\omega_0 + \Delta\omega\right)\tau\right] d\tau \\ + \sum_{n=1}^{\infty} \frac{c_n}{2} \int_{-\infty}^t I_{\text{m}} \cos\left[\left(\left(n - m\right)\omega_0 + \Delta\omega\right)\tau\right] d\tau \end{bmatrix}$$

(1.35)

The only term of Equation 1.35 that provides a non negligible contribution is the one associate with n = m, therefore we can get the approximation:

$$\phi(t) \simeq \frac{I_{\rm m} c_{\rm m} \sin\left(\Delta\omega t\right)}{2q_{\rm max}\Delta\omega} \tag{1.36}$$

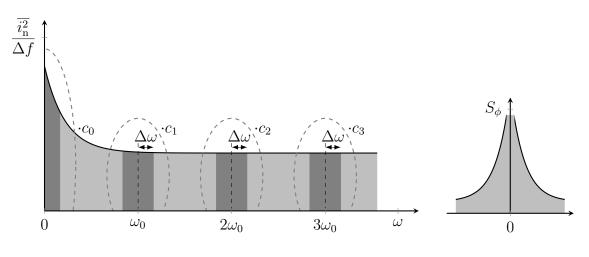

In a more general case however the spectrum of the noise is not given by a single sinusoidal tone, but it's a continuous spectra. Therefore what happens in reality is that  $\phi(t)$  is given by the summation of all the noise contributions located at distance  $\Delta \omega$  from the multiples of the oscillation frequency  $\omega_0$ . Note that the 1/f noise near DC gets upconverted, with relative weight given by the coefficient  $c_0$ , into  $1/f^3$  noise, while white noise near the higher carrier multiples, weighted by the coefficients  $c_{k\neq0}$ , undergoes downconversion turning into  $1/f^2$  noise. This process is shown in Figure 1.18 where the weighted noise contributions shown in Figure 1.18a all sum up following Equation 1.36 into  $\phi(t)$  which is shown in Figure 1.18b. Finally the summation of the various noise contributions all "fold" into noise near the carrier itself, following Equation 1.22.

(a) Noise contributions to phase noise

(b) Summation of noise contributions

Figure 1.18: Noise folding principle

Following these reasonings, in order to calculate the phase noise we start by considering that the value of  $\phi(t)$ , that we have calculated in Equation 1.36, translates following the mechanism of Equation 1.21 into two tones of the output spectrum of the oscillator symmetrically disposed from the carrier at distance  $\Delta \omega$  having power:

$$P_{\rm SBC}(\Delta\omega) \simeq 10 \log \left[\frac{I_{\rm k} c_{\rm k}}{4q_{\rm max}\Delta\omega}\right]^2 \tag{1.37}$$

Extending this formula for the case of a white source noise we get:

$$P_{\rm SBC}(\Delta\omega) \simeq 10 \log \left[ \frac{1}{4q_{\rm max}^2 \Delta\omega^2} \cdot \frac{\overline{i_{\rm n}^2}}{\Delta f} \cdot \sum_{k=0}^{\infty} c_k^2 \right]$$

(1.38)

which can used to derive the general expression of phase noise in the  $1/f^2$  region:

$$\mathcal{L}(\Delta\omega) \simeq 10 \log \left[ \frac{1}{2q_{\max}^2 \Delta\omega^2} \cdot \frac{\overline{i_n^2}}{\Delta f} \cdot \Gamma_{rms}^2 \right]$$

(1.39)

where Parseval's Theorem has been used to rewrite  $\sum_{k=0}^{\infty} c_k^2 = 2\Gamma_{rms}^2$ .

Finally by considering the ISF of a *LC* oscillator being  $\Gamma(x) = -\sin(x)$ , that  $q_{\text{max}} = C_{\text{T}}\hat{V}_{\text{LO}}$  with  $C_{\text{T}} = Q_{\text{T}}/(\omega_0 R_{\text{T}})$  and using Equation 1.23 we get:

$$\mathcal{L}(\Delta\omega) \simeq 10 \log \left[ \frac{1}{2q_{\max}^2 \Delta\omega^2} \cdot \frac{\overline{i_n^2}}{\Delta f} \cdot \Gamma_{rms}^2 \right]$$

(1.40)

$$= 10 \log \left[ \frac{1}{2C_{\rm T}^2 \hat{V}_{\rm LO}^2 \Delta \omega^2} \cdot \frac{4k_{\rm B}T}{R_{\rm T}} \cdot \frac{1}{2} \right]$$

(1.41)

$$= 10 \log \left[ \frac{1}{2\hat{V}_{\rm LO}^2 \Delta \omega^2} \cdot \frac{\omega_0^2 R_{\rm T}^2}{Q_{\rm T}^2} \cdot \frac{4k_{\rm B}T}{R_{\rm T}} \cdot \frac{1}{2} \right]$$

(1.42)

$$= 10 log \left[ \frac{k_{\rm B}T}{\hat{V}_{\rm LO}^2} \cdot \frac{R_{\rm T}}{Q_{\rm T}^2} \left( \frac{\omega_0}{\Delta \omega} \right)^2 \right]$$

(1.43)

which gives us back Equation 1.27. Moreover the " $1/f^3$  corner frequency" can be estimated using:

$$\Delta\omega_{1/f^3} = \omega_{1/f} \cdot \frac{c_0^2}{4\Gamma_{\rm rms}^2} = \omega_{1/f} \cdot \left(\frac{\Gamma_{\rm dc}}{\Gamma_{\rm rms}}\right)^2 \tag{1.44}$$

where the term  $\omega_{1/f}$  is the "1/*f* corner frequency". While in this thesis we are not interested in operation near the  $1/f^3$  corner frequency this once again proves the power of the LTV phase noise model.

#### 1.5.3 The Figure of Merit

Looking at the formula for phase noise derived in Equation 1.43 we notice how:

$$\mathcal{L}\left(\Delta\omega\right) \propto \left(\frac{\omega_0}{\Delta\omega}\right)^2 \tag{1.45}$$

Moreover we have that:

$$\mathcal{L}(\Delta\omega) \propto^{-1} \hat{V}_{\rm LO}^2 \propto I_{\rm bias}^2 \tag{1.46}$$

when we assume operation in the current limited regime. In order to compare different oscillator topologies, working at different oscillation frequencies and absorbing a different amount of power the Figure of Merit (FoM) is used and its defined as:

$$FOM = \mathcal{L}(\Delta\omega) - 20log_{10}\left(\frac{\omega_0}{\Delta\omega}\right) + 10log_{10}\left(\frac{P_{\rm DC}}{1\,{\rm mW}}\right) \ {\rm dBc/Hz}$$

(1.47)

where  $P_{\rm DC}$  is the DC power consumption of the oscillator.

#### 1.5.4 Effects of Phase Noise

We wish now to investigate what effects PN has on the correct operation of electronic circuits that include a noisy oscillator.

#### **Phase Noise in Receivers**

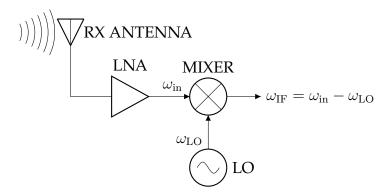

One effect of low phase noise can be observed in a receiver, where its equivalent scheme is shown in Figure 1.19.

Figure 1.19: Receiver scheme

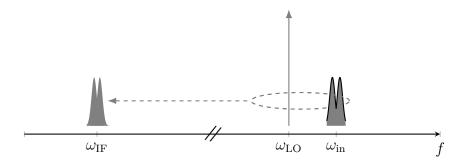

In the ideal case the signal produced by the LO is an impulse at  $\omega_{\rm LO}$  which when convolved through the mixer with the desired channel at  $\omega_{\rm in}$  yields an Intermediate Frequency (IF) signal at  $\omega_{\rm IF} = \omega_{\rm in} - \omega_{\rm LO}$  as shown in Figure 1.20.

Figure 1.20: Downconversion with an ideal LO

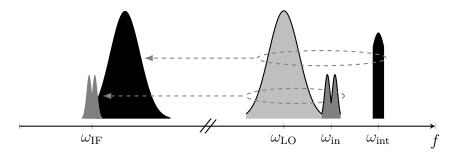

However if a noisy LO is used and the desired signal is accompanied by a large interferer at  $\omega_{int}$ . The convolution of the desired signal and the interferer with the noisy LO spectrum results in a broadened downconverted interferer which overwhelms the desired IF signal corrupting it, as shown in Figure 1.21. This phenomenon is called "reciprocal mixing".

Figure 1.21: Downconversion with a noisy LO

#### Phase Noise in Digital Modulation

There is however another more important effect that involves telecommunications systems employing digital modulations such as Phase Shift Keying (PSK), which in order to be understood requires a brief theoretical introduction regarding the problem of transmitting information and being able to correctly receive it.

Without loss of generality then we consider the problem of the transmission of a single isolated pulse associated to a symbol  $a_0$ .

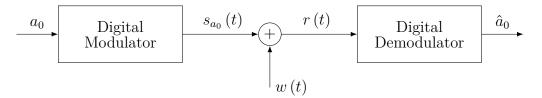

With reference to the system scheme shown in Figure 1.22 the transmission system aims to transfer the value of  $a_0$  to the receiver through the channel.

Figure 1.22: System model for digital transmission of an isolated pulse

In particular the digital modulator, defined by a given set of M real-valued waveforms  $s_n(t), n = 1, ..., M$ , selects the waveform to transmit in accordance with the value of  $a_0$ . This means that if the selected symbol value is  $a_0 = n$ , then the transmitted signal is  $s_{a0}(t) = s_n(t)$ . The selected signal  $s_n(t)$  is then transmitted through the channel, which for simplicity is assumed to have an ideal impulse response. Assuming that the waveform with index n is transmitted, which represents the symbol  $a_0 = n$ , the received, or observed, signal is given by:

$$r(t) = s_{n}(t) + w(t)$$

(1.48)

where w(t) models the noise introduced by the channel.

The receiver now, based on r(t), must decide which among the M hypothesis

$$H_{\rm n}: r(t) = s_{\rm n}(t) + w(t), \qquad n = 1, 2, ..., M$$

(1.49)

is the most likely, and correspondingly must select the detected value  $\hat{a}_0$ .

In order to proceed, it is convenient to represent the signals using vector notation. The received signal r(t) is therefore associated to a vector r of dimension I. Symbol detection is made by subdividing the space  $\mathbb{R}^{I}$  into M non overlapping regions  $R_{n}$  each one associated to one of the possible outcomes of  $a_{0}$ . The hypothesis  $H_{m}$  (and so  $\hat{a}_{0} = n$ ) is chosen if the received vector belongs to  $R_{m}$ , that is:

if

$$r \in R_{\rm m}$$

then choose  $H_{\rm m}$  and  $\hat{a}_0 = m$  (1.50)

This decision rule is realized by a block called "detector" which is part of the digital demodulator.

It is clear that the presence of a noise component w(t) could lead to errors in detection if the noise is so high that it moves a symbol  $a_0 = n$  associated to the region  $R_n$  to another region  $R_k$  with  $k \neq n$ .

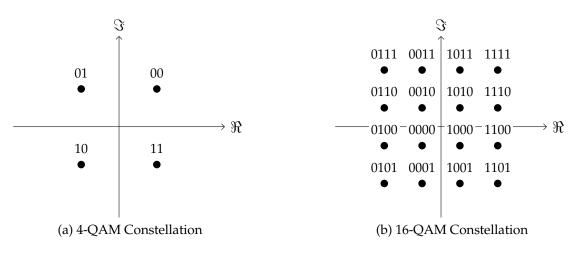

An example of a decision region for a Quadrature Amplitude Modulation (QAM) with M = 4 and M = 16 is shown in Figure 1.23. As can be appreciated, the detection of the symbol region in the M = 4 case can be implemented by checking the sign of the coordinates of r, while for the M = 16 case extra information regarding the modulus of the received vector is needed.

Figure 1.23: Examples of QAM constellations

We can now focus our attention on the PSK modulation in order to understand how also PN can lead to errors in symbol detection. We have that in PSK a generic signal waveform is given by:

$$s_{\rm n}\left(t\right) = h_{\rm tx}\left(t\right)\cos\left(2\pi f_0 + \varphi_{\rm n}\right) \tag{1.51}$$

$$\varphi_{n} = \frac{\pi}{M} (2n-1) + \varphi_{0} \qquad n = 1, 2, ..., M$$

(1.52)

where  $h_{tx}(t)$  is a real-valued finite-energy baseband pulse. This means that signals are obtained by choosing M possible values of the phase of a sinusoidal signal with frequency  $f_0$  modulated by  $h_{tx}$ .

An alternative way to write  $s_n(t)$  is given by:

$$s_{n}(t) = \cos(\varphi_{n}) h_{tx}(t) \cos(2\pi f_{0}) - \sin(\varphi_{n}) h_{tx}(t) \sin(2\pi f_{0})$$

$$(1.53)$$

It can be easily proved that  $s_n(t)$  can be written as the linear combination of the following two vectors:

$$\phi_1(t) = +\sqrt{\frac{2}{E_{\rm h}}} h_{\rm tx}(t) \cos(2\pi f_0)$$

(1.54)

$$\phi_2(t) = -\sqrt{\frac{2}{E_{\rm h}}} h_{\rm tx}(t) \sin(2\pi f_0) \tag{1.55}$$

which, with  $E_{\rm h}$  the energy of  $h_{\rm tx}(t)$ , constitute an orthonormal basis for I = 2. The vector coordinates of  $s_{\rm n}(t)$  are finally given by:

$$s_{\rm n} = \sqrt{\frac{2}{E_{\rm h}}} \left[ \cos\left(\varphi_{\rm n}\right), \sin\left(\varphi_{\rm n}\right) \right] \tag{1.56}$$

To obtain the vector coordinates in Equation 1.56 an oscillator provides a reference sinusoidal signal x(t) of frequency  $f_0$  plus a cosinusoidal signal realized by phase shifting by 90° the original signal x(t). In this way we are capable of realizing the basis of Equation 1.54 and Equation 1.55 and obtain  $s_n$ . However due to the oscillator PN, the coordinates of  $s_n$  are going to be affected by the noise.

Figure 1.24a show the decision region for a PSK modulation with M = 4 where PN is present, causing a "drift" of the received symbols along the constellation circumference. Therefore as PN increases, it's easy to see how it can lead to errors in detection by pushing the received symbols in the wrong region. This problem becomes even bigger if we increase the value of M, in order to be able to transmit more data, as shown in Figure 1.24b. This is the reason why over the years specification on PN have become more stringent to accommodate for modulations employing higher values of M. [2]

Figure 1.24: Examples of PSK constellations

# 1.6 Frequency Pushing

Thus far we have assumed, for simplicity, the value of the supply voltage to be constant. In practical implementations however the power supply will contain noise and, in some cases, even sinusoidal contributions at certain frequencies. The oscillating frequency of the oscillator is generally dependent from the value of the power supply, meaning that small changes in the value of  $V_{\text{DD}}$  will modulate the value of  $\omega_0$  changing it too. This behaviour is called "frequency pushing" and it can be quantified by the "supply pushing factor"  $K_V$ , which is specific for each different type of oscillator.  $K_V$  is normally measured in Hz/V, meaning that a variation of  $\Delta W$  on the power supply corresponds to a variation of the output frequency of  $\Delta \omega = 2\pi K_V \cdot \Delta V$ .

Sinusoidal ripple, present in the power supply, gets translated to spurious tones in the output spectrum of the oscillator, due to supply pushing. In order to prove this, we consider that the frequency modulation given by a ripple  $\Delta V_{\rm m} = V_{\rm m} cos (\omega_{\rm m} t)$  will be:

$$\Delta \omega = 2\pi K_{\rm V} \cdot V_{\rm m} \cos(\omega_{\rm m} t) \tag{1.57}$$

Then since phase is the integral of the angular frequency we get;

$$\phi\left(t\right) = \phi\left(0\right) + \int_{0}^{t} \omega\left(\tau\right) \, d\tau \tag{1.58}$$

$$\phi\left(t\right) = \frac{2\pi K_{\rm V}}{\omega_{\rm m}} V_{\rm m} \sin\left(\omega_{\rm m} t\right) \tag{1.59}$$

where we have assumed  $\phi(0) = 0$ .

By plugging Equation 1.59 into the usual Equation 1.21 we obtain the formula:

$$x(t) \simeq A\cos(\omega_0 t) - A\sin(\omega_0 t) \left(\frac{2\pi K_{\rm V}}{\omega_{\rm m}}\right) V_{\rm m} \sin(\omega_{\rm m} t)$$

(1.60)

By computing the Fourier transform of the second term for  $\omega > 0$  we get:

$$X_{\rm n}(\omega) = \frac{A}{4} \left(\frac{2\pi K_{\rm V}}{\omega_{\rm m}}\right) V_{\rm m} \left[\delta\left(\omega_0 + \omega_{\rm m}\right) + \delta\left(\omega_0 - \omega_{\rm m}\right)\right]$$

(1.61)

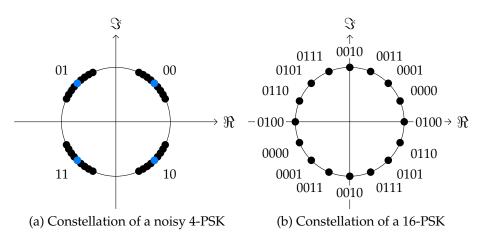

Which shows how as a result of frequency pushing two spurs at frequencies  $\omega_0 \pm \omega_m$  make an appearance in the output spectrum of the oscillator. These spurs have to kept under a certain level with respect to the carrier to avoid reciprocal mixing.

A spectrum example is shown in Figure 1.25:

Figure 1.25: Output spectrum of an oscillator with ripple on the power supply

The power of the spurs represented in dBc is given as:

$$S_{\rm spur} = 10 \log_{10} \left(\frac{2\pi K_{\rm V} V_{\rm m}}{2\omega_{\rm m}}\right)^2 dBc$$

(1.62)

Given the desired spur level the maximum ripple tolerated by the oscillator can be calculated by:

$$V_{\rm m} < \frac{2\omega_{\rm m}}{2\pi K_{\rm V}} 10^{(S_{\rm spur}/20)} \tag{1.63}$$

which is going to be one of the most critical specifications in the design of the SC converter of Chapter 3. We note in fact that  $K_V$  for Class-D oscillator can be as high as 600 MHz/V [4].

As a result of frequency pushing, noise present in the supply voltage gets also picked up by the oscillator, and randomly modulates the oscillation frequency, through the same mechanism explained before. This leads to the conversion of noise in the power supply into phase noise. We can quantify how much supply noise gets converted into phase noise by looking at the following formula:

$$\mathcal{L}_{\text{supply}}\left(\Delta\omega\right) = 10\log_{10}\left(\frac{\left(2\pi K_{\text{V}}\right)^{2}}{\Delta\omega^{2}}V_{\text{n,supply}}^{2}\left(\Delta\omega\right)\right)$$

(1.64)

where  $V_{n,supply}^2$  is the power spectral density of the supply noise. To preserve the inherit phase noise of the oscillator we have to satisfy the condition:

$$\mathcal{L}_{\text{supply}}\left(\Delta\omega\right) \ll \mathcal{L}\left(\Delta\omega\right) \tag{1.65}$$

This leads to:

$$V_{\rm n, supply}^2 < \frac{10^{\frac{-FOM}{10}}}{10^3 P_{\rm DC}} \left(\frac{\omega_{osc}}{2\pi K_{\rm V}}\right)^2$$

(1.66)

which tells us the maximum value that the supply noise can assume, before deteriorating the phase noise of the oscillator. Note that even though Equation 1.66 seems to suggest that by increasing the frequency of the oscillation  $\omega_0$  the oscillator is able to tolerate more supply noise, we have to consider that  $K_v$  is also weakly dependent from frequency. This effect is due to how the capacitance of the tank is realized.  $C_{\text{TOT}}$  is generally composed of a fixed capacitor  $C_{\text{fix}}$ , a variable capacitor  $C_{\text{tune}}$  needed to tune the oscillation frequency, as we will see in Section 2.2, and the parasitic capacitances  $C_{\text{par}}$  of the switches. The expression for  $C_{\text{TOT}}$  is therefore the following:

$$C_{\rm TOT} = C_{\rm fix} + C_{\rm tune} + C_{\rm par} \tag{1.67}$$

The effective value  $C_{\text{par}}$  however can be modulated by the supply voltage, contributing to  $K_{\text{V}}$ . In order to increase  $\omega_0$ , following Equation 1.10, we have to decrease  $C_{\text{tune}}$ . This in turn makes  $C_{\text{par}}$ , in proportion, a bigger component of  $C_{\text{TOT}}$  leading to an increase in  $K_{\text{V}}$ . As a result the ratio  $\omega_0 / (2\pi K_{\text{V}})$  remains almost constant across the operating frequency range.

# CHAPTER 2

# **Class-D** Oscillators

In this chapter an analysis of the Class-D oscillator and its advantages over other oscillator topologies is presented. An analysis on the time-variant nature of the Class-D tank is made, in order to outline how critical design parameters such as oscillation frequency, current consumption and even phase noise are influenced by the nature of the Class-D tank. This analysis is naturally instrumental in order to understand how to approach the design of Class-D VCOs which is also touched upon in this chapter.

# 2.1 Topology Overview

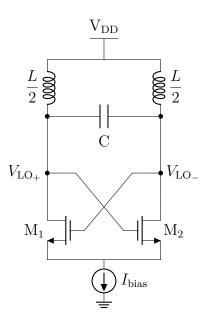

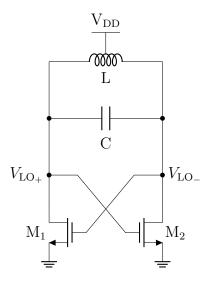

Figure 2.1: Class-D oscillator scheme

By removing the tail generator from a Class-B oscillator we push, as anticipated, the oscillator in its voltage limited region obtaining the topology of a Class-D oscillator, shown in Figure 2.1.

Additionally it has to be noted that to guarantee good Class-D operation, switches  $M_1$  and  $M_2$  have to be sized so that their equivalent resistance is negligible with respect to the tank equivalent resistance.

One of Class-D main characteristics is that it oscillates at an amplitude of  $\hat{V}_{\text{LO,ClassD}} \simeq 3V_{\text{DD}}$ . This makes the Class-D oscillator incredibly attractive for operation at low  $V_{\text{DD}}$  since it is able to guarantee an excellent level of phase noise even when the supply voltage is limited. We have in fact seen in Equation 1.43 how the phase noise is dependent on the oscillation amplitude  $\hat{V}_{LO}$  and compared to a Class-B Oscillator that, as we have seen in Section 1.4.1, reaches a maximum value of  $\hat{V}_{\text{LO,ClassB}} = V_{\text{DD}} - V_{\text{S}}$ , it's easy to see why the Class-D topology excels for very low power supply applications.

On the other hand, even though the Class-D oscillator is capable of producing less phase noise than a Class-B Oscillator, for the same power consumption, this comes at the cost of a higher power supply pushing which can be as high as 600 MHz/V and needs to be kept in high consideration during the design process.

The key difference between Class-D and Class-B oscillators, besides the tail generator, is that the Class-D *LC* tank displays a time-variant nature, meaning that the properties of the tank change during the oscillation period. Not only that, but the behaviour of the Class-D oscillator changes based on the nature of the tank capacitance: floating or single-ended. In reality, since the tank can't be purely floating or single-ended, the behaviour of the oscillator is going to be confined between two different working extremes. In the following sections we are going to show the expressions of the behaviour of a Class-D oscillator, based on these particular properties, as showed in [4].

### 2.1.1 Oscillation Frequency

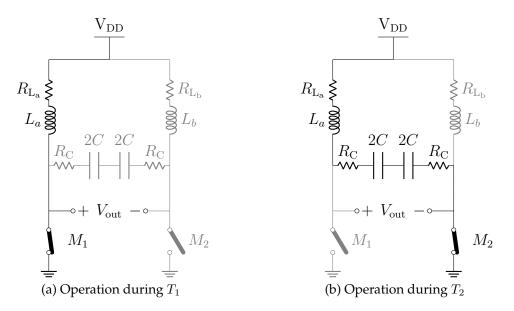

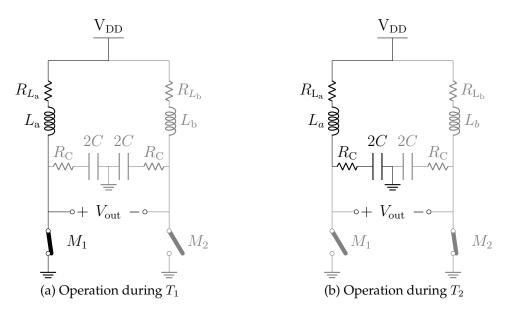

As anticipated, due to the time-variant nature of the tank, the Class-D oscillator changes its properties based on the nature of the capacitance present in the tank. The aforementioned property extends even to its oscillation frequency which has the peculiarity of varying between two extremes  $\omega_{0,\text{float}}$  for a completely floating tank capacitance and  $\omega_{0,\text{se}}$  for a completely single-ended tank capacitance. This is in sharp contrast with the fixed  $\omega_0$  value of Class-B oscillators, as seen in Equation 1.10. In order to derive expressions for  $\omega_{0,se}$  and  $\omega_{0,float}$  it is necessary to study how the current flowing into the inductor  $L_a = L_b = L/2$  evolves during an oscillation period. We take, as a reference, the equivalent scheme of the Class-D oscillator shown in Figure 2.2 for the case where the oscillator is loaded with a floating capacitor and the one showed in Figure 2.3 for when in turn a single-ended capacitor is used.

Figure 2.2: Equivalent scheme of a Class-D oscillator with floating capacitance

Figure 2.3: Equivalent scheme of a Class-D oscillator with single-ended capacitance

The operation of the oscillator during an oscillation period  $T_{\text{osc}}$  is divided into 2 phases. During  $T_1$  (i.e. for  $0 < t < T_{\text{osc}}/2$ ),  $M_1$  shorts  $L_a$  to ground and  $i_{\text{L}_a}(t)$  results from the exponential charge of  $L_a$ . During  $T_2$  (i.e. for  $T_{\text{osc}}/2 < t < T_{\text{osc}}$ ), on the other hand,  $M_1$  is off and  $L_a$  resonates with the equivalent tank capacitance  $C_{\text{eq}}$ . In this last case  $i_{L_a}(t)$  is a sinusoidal current wave with oscillation frequency  $\omega_{tank}$  of:

$$\omega_{\rm tank} = \sqrt{\frac{1}{L_{\rm a}C_{\rm eq}}} \tag{2.1}$$

where  $C_{eq} = C$  in the case of Figure 2.2 and  $C_{eq} = 2C$  in the case of Figure 2.3.

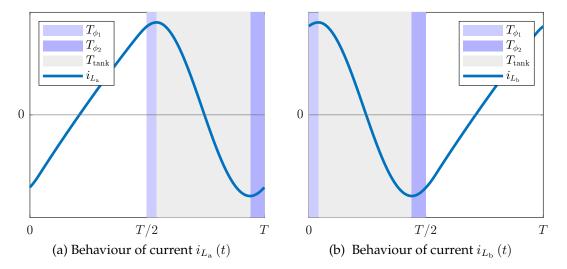

The same behaviour can be observed by looking at the operation of transistor  $M_2$  and the inductor current  $i_{L_b}(t)$  since their operation is complementary with respect to  $M_1$ and  $i_{L_a}(t)$ . In Figure 2.4 the time evolution of  $i_{L_a}$  and  $i_{L_b}$  is plotted showing this aspect and highlighting the period  $T_{tank}$  of  $\omega_{tank}$ .

Figure 2.4: Currents on the inductors  $L_{\rm a}$  and  $L_{\rm b}$

Note from Figure 2.4 how the oscillation period of  $T_{tank}$  is smaller than  $T_2$  so we have to take this into account by writing:

$$T_2 = T_{\phi 1} + \frac{T_{\text{tank}}}{2} + T_{\phi 2} \tag{2.2}$$

During  $T_1$  the expression of  $i_{La}(t)$  is:

$$i_{L_{a},T_{1}}(t) = i_{1} + \frac{V_{\text{DD}}}{R_{L_{a}}} \left(1 - e^{-(R_{L_{a}}/L_{a})t}\right)$$

(2.3)

where  $i_1 = i_{L_a}(0) = i_{L_a}(T_{osc})$  and  $R_{L_a} = R_{L_b} = R_L/2$  is the series resistance of  $L_a$ . The derivative of  $i_{L_a,T_1}(t)$  is:

$$\dot{i}_{L_{a},T_{1}}(t) = \frac{V_{\text{DD}}}{L_{a}}e^{-(R_{L_{a}}/L_{a})t}$$

(2.4)

We can then proceed by calculating the values of  $i_{L_a,T_1}(t)$  and  $\dot{i}_{L_a,T_1}(t)$  at the transition time  $t = T_{osc}/2$  between  $T_1$  and  $T_2$ :

$$i_{L_{a},T_{1}}\left(\frac{T_{\text{osc}}}{2}\right) = i_{1} + \frac{V_{\text{DD}}}{R_{L_{a}}}\left(1 - e^{\pi/Q_{L_{a}}}\right) = i_{0}$$

(2.5)

$$\dot{i}_{L_{a},T_{1}}\left(\frac{T_{\rm osc}}{2}\right) = \frac{V_{\rm DD}}{R_{L_{a}}}e^{-\pi/Q_{L_{a}}} = i'_{0}$$

(2.6)

where  $Q_{L_{\rm a}} = \omega_{

m osc} L_{\rm a}/R_{L_{\rm a}}$ , with  $\omega_{osc} = 2\pi/T_{

m osc}$

Assuming the tank losses to be negligible we can rewrite  $i_0$  as:

$$i_0 = i_1 + \frac{V_{DD}}{L_a} \frac{T_{\text{osc}}}{2}$$

(2.7)

and the same applies for  $i'_0$ :

$$i_0' = \frac{V_{DD}}{L_a} \tag{2.8}$$

Moreover, since there are no losses, the current on the inductor  $L_a$  at time t = 0 and  $t = T_{osc}/2$  is the same in modulus, therefore:

$$-i_{La}(0) = i_{La}(T_{\rm osc}/2) \tag{2.9}$$

Combing Equation 2.9 and Equation 2.7 we get:

$$-i_1 = i_0 = i_1 + \frac{V_{DD}}{L_a} \frac{T_{\text{osc}}}{2}$$

(2.10)

which allow us to immediately write:

$$i_0 = \frac{1}{2} \left( \frac{V_{DD}}{L_{\rm a}} \frac{T_{\rm osc}}{2} \right) = \frac{\pi V_{DD}}{2L_{\rm a}\omega_{\rm osc}}$$

(2.11)

During  $T_2$  we treat, as already mentioned,  $i_{L_a}(t)$  as a portion of sinusoid of angular frequency  $\omega_{tank}$ . This sinewave is however damped by the combined losses of  $L_a$  and  $C_{eq}$ . Knowing the values of  $i_{L_a}(t)$  and of  $\dot{i}_{L_a}(t)$  at  $t = T_{osc}/2$ , due to the continuity of the current, the expression of  $i_{L_a,T_1}(t)$  during  $T_2$  can be written as:

$$i_{L_{a},T_{2}}(t) = \left\{ \left( \frac{i_{0}'}{\omega_{\text{tank}}} + \frac{i_{0}}{2Q_{\text{tank}}} \right) \sin\left(\omega_{\text{tank}}t'\right) + i_{0}\cos\left(\omega_{\text{tank}}t'\right) \right\} e^{-\left(\left(R_{L_{a}} + R_{C_{\text{eq}}}\right)/(2L_{a})\right)t'}$$

(2.12)

where  $t' = t - T_{\text{osc}}/2$ .

Furthermore by substituting  $Q_{\text{tank}} = \omega_{\text{tank}} L_{\text{a}} / (R_{L_{\text{a}}} + R_{C_{\text{eq}}})$  we get:

$$i_{L_{a},T_{2}}(t) = I_{pk} cos \left(\omega_{tank} t' - \phi_{0}\right) e^{-\left(\left(R_{L_{a}} + R_{C_{eq}}\right)/(2L_{a})\right)t'}$$

(2.13)

$$I_{\rm pk} = \sqrt{\left(\frac{i_0'}{\omega_{\rm tank}} + \frac{i_0}{2Q_{\rm tank}}\right)^2 + i_0^2} \simeq \sqrt{\left(\frac{i_0'}{\omega_{\rm tank}}\right)^2 + i_0^2}$$

(2.14)

$$\phi_0 = \arctan\left(\frac{i'_0}{i_0\omega_{\text{tank}}} + \frac{1}{2Q_{\text{tank}}}\right) \simeq \left(\frac{i'_0}{i_0\omega_{\text{tank}}}\right)$$

(2.15)

The term  $\phi_0$  can be further rewritten as:

$$\phi_0 = \arctan\left(\frac{2}{\pi}\frac{\omega_{\rm osc}}{\omega_{\rm tank}}\right) \simeq \frac{2}{\pi}\frac{\omega_{\rm osc}}{\omega_{\rm tank}} = \frac{2}{\pi}\frac{T_{\rm tank}}{T_{\rm osc}}$$

(2.16)

By noticing that due to the symmetry of  $i_{L_a}(t)$  we have that  $T_{\phi 1} = T_{\phi 2} = T_{\phi}$ .  $T_{\phi}$  is given by:

$$T_{\phi} = \frac{\phi_0}{2\pi} T_{\text{tank}}$$

(2.17)

We have now all the elements to derive the oscillation frequency as follows:

$$T_2 = \frac{T_{\rm osc}}{2} \tag{2.18}$$

$$=\frac{T_{\text{tank}}}{2} + 2T_{\phi} \tag{2.19}$$

$$= \frac{T_{\text{tank}}}{2} + 2\frac{\varphi_0}{2\pi}T_{\text{tank}}$$

(2.20)

$$= T_{\text{tank}} + 2T_{\text{tank}}^2$$

(2.21)

$$= \frac{\operatorname{dank}}{2} + \frac{1}{\pi^2} \frac{\operatorname{dank}}{T_{\mathrm{osc}}}$$

(2.21)

which results in

$$T_{\rm osc} = \alpha T_{\rm tank} \implies \omega_{\rm osc} = \frac{\omega_{\rm tank}}{\alpha} = \frac{1}{\alpha} \sqrt{\frac{1}{L_{\rm a}C_{\rm eq}}}$$

(2.22)

with

$$\alpha = \frac{1}{2} + \sqrt{\frac{1}{4} + \frac{4}{\pi^2}} \simeq 1.3 \tag{2.23}$$

Since  $C_{eq}$  changes if the tank capacitance is floating or single-ended  $\omega_{tank}$  changes as well and we have two separate oscillation frequencies.