Industrial Engineering Department Master's degree in Electrical Energy Engineering

Master's thesis in Electrical Energy Engineering

## Design and implementation of a GaN based dual active bridge converter for electric vehicle charger

SUPERVISOR: Prof. Manuele Bertoluzzo CO-SUPERVISOR: M.Sc. Konstantin Siebke

CANDIDATE: Marco Giacomazzo

ACADEMIC YEAR 2019-2020

AB Institut für Elektrische Maschinen, Antriebe und Bahnen TU Braunschweig

### University of Padua

INDUSTRIAL ENGINEERING DEPARTMENT Master's degree in Electrical Energy Engineering

MASTER'S THESIS

## Design and implementation of a GaN based dual active bridge converter for electric vehicle charger

Candidate: Marco Giacomazzo 1159867 Supervisor: **Prof. M. Bertoluzzo** Industrial Engineering Department Co-supervisor: **M.Sc. Konstantin Siebke**

Technische Universität Braunschweig

## Contents

| Lis | st of Tables                                                                                                                                                                                 | III                                           |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Lis | st of Figures                                                                                                                                                                                | v                                             |

| 1   | Introduction1.1Energy efficiency1.2Challenges1.3Automotive applications of DAB converter1.4GaN                                                                                               | 2                                             |

| 2   | Analysis of dual active bridge converter         2.1       Forward mode                                                                                                                      | <b>21</b><br>22<br>27<br>29<br>38<br>45<br>46 |

| 3   | Charging process, circuit simulation and total power lost trend         3.1       Battery stack and charging model                                                                           |                                               |

| 4   | High frequency transformer design4.1General characterization of a high frequency transformer4.2High frequency effects on the windings4.3General design steps4.4Integrated leakage inductance | <b>69</b><br>69<br>72<br>74<br>84             |

| 5   | Small signal model and control loops5.1Small signal model5.2Current control loop5.3Cascade control loop5.4Anti-windup strategies                                                             | 109                                           |

| 6   | Laboratory results         6.1       Circuit layout         6.2       Current control loop         6.3       Working conditions                                                              |                                               |

| 7   | Alternative control techniques         7.1       Single PWM control         7.2       Dual PWM control                                                                                       | <b>125</b><br>127<br>135                      |

| 8   | Conclusion                                                                                                                                                                                   | 143                                           |

| Bi  | bliography                                                                                                                                                                                   | 145                                           |

## **List of Tables**

| 1.1 | Different energy demands.                                                                                 | 3   |

|-----|-----------------------------------------------------------------------------------------------------------|-----|

| 1.2 | Properties of different semiconductors                                                                    | 7   |

| 2.1 | Roles of the devices involved in ZVS turning on of output bridge switches with positive inductive         |     |

|     | current                                                                                                   | 31  |

| 2.2 | Roles of the devices involved in ZVS turning on of input bridge switches with positive inductive current. | 31  |

| 2.3 | Working parameters of the charger.                                                                        | 38  |

| 3.1 | Specification of the lithium iron battery.                                                                | 53  |

| 3.2 | Circuit simulation parameters.                                                                            |     |

| 3.3 | Circuit simulation results.                                                                               |     |

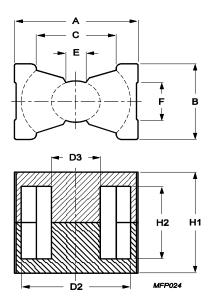

| 4.1 | Main dimensions of PQ4040 transformer                                                                     | 89  |

| 4.2 | Main dimensions of PQ5050 transformer.                                                                    | 95  |

| 4.3 | Leakage inductances and different power losses in the three designed transformers                         | 102 |

| 6.1 | Efficiency trend in buck, matching and boost modes.                                                       | 124 |

# **List of Figures**

| 1.1  | Comparison of $CO_2$ emissions for different power trains, considering different ways of energy pro-           |    |

|------|----------------------------------------------------------------------------------------------------------------|----|

|      | duction [2]                                                                                                    | 2  |

| 1.2  | Schematic block of the entire charger.                                                                         | 3  |

| 1.3  | Full active bridge AC/DC converter.                                                                            | 4  |

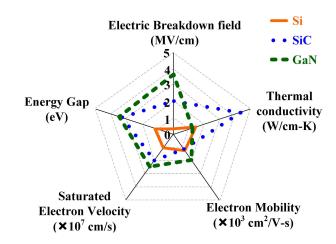

| 1.4  | Performances schematic plot of Si, SiC and GaN.                                                                | 8  |

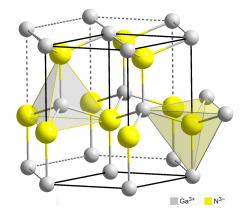

| 1.5  | Crystal lattice of GaN.                                                                                        | 9  |

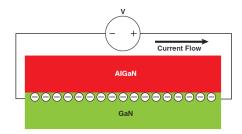

| 1.6  | Two dimensional electron gas under external field.                                                             | 9  |

| 1.7  | Depletion-mode lateral GaN HFET.                                                                               | 9  |

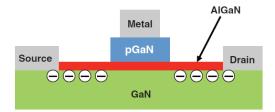

| 1.8  | Schematic section of a pGaN enhancement transistor.                                                            | 10 |

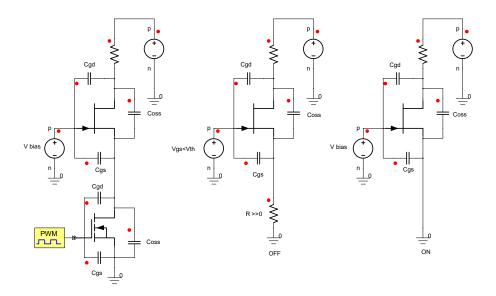

| 1.9  | Cascade hybrid configuration and operating stages.                                                             | 10 |

| 1.10 | Schematic circuit during conduction of low voltage mosfet.                                                     | 11 |

|      | Changing of $R_{on}$ varying gate length, with $E_c$ equal to 1 [MV/cm].                                       | 13 |

|      | Switching power losses during turn-on (a) and turn-off (b) of a power device.                                  | 14 |

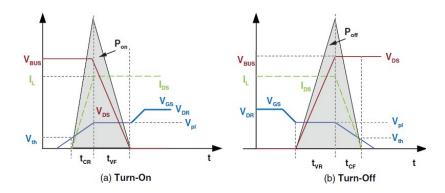

|      | Resistive models of lateral (a) and vertical (b) GaN power switches.                                           | 14 |

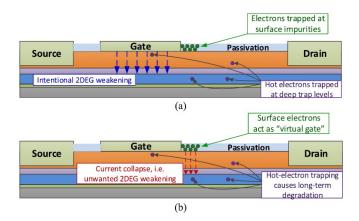

|      | Events that cause an increase of $R_{on}$ : charges trapped in off-state (a); consequent current collapse (b). | 15 |

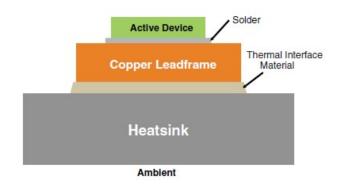

|      | Section of proposed thermal conductivity improvement.                                                          | 16 |

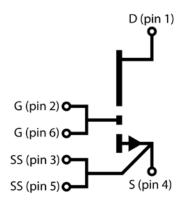

|      | Circuit symbol of GS66516B.                                                                                    | 17 |

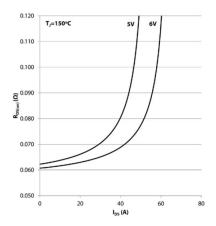

|      | On resistance trend with different values of gate driver pulse and direct current, for fixed temperature.      | 17 |

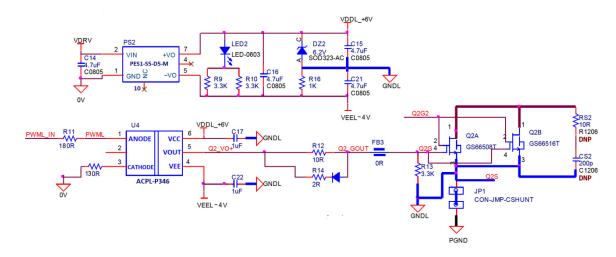

|      | Gate bias and driver circuit.                                                                                  | 18 |

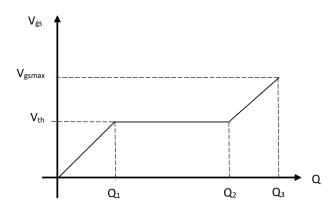

|      | Gate to source voltage waveform vs provided charge.                                                            | 18 |

| 1.17 |                                                                                                                | 10 |

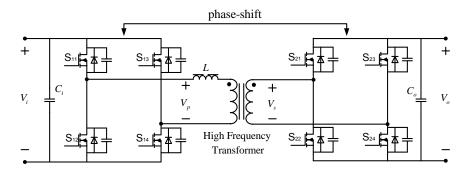

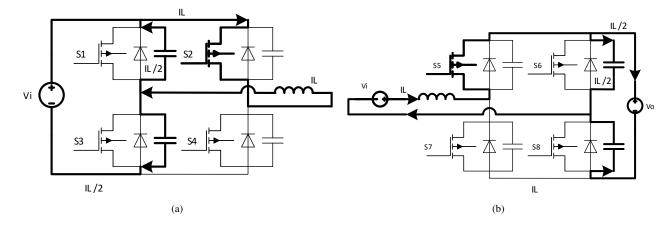

| 2.1  | DAB circuit with single phase shift control.                                                                   | 21 |

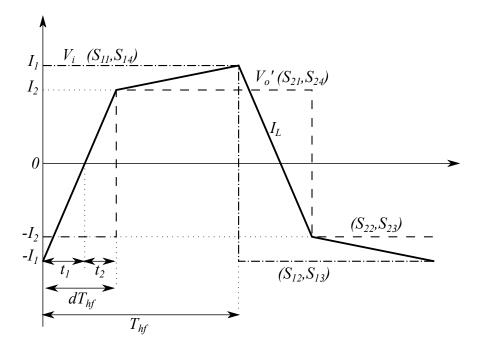

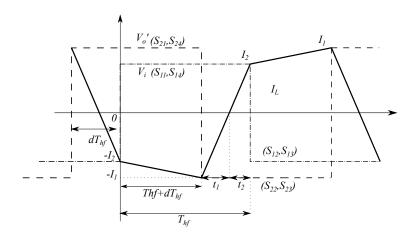

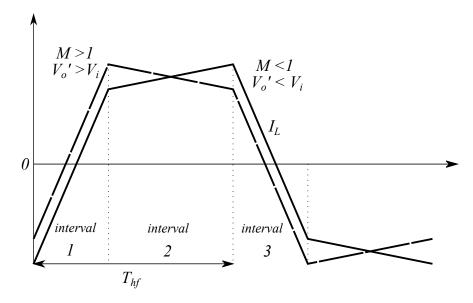

| 2.2  | Voltage and leakage inductance waveforms in buck mode.                                                         |    |

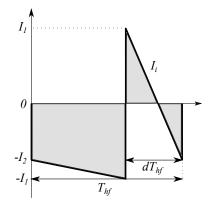

| 2.3  | Output current referred to the primary side.                                                                   | 24 |

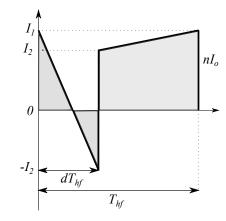

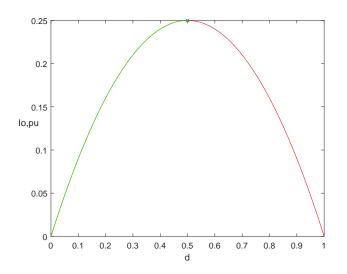

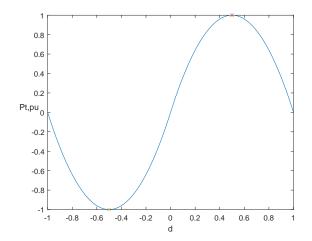

| 2.4  | Load current as a function of the dimensionless phase shift d                                                  | 25 |

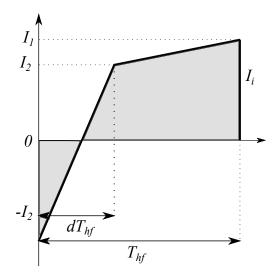

| 2.5  |                                                                                                                | 26 |

| 2.6  | Converter current and voltages in boost mode.                                                                  | 26 |

| 2.7  | Current and voltage waveforms in reverse buck mode.                                                            | 27 |

| 2.8  | Output current in the buck reverse mode.                                                                       | 28 |

| 2.9  | Normalized transmitted power as a function of d.                                                               | 29 |

| 2.10 |                                                                                                                | 29 |

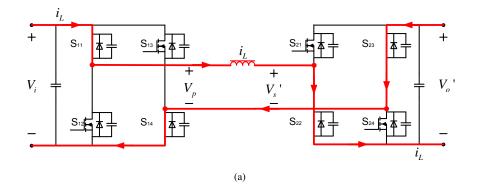

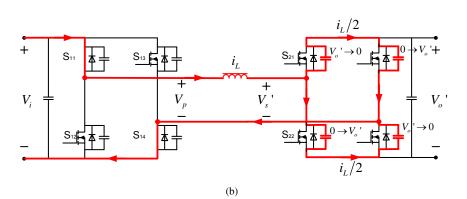

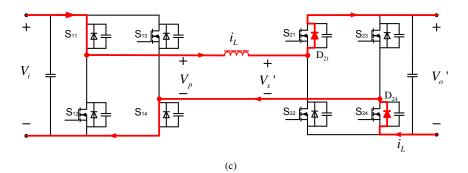

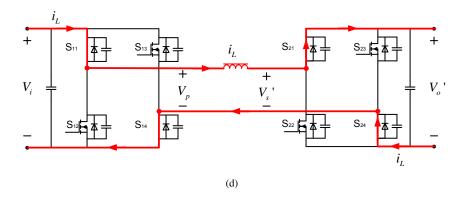

|      | Steady-state conduction intervals in buck/boost mode.                                                          | 31 |

|      | Current paths in the output bridge during a commutation interval.                                              | 32 |

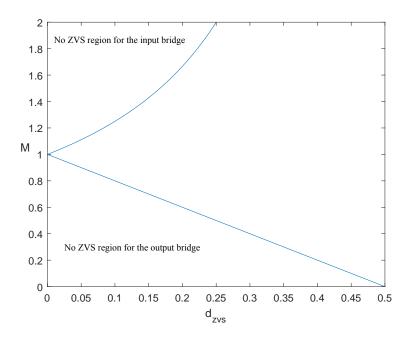

|      | Necessary condition to achieve ZVS in the leading and lagging bridge.                                          | 34 |

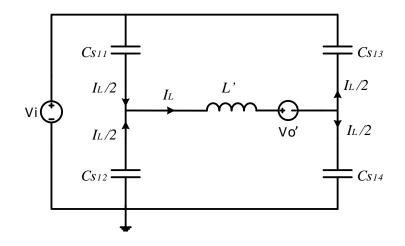

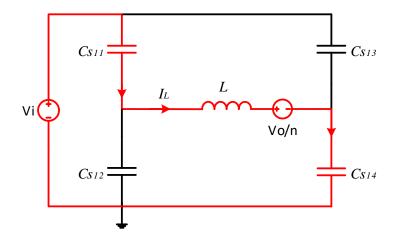

|      | Equivalent circuit during turn off of $S_{11}$ and $S_{14}$ .                                                  |    |

|      | Equivalent circuit during turn off $S_{11}$ and $S_{14}$                                                       |    |

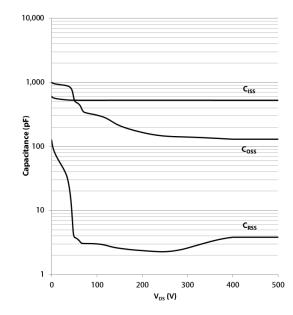

|      | Parasitic capacitances of the GaN HEMT.                                                                        | 39 |

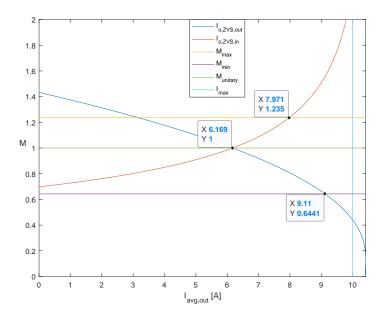

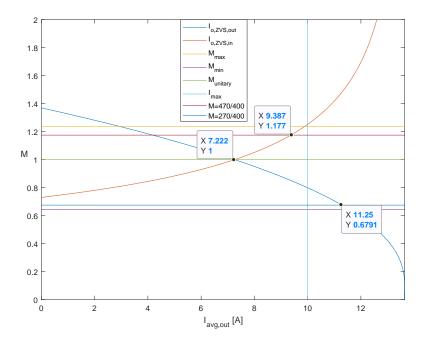

|      | Minimum output current required to ensure ZVS with L=9.6 [ $\mu$ H].                                           |    |

|      | • •                                                                                                            | 40 |

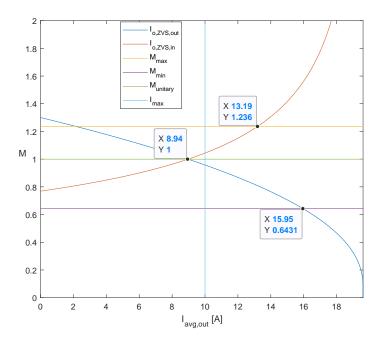

|      | Minimum output current required to ensure ZVS with L=5.1 [ $\mu$ H]                                            | 40 |

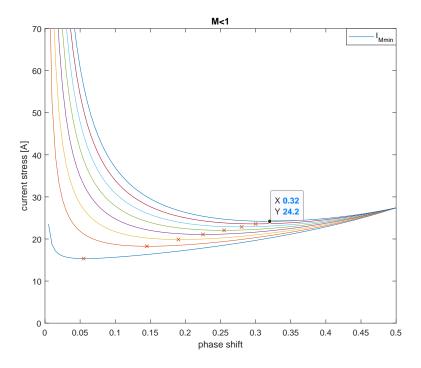

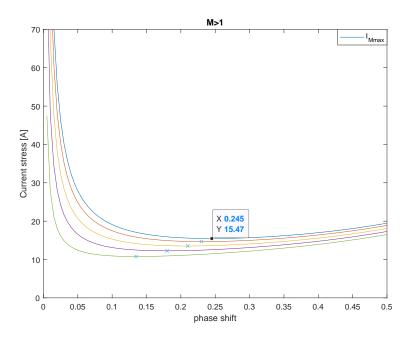

|      | Current stress varying the value of $M$ and $d$ in buck mode.                                                  |    |

|      | Current stress varying the value of $M$ and $d$ in boost mode                                                  | 43 |

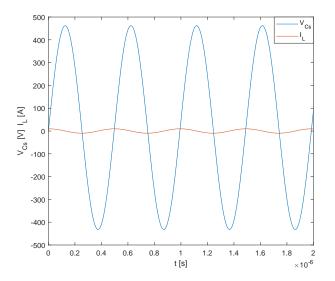

|      | Voltage and current waveforms during the resonant intervals.                                                   | 44 |

|      | Minimum output current required to ensure ZVS with L=7.3 [ $\mu$ H]                                            | 45 |

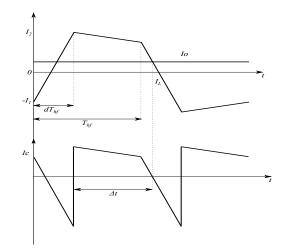

|      | Inductance, output average and capacitance currents.                                                           | 45 |

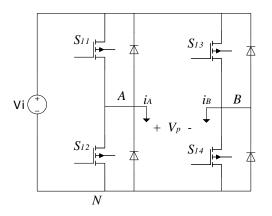

|      | Ideal circuit of the input bridge to analyze the dead time effects on the primary voltage $V_p$                | 46 |

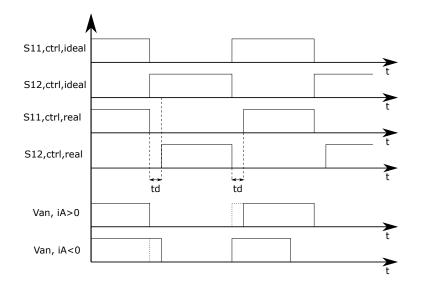

|      | Control signal and output voltage for the first leg in ideal and real case.                                    | 47 |

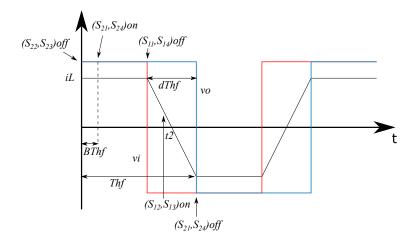

|      | Operation waveforms when the dead time doesn't influence the converter behaviour                               | 48 |

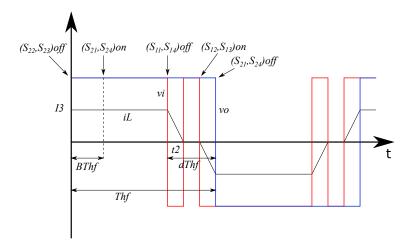

|      | Operation waveforms in presence of reverse voltage polarization.                                               | 48 |

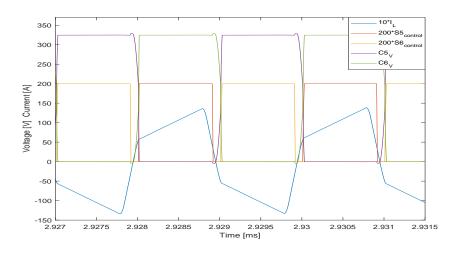

| 2.28 | Simulation result of the voltage reverse polarization effect without parasitic output capacitances             | 50 |

|       | Simulation of the voltage reverse polarization with parasitic output capacitances                           |     |

|-------|-------------------------------------------------------------------------------------------------------------|-----|

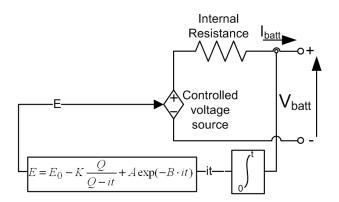

| 3.1   | Simplified battery model.                                                                                   | 54  |

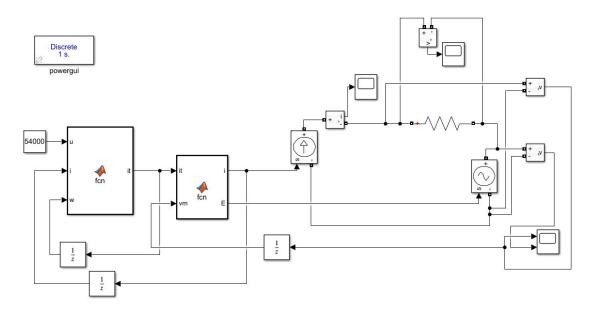

| 3.2   | Simulink model of the battery.                                                                              | 55  |

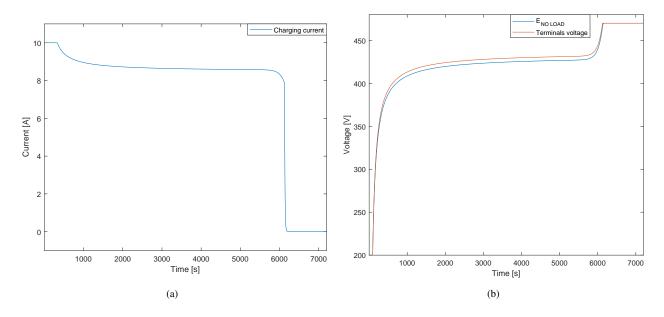

| 3.3   | Current and voltage battery waveforms.                                                                      | 56  |

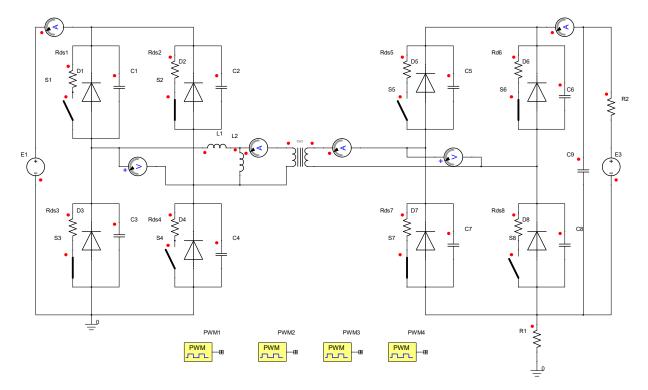

| 3.4   | Schematic circuit of the DAB converter.                                                                     | 57  |

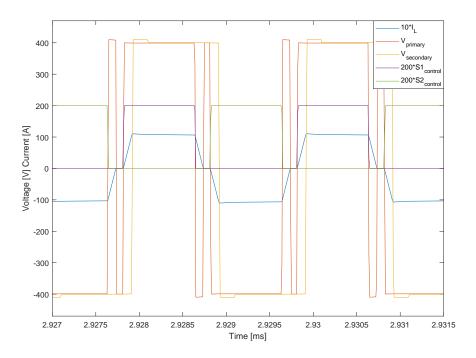

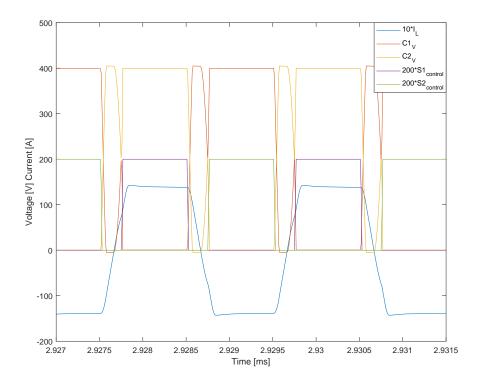

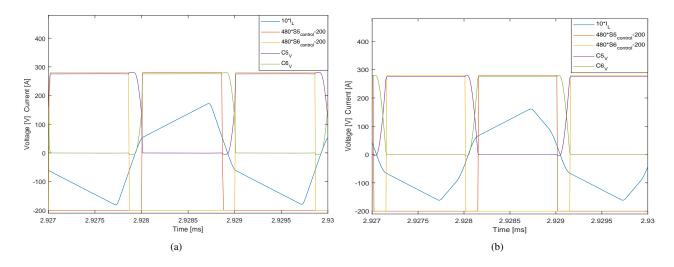

| 3.5   | Main simulation results.                                                                                    | 59  |

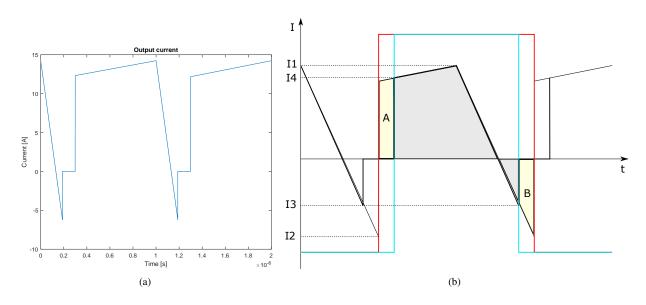

| 3.6   | Hard switching in the output bridge.                                                                        | 60  |

| 3.7   | Real average output current.                                                                                | 61  |

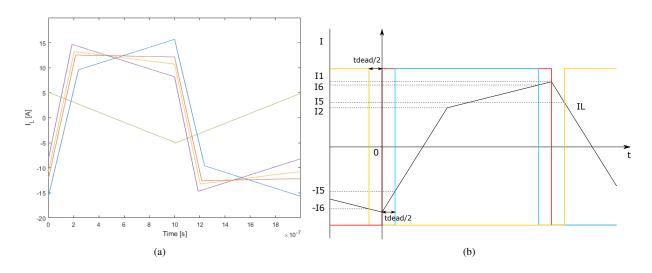

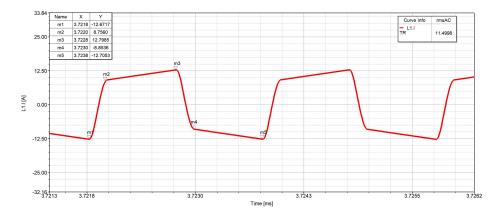

| 3.8   | Inductance current waveforms.                                                                               | 62  |

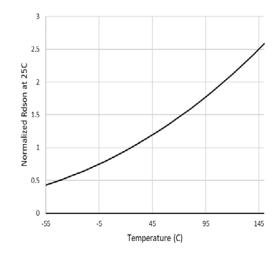

| 3.9   | Normalized power devices on resistance as a function of the temperature.                                    | 65  |

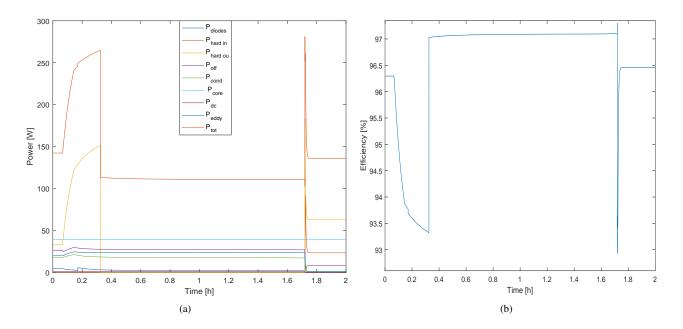

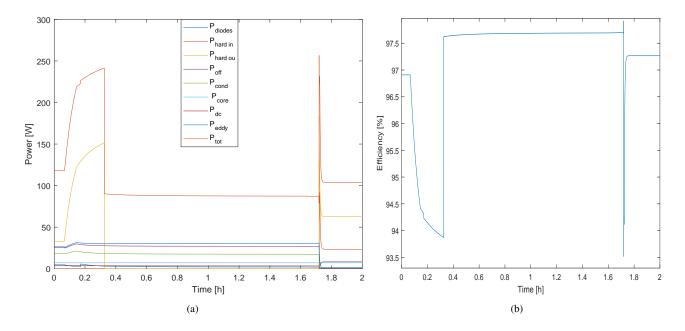

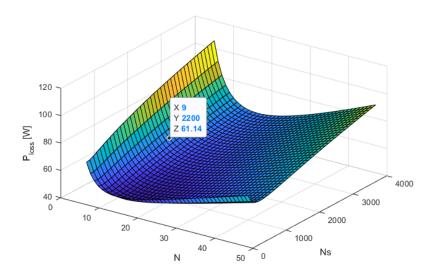

| 3.10  | Total power losses and efficiency during a charging process in the case of PQ5050 transformer with 9 turns. | 67  |

| 3 1 1 | Total power losses and efficiency during a charging process in the case of PQ5050 transformer with          | 07  |

| 5.11  | 12 turns.                                                                                                   | 67  |

|       | 12 turns                                                                                                    | 07  |

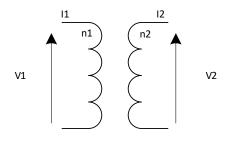

| 4.1   | Ideal circuit of a single phase transformer.                                                                | 70  |

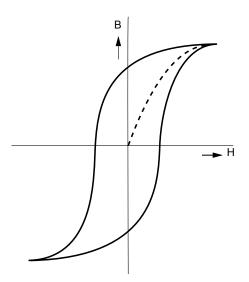

| 4.2   | Hysteresis loop.                                                                                            | 70  |

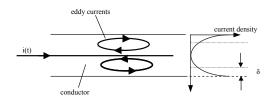

| 4.3   | Current distribution on a bare wire carrying high frequency current.                                        | 72  |

| 4.4   | Current density distribution in a bare wire increasing the operating frequency.                             | 73  |

| 4.5   | Increasing wire resistance with the frequency.                                                              | 73  |

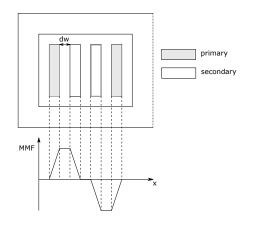

| 4.6   | Proximity effect in multilayer windings.                                                                    | 74  |

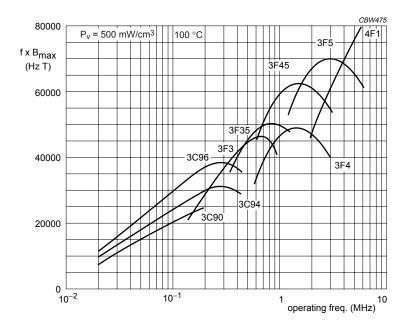

| 4.7   | Performance factor of different ferrite materials produced by Ferroxcube.                                   | 75  |

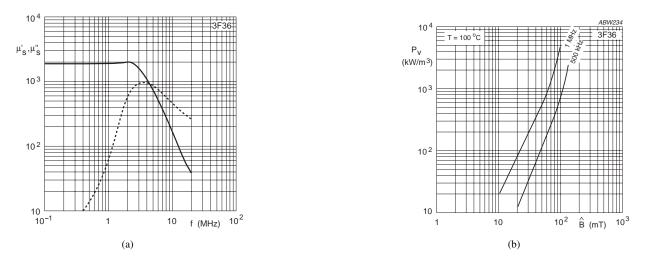

| 4.8   | Complex permeability and specific power losses in ferrite 3F36.                                             | 76  |

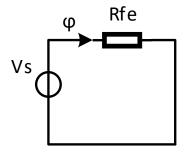

| 4.9   | Magnetic circuit of the transformer.                                                                        | 77  |

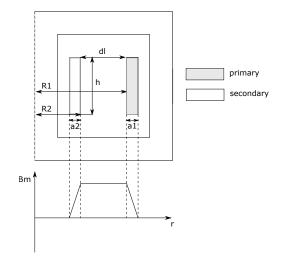

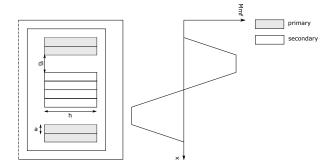

| 4.10  | Magnetic field in half symmetric transformer.                                                               | 78  |

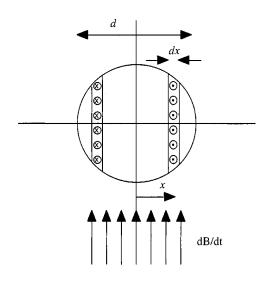

| 4.11  | Cylinder conductor in a uniform magnetic field.                                                             | 79  |

|       | Leakage inductance current at nominal working condition.                                                    | 82  |

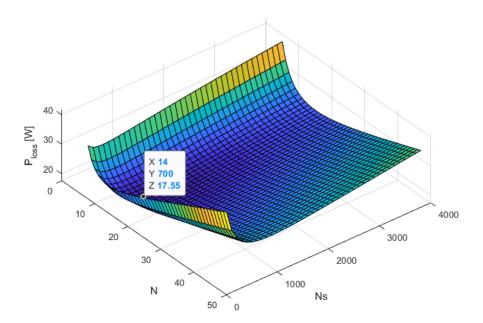

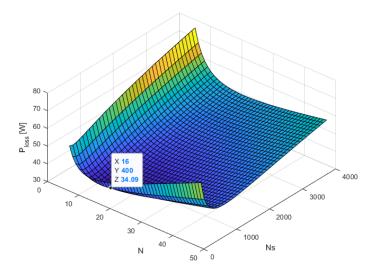

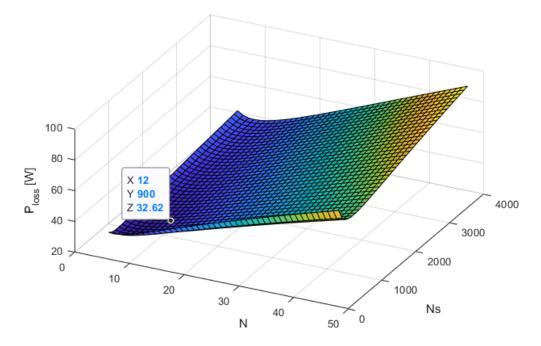

| 4.13  | Total power lost in the transformer as a function of the number of turns and strands                        | 83  |

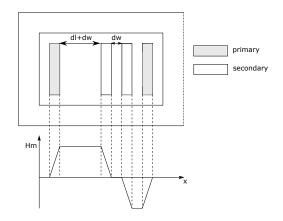

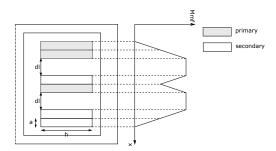

| 4.14  | Field distribution with bigger space between primary and secondary windings.                                | 84  |

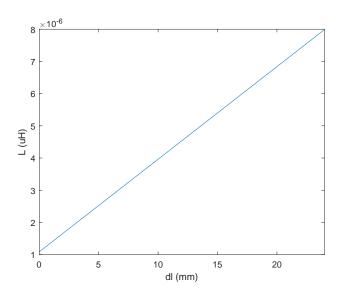

| 4.15  | Module of the leakage inductance as a function of the space between layers                                  | 86  |

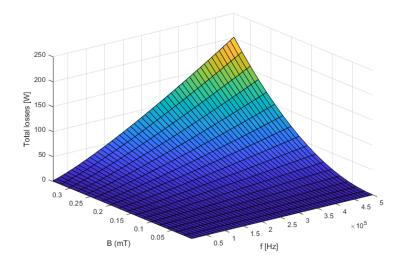

|       | Total power losses trend varying the frequency and the flux density.                                        | 88  |

| 4.17  | Transformer total power losses in the case of asymmetric configuration.                                     | 88  |

|       | Cross section view of PQ 4040 core.                                                                         | 89  |

|       | Axial component of the flux density in radial position                                                      | 91  |

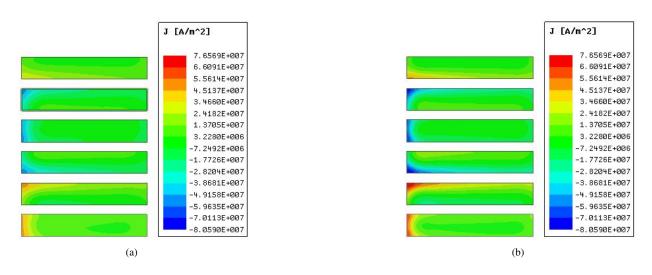

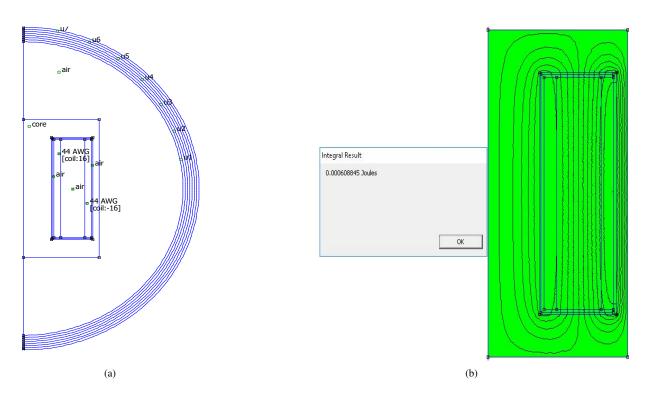

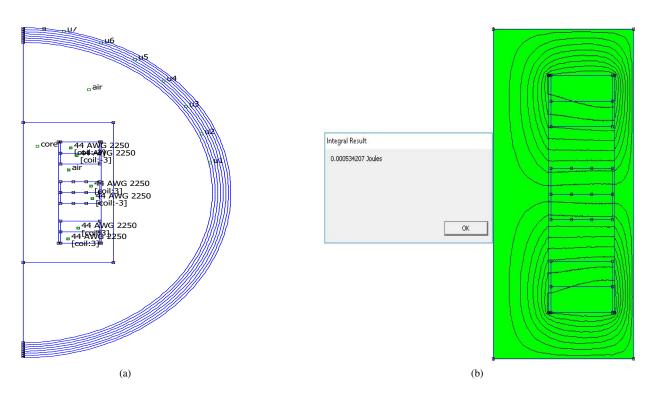

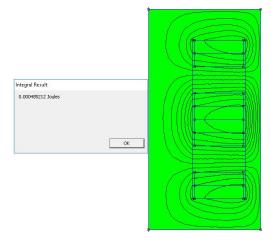

|       | Magnetic problem simulation of the designed PQ4040 transformer                                              | 92  |

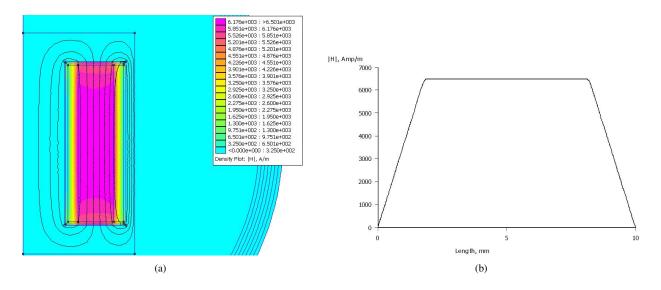

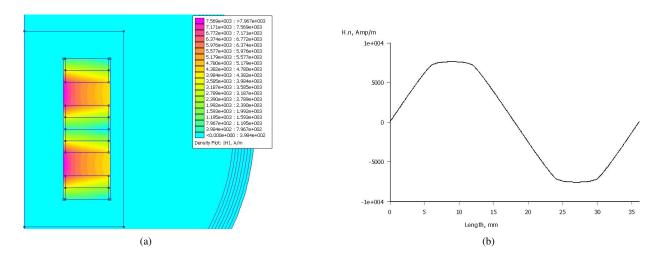

|       | Magnetic field strength in magneto-static simulation.                                                       | 93  |

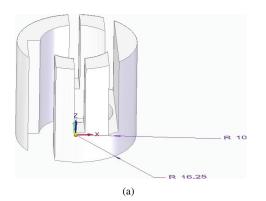

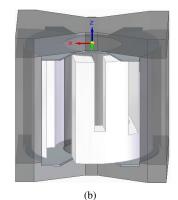

|       | CAD design of the insulator and the total assembly.                                                         | 93  |

|       | 3D printing and construction of the PQ4040 transformer.                                                     | 94  |

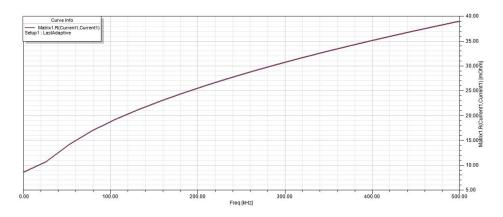

|       | Leakage inductance measurement in the PQ4040.                                                               | 94  |

|       | Total power losses in asymmetric PQ5050 transformer.                                                        | 96  |

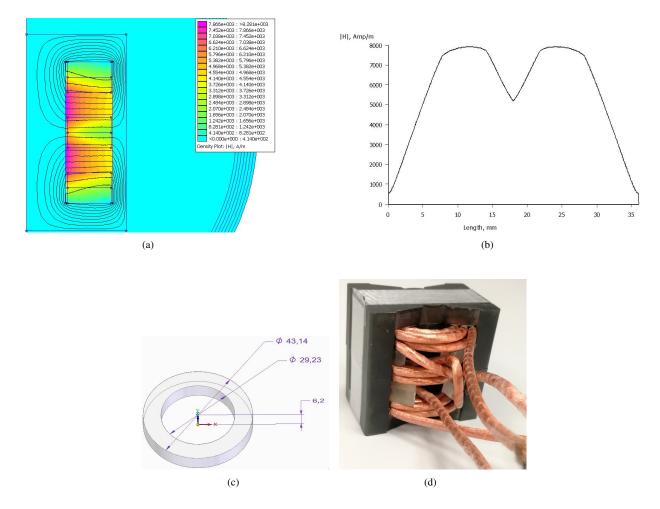

|       | Radial component of the magneto motive force in axial position.                                             | 97  |

|       | Magnetic problem simulation of the designed PQ5050 transformer.                                             | 97  |

|       | Designed PQ5050 transformer.                                                                                | 98  |

|       | Total power losses as a function of the number of strands and turns in the PQ5050 symmetric transformer.    |     |

|       |                                                                                                             | 100 |

|       |                                                                                                             | 101 |

|       |                                                                                                             | 101 |

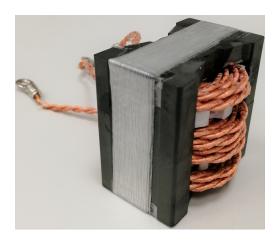

| 4.33  | Symmetric built up transformer.                                                                             | 102 |

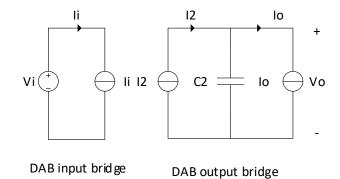

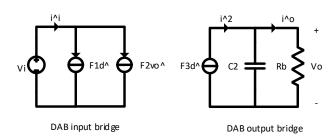

| 5.1   | Average model of the DAB.                                                                                   | 103 |

| 5.2   |                                                                                                             | 105 |

| 5.3   |                                                                                                             | 105 |

| 5.4   |                                                                                                             | 100 |

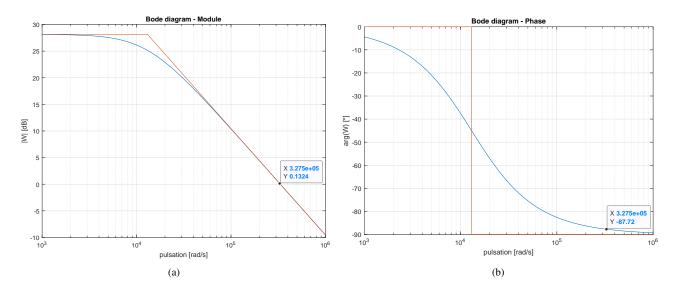

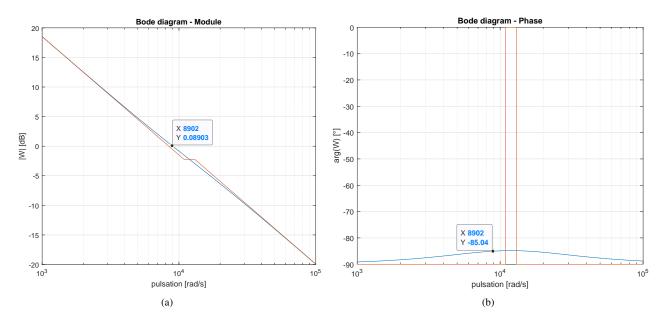

| 5.5   | Module and phase Bode diagrams of the open loop system with PI controller.                                  |     |

| 5.5   | income and phase bode and runs of the open roop system with the controller.                                 | 100 |

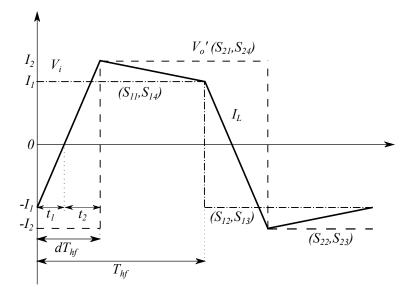

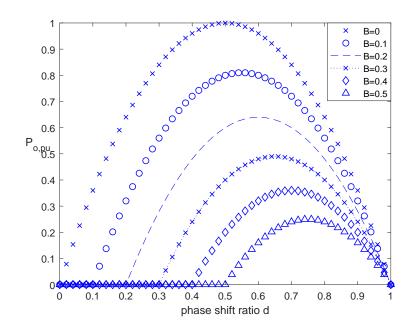

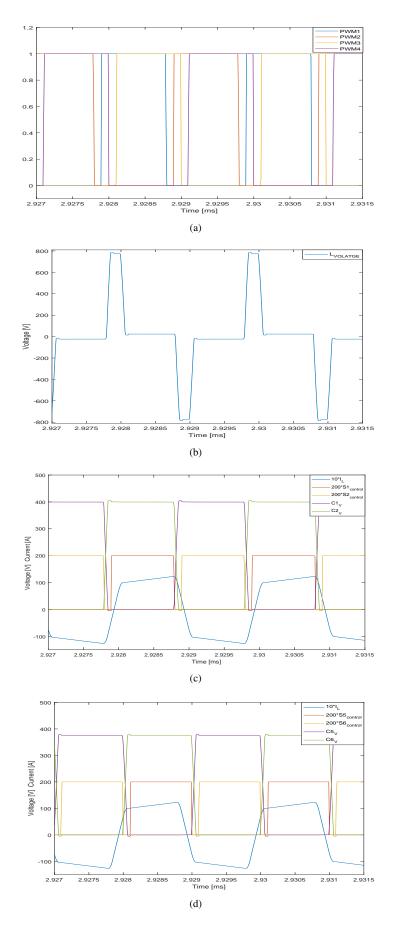

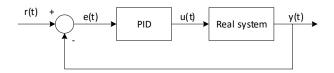

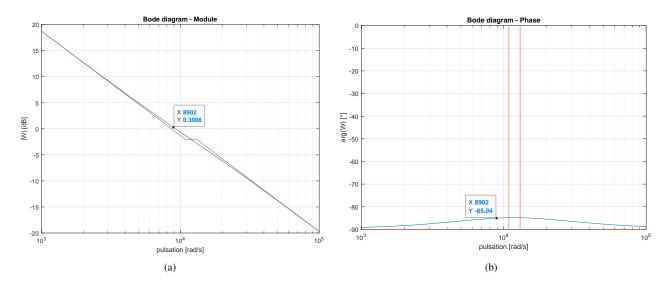

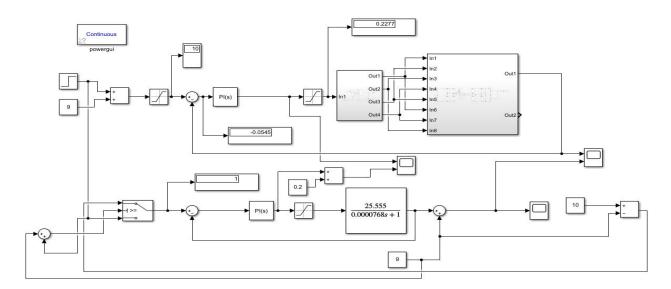

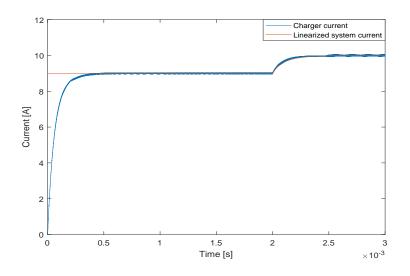

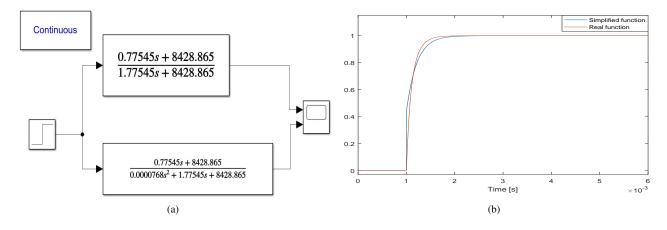

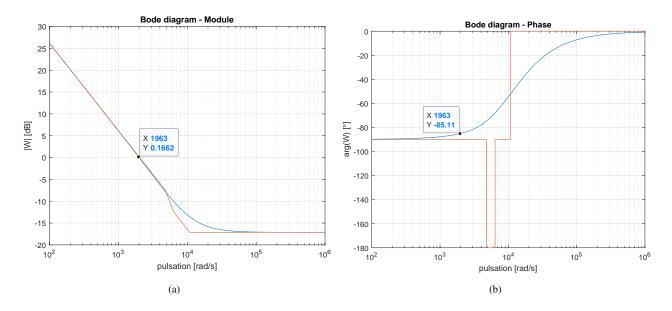

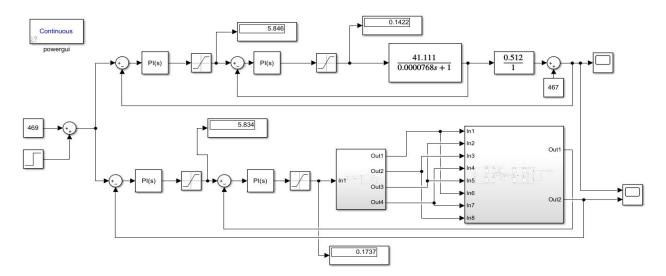

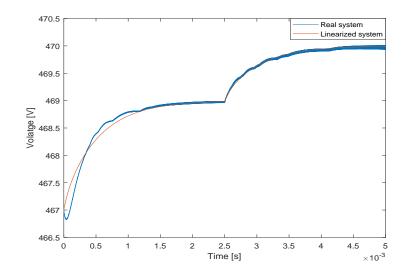

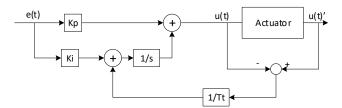

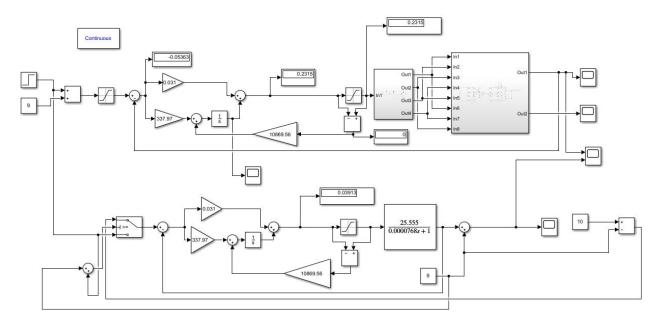

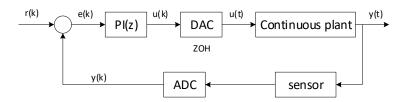

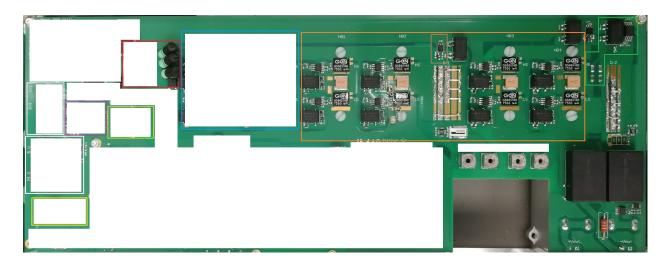

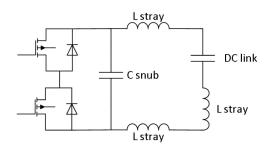

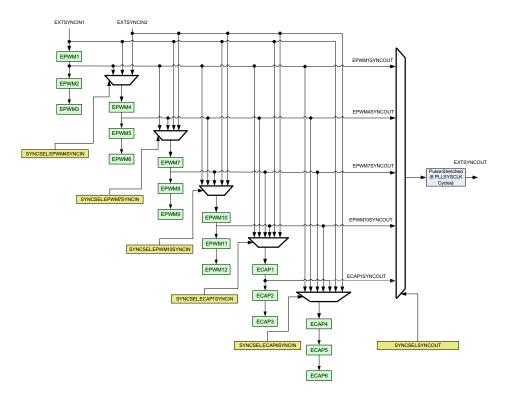

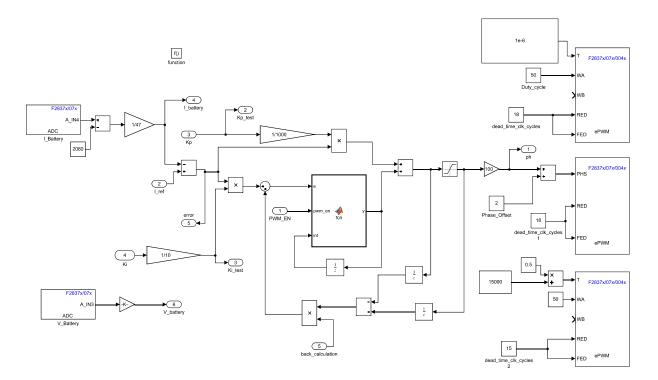

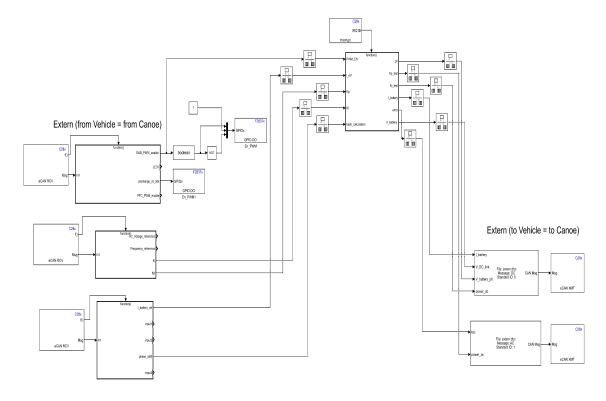

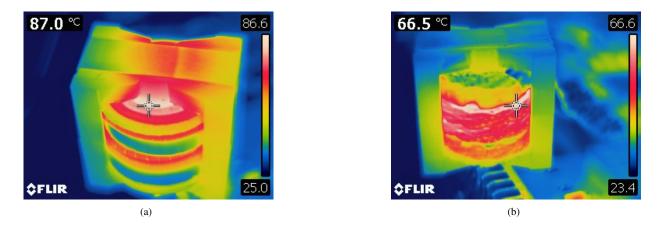

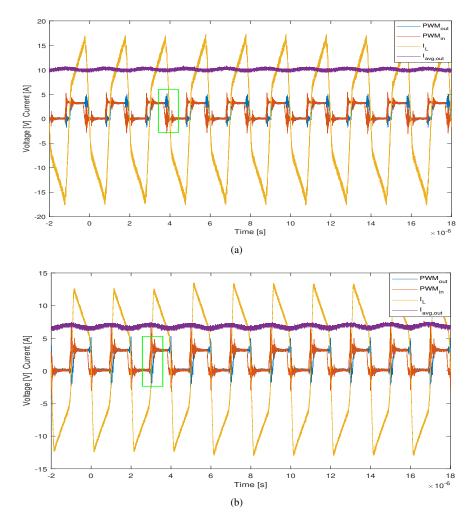

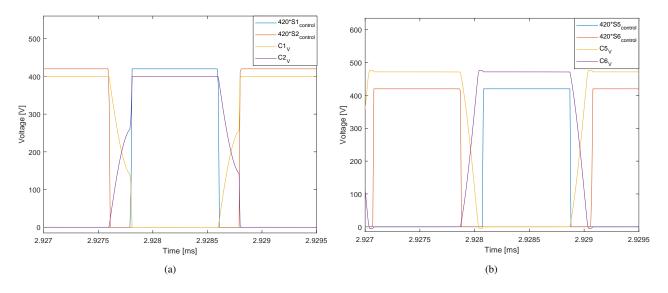

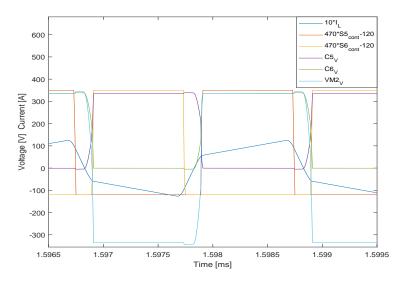

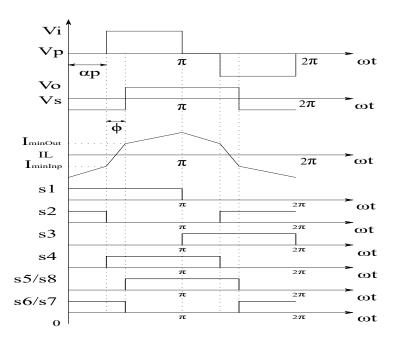

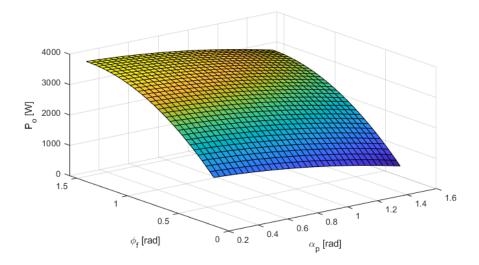

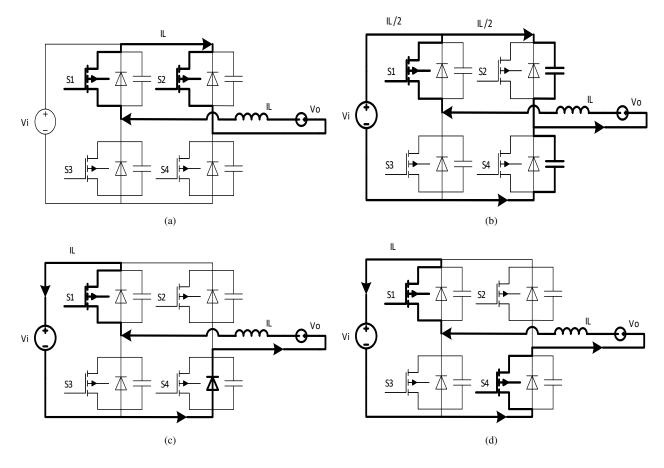

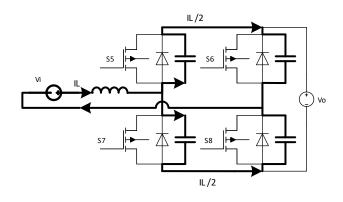

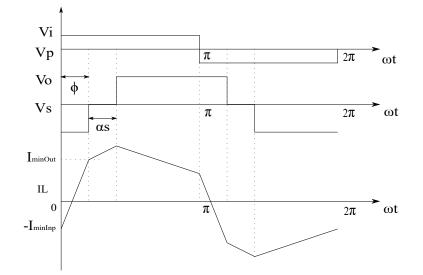

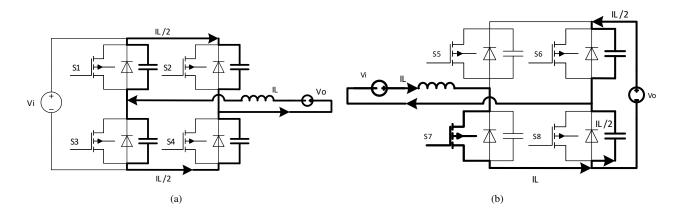

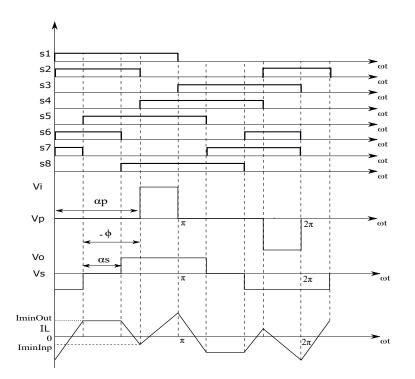

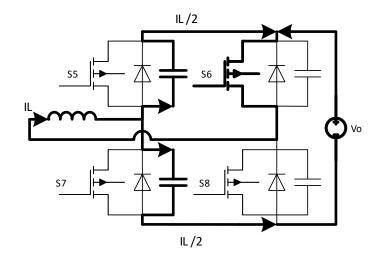

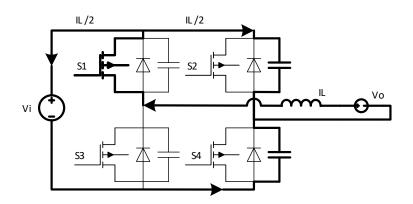

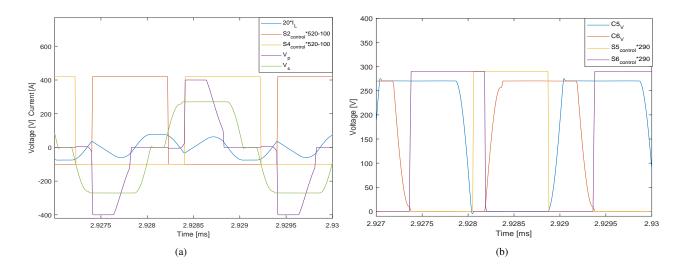

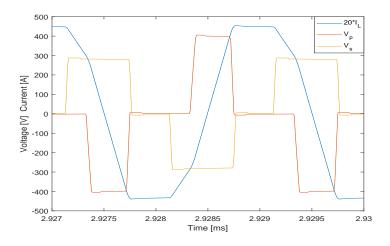

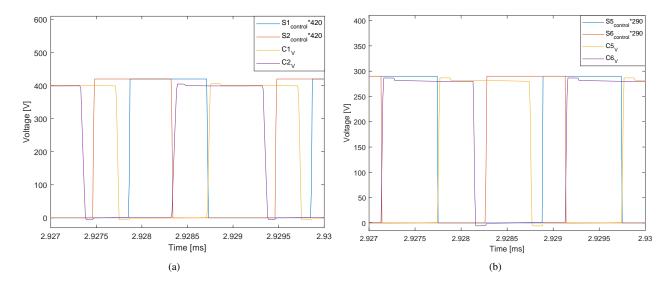

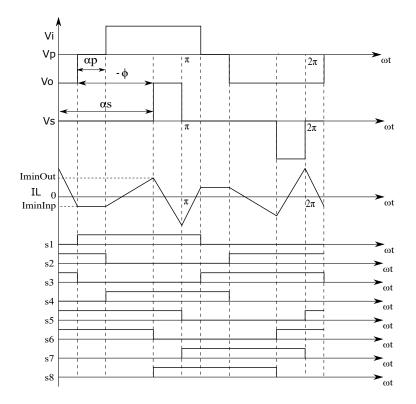

| 5.15Analog to digital conversions along the control loop.1146.1Top view of the whole charger.1186.2Schematic circuit to explain the need of the snubber capacitances.1186.3Delfino microcontroller time base counter.1196.4Current closed control loop.1216.5External system of the current control loop.1216.6Thermal measurements on the PQ5050 transformers.1226.7Thermal measurements on the PQ4040 transformer and switches.1237.8Buck and boost mode waveforms.1237.1Input and output bridge soft switching in boost mode with a leakage inductance of 16 [ $\mu$ H].1257.2Hard and soft switching in the input and output bridges respectively with L=25 [ $\mu$ H].1267.4Working waveforms and switching path in the case of single PWM control.1287.5Output power as a function of $\phi_f$ and $\alpha_p$ .1307.6Soft switching commutation in the input bridge at $\alpha_p$ .1317.8Hard and soft output bridge in the case of SPS and single PWM respectively.1327.9Working waveforms with single PWM in boost mode operation.1337.10Input and output bridge commutations in the output bridge at instant $\alpha_p$ .1377.13Equivalent circuit during the commutation in the input bridge at instant $\alpha_p$ .1377.14Working waveforms and switching path in the case of dual PWM control (buck mode).1367.15Liquivalent circuit during the commutation in the input bridge at instant $\alpha_p$ .137 </th <th>5.11<br/>5.12<br/>5.13<br/>5.14</th> <th>Output voltage step response in the cascade mode</th> <th>109<br/>110<br/>111<br/>112<br/>112<br/>113<br/>114<br/>114</th> | 5.11<br>5.12<br>5.13<br>5.14                                                                          | Output voltage step response in the cascade mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 109<br>110<br>111<br>112<br>112<br>113<br>114<br>114 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 7.2Hard and soft switching in the input and output bridges respectively with L=25 [ $\mu$ H].1267.3Hard switching commutations in the output bridge with SPS control.1277.4Working waveforms and switching path in the case of single PWM control.1287.5Output power as a function of $\phi_f$ and $\alpha_p$ .1297.6Soft switching commutation in the input bridge at $\alpha_p$ .1307.7Commutation in the output bridge.1317.8Hard and soft output bridge in the case of SPS and single PWM respectively.1327.9Working waveforms with single PWM in boost mode operation.1337.10Input and output bridge commutations in boost mode.1347.11Working waveforms and switching path in the case of dual PWM control (buck mode).1367.12Equivalent circuit during the commutation in the input bridge at instant $\alpha_p + \phi$ .1377.13Equivalent circuit during the commutation in the input bridge at instant $\alpha_p$ .1377.14Hard switching in the lagging leg of the input bridge and almost total soft switching in the output bridge.1397.15Voltage and current waveforms within ZVS in buck mode.1397.16Soft switching in both input and output bridges.1407.17Working waveforms and switching path in the case of dual PWM control.1407.14Working waveforms within ZVS in buck mode.1397.15Voltage and current waveforms within ZVS in buck mode.1407.17Working waveforms and switching path in the case of dual PWM control.140                                                                                                                                                         | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> </ul> | Top view of the whole charger.       Schematic circuit to explain the need of the snubber capacitances.         Schematic circuit to explain the need of the snubber capacitances.       Delfino microcontroller time base counter.         Delfino microcontroller time base counter.       Delfino microcontroller time base counter.         Current closed control loop.       Delfino microcontrol loop.         External system of the current control loop.       Delfino microcontrol loop.         Thermal measurements on the PQ5050 transformers.       Delfino microcontrol loop.         Thermal measurements on the PQ4040 transformer and switches.       Delfino microcontrol loop.         Buck and boost mode waveforms.       Delfino microcontrol loop. | 118<br>119<br>121<br>121<br>122<br>123<br>123        |

| 7.6       Soft switching commutation in the input bridge at $\alpha_p$ .       130         7.7       Commutation in the output bridge.       131         7.8       Hard and soft output bridge in the case of SPS and single PWM respectively.       132         7.9       Working waveforms with single PWM in boost mode operation.       133         7.10       Input and output bridge commutations in boost mode.       134         7.11       Working waveforms and switching path in the case of dual PWM control (buck mode).       136         7.12       Equivalent circuit during the commutation in the output bridge at instant $\alpha_p + \phi$ .       137         7.13       Equivalent circuit during the commutation in the input bridge at instant $\alpha_p$ .       137         7.14       Hard switching in the lagging leg of the input bridge and almost total soft switching in the output bridge.       139         7.16       Soft switching in both input and output bridges.       140         7.17       Working waveforms and switching path in the case of dual PWM control.       140                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7.2<br>7.3                                                                                            | Hard and soft switching in the input and output bridges respectively with L=25 [ $\mu$ H]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 126<br>127                                           |

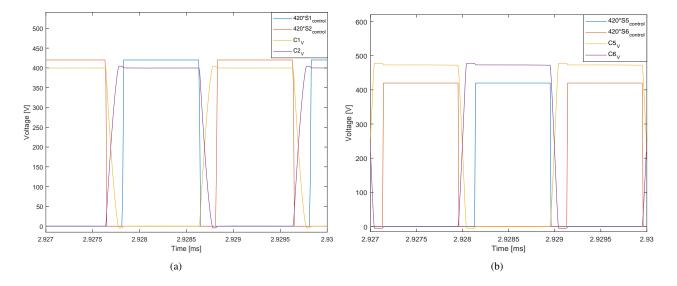

| 7.8       Hard and soft output bridge in the case of SPS and single PWM respectively.       132         7.9       Working waveforms with single PWM in boost mode operation.       133         7.10       Input and output bridge commutations in boost mode.       134         7.11       Working waveforms and switching path in the case of dual PWM control (buck mode).       136         7.12       Equivalent circuit during the commutation in the output bridge at instant $\alpha_p + \phi$ .       137         7.13       Equivalent circuit during the commutation in the input bridge at instant $\alpha_p$ .       137         7.14       Hard switching in the lagging leg of the input bridge and almost total soft switching in the output bridge.       139         7.16       Soft switching in both input and output bridges.       140         7.17       Working waveforms and switching path in the case of dual PWM control.       140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7.6                                                                                                   | Soft switching commutation in the input bridge at $\alpha_p$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 130                                                  |

| 7.11 Working waveforms and switching path in the case of dual PWM control (buck mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7.8<br>7.9                                                                                            | Hard and soft output bridge in the case of SPS and single PWM respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 132<br>133                                           |

| 7.13 Equivalent circuit during the commutation in the input bridge at instant $\alpha_p$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7.11                                                                                                  | Working waveforms and switching path in the case of dual PWM control (buck mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 136                                                  |

| 7.16 Soft switching in both input and output bridges.       140         7.17 Working waveforms and switching path in the case of dual PWM control.       140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7.13                                                                                                  | Equivalent circuit during the commutation in the input bridge at instant $\alpha_p$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 137                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7.15<br>7.16<br>7.17                                                                                  | Voltage and current waveforms within ZVS in buck mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 139<br>140<br>140                                    |

## Abstract

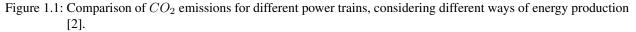

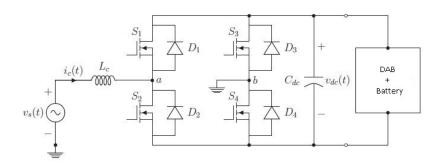

Nowadays electric mobility is arousing a lot of interest from the major car manufacturers. Despite the fact that outboard fast direct current chargers represent the most immediate response to the problem of recharging the batteries, AC on-board chargers are of fundamental importance to guarantee the use of the domestic infrastructure. After the conversion of the voltage from AC to DC, carried out by the power factor corrector, a DC/DC converter is necessary to be able to charge the battery with the desired current value.

In this context, the dual active bridge converter represents a good solution since it allows to satisfy the aforementioned request, guaranteeing the minimum bulk, the minimum number of components and galvanic isolation.

In this thesis the study of the aforementioned converter operating at a frequency of 500 [kHz] is presented; the realization of the high frequency transformer with integrated leakage inductance is documented in detail and finally a possible alternative to the classic control with single phase shift between the two active bridges is described, in order to extend the range of soft switching even at small levels of transmitted power, especially necessary to accomplish the final stage of the battery charging process, during which the load current becomes very small.

### Sommario

Oggigiorno la mobilità elettrica sta suscitando grande interesse da parte dei maggiori costruttori di veicoli elettrici. Malgrado le colonnine fast charge in corrente continua rappresentino la risposta più immediata al problema di ricarica delle batterie, i caricatori di bordo in alternata sono di fondamentale importanza per sfruttare la capillare rete di alimentazione domestica.

In seguito alla conversione da AC in DC che è realizzata mediante il power factor corrector, un convertitore DC/DC è necessario per essere in grado di ricaricare la batteria con la corrente desiderata. In tale contesto il convertitore a doppio ponte attivo rappresenta un'ottima soluzione poiché permette di soddisfare la sopracitata richiesta, garantendo un minimo ingombro, un minimo numero di componenti e l'isolamento galvanico.

In questa tesi si affronta lo studio del suddetto convertitore, operante alla frequenza di 500 [kHz]; viene inoltre presentata la progettazione del trasformatore ad alta frequenza ed infine viene descritta una possibile alternativa al classico controllo con singolo sfasamento tra i due ponti attivi, al fine di estendere il funzionamento in soft switching anche con piccoli livelli di potenza trasmessa, in particolare durante l'ultimo stadio di carica della batteria.

## **1** Introduction

For more than a century the development of industrialized countries has been dependent upon fossil fuels. Current trends in energy supply are not more sustainable and climate changes are starting to become irreversible.

Governments are focusing on the major fields of air pollution, among them the transportation sector. In the next few years it'll be necessary to think back the way through which people can move. Electrical energy use in the transport sector is considered the best solution in order to reduce the mainly exhaust gasses that cause greenhouse effect, especially  $CO_2$  and  $NO_x s$ , the last ones are generated in internal combustion engines that work at high pressure ratio, like the diesel ones.

With respect to traditional engines, electric vehicles, especially those that rely only on batteries supply, can reach a plug-to-wheel efficiency that is more than the double; although all these good perspectives, penetration rates of electric vehicles are still too low. The reason could be search on the following drawbacks:

- high battery cost;

- range anxiety;

- a narrow spreading of charging infrastructures, especially along the highway;

- long charging time.

Decarbonizing transport is providing to be one of the largest research and development projects of the 21st century [1].

### 1.1 Energy efficiency

The great driver for electric mobility (beyond climate change) is the capability to operate locally without creating emissions, this aspect is very important, especially in big cities: it's known that a central plant, to product the energy required for a fleet of cars, releases into the air a smaller quantity of pollutants with respect a myriad of small widespread burners, in which it's impossible to set powerful electrostatic filters. Hence the growing amount of electric vehicles can give a big "footprint" to improving air quality in urbanized regions.

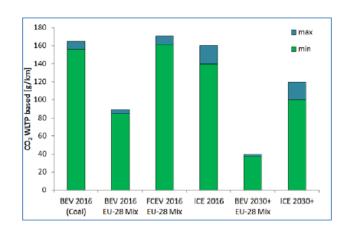

Taking a look at the histogram in figure 1.1, it's clear that a real climate benefit in the shifting from oil to electricity is reached only when renewable energy sources will get a big slice in the circle of the production sources; on one hand with a proper energy baking, it will be possible to go below 50  $[gCO_2/km]$  in WLTP cycle, but on the other hand relying exclusively on coal exploitation, the pollution caused by electric vehicles overcomes the top boundary of combustion engines.

An important aspect of electric vehicles has to be found in their ability to get advantages from kinetic energy: despite combustion that is irreversible, during breaking and downhill, inverting the sign of the current in the windings, electric motors can act like a "brake forward" and so they are able to recover a certain amount of this energy and act like generators, while maintaining the same rotation direction; in this way a considerable energy saving can be reach not only in battery electric vehicles (BEVs), but especially in plug-in hybrid electric vehicles (PHEVs), since the energy recovered can be used in the following acceleration, leaving the combustion engine to work in a range of maximum torque and minimum fuel consumption.

### 1.2 Challenges

As written above, the reasons for the scepticism of public opinion in face of electric mobility relied on economic and physical boundaries. To increase the available range, a bigger battery stack is needed but it would cause an increasing of the weight and subsequently a decreasing of efficiency.

Fast charging is another requirement: at the beginning of this year Tesla presented the third generation of its Superchargers that can reach a peak charging power of 250 [kW], allowing to obtain 120 [km] in just five minutes (of course the power will decrease as the charge status of the battery increases).

In order to achieve the goal of a widespread electron mobility it's necessary to obtain important developments in the following fields:

- energy storage systems;

- drivetrain technologies;

- grid integration.

The work of this thesis is focused on one power electronic system that allows an efficient energy management and it's connected downstream an active power factor corrector converter: the DC/DC isolated dual active bridge converter.

### 1.3 Automotive applications of DAB converter

The reasons for what it has become necessary to put more and more effort on the developing of electric mobility can be summarized in three points:

- shrinking of fossil fuel reserves;

- growth of word population;

- increasing of welfare also in poor countries, that means a large number of people would like to access the exploitation of energy to ensure economic growth.

The energy demand can be differentiated into three major "subjects": civil, industrial and transportation activities. Apart from increasing the energy efficiency, it's not possible to make heavier changes in the first two groups, instead it

| Power train                              | Electric | Combustion |

|------------------------------------------|----------|------------|

| Energy consumption tank to wheel [Wh/km] | +30      | +400       |

| Energy consumption well to tank [Wh/km]  | +180     | 430        |

Table 1.1: Different energy demands.

Figure 1.2: Schematic block of the entire charger.

results possible to re-design the third one, bringing interesting amount of energy saving and consequently air pollution decreasing.

In order to understand if the electrical technology is the right direction to be followed, a short energy balance is mandatory: on one hand in internal combustion engines, beyond road energy and power train consumptions, there are also losses regarding the extraction, refining and transportation of oil; on the other hand in battery electric vehicles (BEVs), besides traction energy, losses occur in the transmission and distribution electric grid.

Below there's a fast computation that underlines the milestones of the two different propulsion systems: consumptions are distinguished in two categories, id est from tank to wheel (assuming that tank represents both fuel sink and battery stack) and from well to tank (assuming that well stays also for electric energy plants).

The average propulsion energy required by a C segment car is about 120 [Wh/km]. Through the values listed in table 1.1, making a sum it appears that the total energy well to wheel is equal to 330 [Wh/km] for BEVs and 950 [Wh/km] for ICEs [3], hence there is a saving of about 65 %. In the middle there are hybrid electric vehicles that would be the most popular in the next few years, also remembering that from 2021 all cars manufacturers should respect the average limit of 95 [gCO<sub>2</sub>/km]. In all electric vehicles the dual active bridge DC/DC converter plays a fundamental role in the charging and discharging process of the battery, allowing galvanic isolation and managing the difference voltages between battery and rectified DC voltage. Picture 1.2 presents all the voltage conversions that occur inside the charger: the AC voltage at the input port is rectified by means of the PFC converter, then the DC voltage is modified by the dual active bridge in order to get the suitable magnitude to charge the battery stack. The following paragraph describes an ancillary use of the first stage of the charger, instead the dual active bridge will be discussed in details in the second chapter.

#### 1.3.1 V2G technology

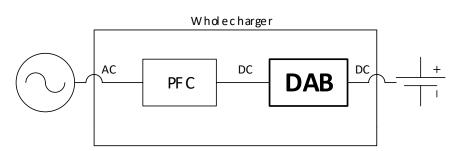

The whole charger consists of two stages: a power factor corrector (PFC), which interfaces with the grid, and a dual active bridge, that allows to manage the DC voltage between the DC link and the battery. Thanks to this particular architecture it's possible not only to charge the battery, but also to discharge it, for traction aim or to fulfil the so called "vehicle to grid".

The daily power demand plot has two humps that the network manager has to provide in order to ensure the stability of the electric system. EVs store a big amount of energy in their battery stacks and for this reason they could be a good

Figure 1.3: Full active bridge AC/DC converter.

solution to smooth these two humps of the power demand trend; however some researches have demonstrated that this further exchange of energy, increasing the number of charging/discharging processes, will decrease the lifetime of the traction battery.

On the other hand it's rising the idea to employ the chargers inside electric vehicles to compensate locally the reactive power in the transmission grid. It's known that for long distance, the reactive component (inductive one) of the transmission lines is higher than the resistive one, also considering that a big part of loads connected to the grid is of inductive nature. The reactive current doesn't contribute to the transmission of active power, but it just flows from one side to another, congesting the grid and increasing the losses on transformers. For these reasons the possibility to produce at the distribution level and locally the reactive power required by passive loads is reaching a lot of interest. Through a punctual management of the reactive power it's possible to accomplish some of the bigger problems that afflict the grid stability: voltage and frequency regulation.

The on board charger can provide positive or negative reactive power independently from the state of charge of the battery, not afflicting its lifetime. The first stage of the chargers is drawn in figure 1.3. To make an analysis of the circuit it's possible to refer to an equivalent simplified one, considering only the grid and the input converter voltages (respectively  $v_s$  and  $v_c$ ), interleaved by the inductance  $L_c$ . The last one takes into account not only the transmission lines inductance, but also that one used downstream the power factor corrector that is used to limit the current oscillation in the DC bus.

Looking at the full bridge from right to left side, the DC voltage of the capacitances is the input parameter, instead the AC voltage, made through a PWM modulation, represents the output parameter. Considering a switching frequency quite high, the passive filters on both sides of the converter could be regarded so small that they don't absorb power. Thinking the grid voltage perfectly sinusoidal, since the transfer of power between the two subjects (the grid and the converter) is possible just among isofrequential quantities, all the harmonics generated by the switching can be neglect and it's possible to focus on fundamental:

$$v_s(t) = \sqrt{2V_s \sin(\omega t)} \tag{1.1}$$

Since normally the grid acts like the tank of energy, the voltage downstream the inductance  $L_c$  has to lag  $v_s(t)$  of an angle  $\delta$  that it's called "load angle":

$$v_c(t) = \sqrt{2}V_c \sin(\omega t - \delta) \tag{1.2}$$

The source voltage  $v_s$  and the charger voltage  $v_c$ , being at the same frequency, can be expressed as phasors:

$$\mathbf{V}_{\mathbf{s}} = \sqrt{2} V_{\mathbf{s}} e^{-j\pi/2} \tag{1.3}$$

$$\mathbf{V_c} = \sqrt{2}V_s e^{-j(\pi/2 + \delta)} \tag{1.4}$$

The phasor of the current  $I_c$  that flows through the inductor is given by the ratio between the inductance voltage and the respective impedance. The final expression of the current in time domain is given by:

$$i_c(t) = \sqrt{2I_c \sin(\omega t - \theta)} \tag{1.5}$$

in which

$$I_{c} = \frac{1}{\omega L_{c}} \sqrt{V_{c}^{2} + V_{s}^{2} - 2V_{c}V_{s}cos(\delta)}$$

(1.6)

and

$$\theta = \tan^{-1}\left(\frac{V_s - V_c \cos(\delta)}{V_c \sin(\delta)}\right) \tag{1.7}$$

Knowing the expression of the line current  $i_c(t)$  and the voltage  $v_s(t)$  it's possible to compute the instantaneous power delivered by the grid:

$$p_s(t) = v_s(t)i_c(t) = \sqrt{2}V_s sin(\omega t) \cdot \sqrt{2}I_c sin(\omega t - \theta)$$

=  $V_s I_c cos(\theta) - V_s I_c cos(2\omega t - \theta)$  (1.8)

The instantaneous power through the coupling inductance is equal to:

$$p_L(t) = v_L(t)i_c(t) = L\frac{di_c}{dt}i_c(t)$$

(1.9)

Substituting the expression (1.5) into the equation of the inductance power (1.9), it results:

$$p_L(t) = \omega L_c I_c^2 \sin(2\omega t - 2\theta) \tag{1.10}$$

Finally, taking into account equations (1.8) and (1.10) it's feasible to compute the instantaneous power in the AC side of the converter:

$$p_c(t) = p_s(t) - p_L(t) = V_s I_c \cos(\theta) - V_s I_c \cos(2\omega t - \theta) - \omega L_c I_c^2 \sin(2\omega t - 2\theta)$$

$$(1.11)$$

Like shown in equation (1.11), the instantaneous charger input power consists of two terms: the first one at the grid frequency is the average power, the second one at a double frequency is the ripple power. Focusing on the ripple contribute, it's possible to refer both terms to a sinusoidal waveform (since they have the same frequency) and calculate the module of this power component:

$$P_{ripple} = \sqrt{(V_s I_c)^2 + (\omega L_c I_c)^2 - 2\omega L_c V_s I_c^3 sin\theta}$$

(1.12)

The active, reactive and apparent power can be express in function of the load angle  $\theta$ :

$$P_s = V_s I_c \cos(\theta) \tag{1.13}$$

$$Q_s = V_s I_c \sin(\theta) \tag{1.14}$$

$$S = V_s I_c \tag{1.15}$$

Substituting the equations from (1.13) to (1.15) in (1.12), the module of the ripple input charger power results function of the reactive power:

$$P_{ripple} = \sqrt{S^2 + (\omega L_c \frac{S^2}{V_s^2})^2 - 2\omega L_c \frac{S^2}{V_s^2} Q_s}$$

(1.16)

The amplitude of the ripple in the input power is directly linked to the sign of the reactive power of the source: if the full bridge converter absorbs an inductive reactive power (hence it delivers capacitive reactive power to the grid) the ripple will be smaller, contrariwise if the converter absorbs a capacitive reactive power (so it delivers inductive reactive power to the grid), the ripple will be greater. The sign of the reactive power absorbed by the charger depends on the modules of the grid and converter voltages: if  $V_s$  is greater than  $V_c$ ,  $Q_s$  will be positive and the PFC looks like an inductor, otherwise it will be negative and the full bridge acts like a capacitance. Dividing the ripple power by the working pulsation (at a double frequency with respect that one of the grid) gives the module of the energy ripple which is present in the DC link supported by the capacitances:

$$E_{ripple} = \frac{1}{\omega} \sqrt{S^2 + (\omega L_c \frac{S^2}{V_s^2})^2 - 2\omega L_c \frac{S^2}{V_s^2}} Q_s$$

(1.17)

Considering the frequency of the energy ripple, the maximum variation of the energy stored by the capacitor bank corresponds to:

$$E_{\Delta cap} = \frac{1}{2}C(V_{dcmax}^2 - V_{dcmin}^2)$$

(1.18)

Equating the two energy equation (1.17) and (1.18) it's possible to get the minimum required value of capacitance at the DC link of the charger to accomplish the task of the local reactive power compensation.

The capacitance bank in the laboratory charger consists of four Nichicon capacitances connected in parallel in order to get a total amount of 1560 [ $\mu$ F], a reasonable value to make this charger suitable also for the aforementioned ancillary aims (the minimum and maximum value of the DC link voltage are respectively 380 [V] and 420 [V]).

It has to be outlined that the required capacitance value directly depends on the total inductance  $L_c$ . Taking into account all the inductive objects connected to the grid, this value could be quite big: for this reason the v2g reactive power compensation has a positive impact only if a large number of EVs accomplish this task.

Since the aim of this thesis is focused on the study of the DC/DC converter and not on the PFC stage, the vehicle to grid operation won't be analyzed anymore; this short section has been necessary just to outline that a possible use of the EVs as active subjects towards the electric system has to be taken into account in the design of the charger, since the reactive power could create instabilities downstream the AC/DC conversion.

| Parameters                     | Si   | GaN  | SiC  |

|--------------------------------|------|------|------|

| Band gap $[eV]$                | 1.12 | 3.39 | 3.26 |

| Critical field $E_c [MV/cm]$   | 0.23 | 3.3  | 2.2  |

| Electron mobility $[cm^2/Vs]$  | 1400 | 1500 | 950  |

| Permittivity                   | 11.8 | 9    | 9.7  |

| Thermal conductivity $[W/cmK]$ | 1.5  | 1.3  | 3.8  |

Table 1.2: Properties of different semiconductors

### 1.4 GaN

#### 1.4.1 Why to use gallium nitride

Before the coming of power electronic switches, all the energy management was passive: resistors were used to regulate the speed of a motor and in this way it was possible, for example, to regulate the quantity of fluid that a pump could manage; all the components were very heavy and bulky, since the working frequency was that one of the grid. Through switching semiconductor devices, it became possible to manage the energy flow in a more efficient way, changing directly the module of voltage and current applied to electric motors and electronic devices. Increasing the working frequency means reducing the weight and volume of power electronic converters, ensuring both efficiency and reliability. For over three decades mosfets have improved their capabilities, but since the last years the rate of improvement has slowed, because this technology has almost got its theoretical boundaries.

The requirement to get further improvements, in order to increase the working frequency and ensure the capability of withstand high voltage, involves researchers to investigate new materials that could substitute silicon and silicon carbide in the manufacturing of field effect transistors. Semiconductors used in power conversion have to ensure:

- efficiency;

- reliability;

- controllability;

- cost effectiveness.

In order to make a comparison between different kinds of semiconductor, there are some parameters that have to be taken into account, especially band gap and critical field. The crystal parameters contained in table 1.2 make it possible to understand because gallium nitride can be superior than other semiconductors. The band gap of a semiconductor is related to the strength of its bonds inside the crystal lattice: an higher value can be translated in the capability of material to work with high temperatures and ensure lower leakage currents.

$$V_{br} = \frac{1}{2} w_{drift} E_c \tag{1.19}$$

A consequence of strong chemical bonds is an higher electric field needed to cause avalanche breakdown. The breakdown voltage  $V_{br}$  is proportional to the width of the drift region  $(w_{drift})$ , i.e. the region low doped, as it can be seen in eq. (1.19). In the case of GaN and SiC, the drift region can be 10 times smaller than in silicon for the same breakdown voltage.

In order to support a such big electrical field, it's necessary that the majority carriers are depleted away. Assuming an N-type semiconductor, it's possible to use the Poisson's equation to calculate the number of electrons between the

Figure 1.4: Performances schematic plot of Si, SiC and GaN.

two terminals of the device (drain and source):

$$qN_D = \xi_o \xi_r \frac{E_c}{w_{drift}} \tag{1.20}$$

In the equation (1.20) q is the electron's charge  $(1.6 \cdot 10^{-19} \text{ coulombs})$ ,  $N_D$  is the number of electrons contained in the volume,  $\xi_o$  and  $\xi_r$  are respectively the vacuum and relative permittivity. Since the critical electric field inside gallium nitride devices can be 10 times bigger than inside silicon ones, it's possible to design the electrical terminals 10 times tighter, hence the number of electrons can be 100 times greater and this one is the reason for what GaN and SiC overcome Silicon in power conversion. The wide band gap semiconductors result in devices with lower on-resistance  $R_{on}$  and switching losses. Unfortunately, as can be seen in figure 1.4 GaN shows a lower thermal conductivity rather than SiC, but it's superior for what concern high-efficiency and high-frequency possibilities of working.

$$R_{DS_{on}} = \frac{w_{drift}}{q\mu_n N_D} \tag{1.21}$$

The theoretical on resistance is proportional to the width of the drift region (see (1.21), where  $\mu_n$  is the electrons' mobility).

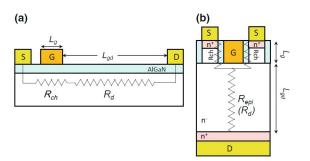

#### 1.4.2 Two dimensional electron gas

The lattice of gallium nitride has a hexagonal structure (see figure 1.5). Since it's very stable, this material can work with high temperatures without destroying itself; furthermore it has some piezoelectric properties that allow to create a small electric field when there's a strain applied.

In order to create a conduction path, it's necessary to build up a heterojunction, for example facing a layer of GaN with another one of AlGaN. In this way a strain will grow at the interface of the two layers and a two dimensional electron gas (2DEG) appears. Applying an external electron field, it's possible to almost "short-circuit" the drain and source, creating a path with high concentration and high mobility of electrons, that causes a negligible voltage drop during switch conduction (see figure 1.6).

Figure 1.5: Crystal lattice of GaN.

Figure 1.6: Two dimensional electron gas under external field.

#### 1.4.3 Depletion and enhancement mode

Nowadays most of the GaN devices available are lateral heterojunction field-effect transistors (HEMTs); they are rated to work with voltages up to 600-650 [V]. As can be seen in figure 1.7 both source and drain terminals pierce through the AlGaN layer, in order to almost create an ohmic contact with the 2DEG. The substrate is typically made of Si, sapphire and other materials; it's necessary also to create a buffer layer between the substrate and the GaN layer. After this small description, it's clear that the HFET is inherently a depletion-mode device and so, without applying any negative voltage at the gate, with respect to drain or source potential, the two external terminals are normally "short-circuited". This behaviour is not desirable for voltage-source converters, because it creates very big circulating current at the start up of the device if no negative voltage is before applied to the gate.

In order to overcome this disadvantage, researchers and manufacturers put a lot of effort in the design process, in order to modify the internal structure of the switches and make them normally off at "rest" position. These devices are called enhancement-mode transistors. Principally there are four popular structures to create these desirable devices: recessed gate, pGaN gate, cascade and implanted gate.

The first topology is based on the simple idea that, etching the thickness of the AlGaN layer, the piezoelectric effect will decrease and hence the bias voltage is easily smaller than the built-in voltage of the Schottky gate metal and

Figure 1.7: Depletion-mode lateral GaN HFET.

Figure 1.8: Schematic section of a pGaN enhancement transistor.

Figure 1.9: Cascade hybrid configuration and operating stages.

in this way it's possible to deplete the region below the gate surface, interrupting the short path created by the high concentration of electrons.

The second topology is based on the same idea of the first one, but instead of decreasing the natural piezoelectric field induced in the interface between the two layers of AlGaN and GaN, it's put a p-type GaN layer over the AlGaN one and over it there's the metal gate. Since the positive charges of this doped layer have a built-in voltage greater than that one generated by the piezoelectric effect, the 2DEG is split in the two opposite side of the gate surface, making impossible a current flow without applying a positive voltage between gate and source, as can be seen in figure 1.8.

The third way to get a normally off device is the so called "cascade hybrid mode". In the cascade mode two series transistors are required (figure 1.9): the first one has a bias voltage and the second one is driven by means of a pulse signal. Following the stages shown in the aforementioned figure, when Q2 is in the off state, id est the drive signal is null, it appears a sort of very big resistance and so, whatever current will flow through the depletion-mode GaN HFET (Q1), it will generate an increasing of the voltage. Meanwhile, as the pin source voltage goes up, that one between gate and source falls down, until when it becomes smaller than the threshold voltage ( $V_{gs} < V_{th}$ ) and so also the first transistor will turn off. In this way we could identify the low voltage mosfet (Q2) like a master and the HEFT like a slave (Q1).

When a positive pulse is applied on the gate of Q2, the resistance between its drain and source terminals falls down and hence the potential on the source side of Q1 becomes like the ground one. Applying the opportune bias voltage on the gate of the HEFT,  $V_{gs}$  grows over  $V_{th}$  and so there's a flow of current, but only in presence of a positive bias voltage in the mosfet Q2 (enhancement mode transistor). This configuration allows to design very fast switches: taking a look at

Figure 1.10: Schematic circuit during conduction of low voltage mosfet.

the first transistor Q1 (figure 1.9), there's a bias voltage applied on the gate terminal, but the control signal is applied by the source terminal (in this way it's possible to change the potential of the source terminal), so it's a quite different control technique rather than standard one.

$$C_{Mill_{PWM}} = C_{gd} \left(1 + \frac{V_{in}}{V_{qs}}\right) \tag{1.22}$$

In normal transistors there are two parassitic capacitances between gate-source and gate-drain; the last one has a significant impact on the commutation behaviour, since Miller's effect appears. This effect causes that  $C_{gd}$  seems bigger than in reality, depending on the voltage gain, as can be seen in equation (1.22), that appears like the capacitance behaves in the same way of a boost converter. With a very large capacitance it's necessary a big amount of charges in order to charge  $C_{gd}$  and  $C_{gs}$ , furthermore these capacitances are not linear and their modules change with voltage changing. This gain in the gate to drain capacitance is due to the so called "phase reversal": when a positive gate to source voltage is applied at control terminal, the drain to source voltage falls down and this is the reason for the positive gain in the Miller equation (1.22). On the other hand, when the control pulse is given through the source terminal of the depletion mode transistor, it appears the circuit shown in figure 1.10. In this case the capacitance  $C_{gs}$  is grounded.

$$C_{Mill_{PWM}} = C_{gd} \left(1 - \frac{V_{in}}{V_{gs}}\right) \tag{1.23}$$

$$C_{Mill_{PWM}} = C_{gd_{Q2}} \left(1 + \frac{\Delta V_d}{V_{gs}}\right) \tag{1.24}$$

In this particular case, the Miller capacitance becomes quite small, since the voltage gain is not more added (see equation (1.23)) due to the fact that there isn't the "phase reversal" phenomenon; as a result the charge required to charge and discharge the parasitic capacitances is approximately that one of the  $C_{oss}$ , hence enough small to guarantee a high switching frequency. Anyway, the low voltage mosfet Q2 is still driven with standard technique (pulse inside the gate), but the voltage swing at its drain terminal (linked in series with the source terminal of the GaN transistor) is quite small, since the maximum voltage variation that can occur at the input of the second transistor is equal to the threshold voltage of the GaN HEFT. Thanks to the small voltage oscillation at the drain terminal of the common mosfet, the resultant Miller capacitance between drain and gate doesn't suffer the voltage gain, since the last one is very small, like stated in equation (1.24). It's important to underline that, in order to get high switching frequency, the stray

inductances have to be reduced as minimum as possible, otherwise, since in the circuit there are high rate of current variations, the voltage swing in the drain terminal couldn't be any more negligible. Since the on resistance  $R_{ds_{ON}}$  in the GaN HFET increases with the increasing of the voltage, the cascade mode is convenient when the working range of voltage is above 200 [V], in this way the added mosfet resistance will be just 3% of the total resistance.

The fourth topology establishes to deplete the two dimensional electron gas by putting some negative fluorine atoms inside the AlGaN layer: in this way the transistor becomes normally off and only applying a positive voltage through the Schottky gate it's possible to reconstruct the very high conductivity electron path.

#### 1.4.4 Bidirectional current flow

In a conventional Si mosfet the current can change its direction through the path created by the p-n junction. The GaN HEFT hasn't got any body diode, but the bidirectional way is guaranteed by its symmetric structure. Differently from other enhancement mode devices, in the cascode mode, when the direction of the current changes, the body diode of the low voltage Si mosfet turns on and consequently also the GaN transistor turns on, but once the current starts to flow inside the mosfet, there's a peak due to the reverse recovery charge, however this spike of current expires in a narrow time and it's vary order of magnitude smaller than the spikes of current that occur in power mosfet.

In the GaN enhancement HEFT the electron channel is built up when the voltage across gate and source exceeds the threshold one; furthermore it is restored also when the voltage among drain and gate overcomes its own threshold one,  $V_{th_{ad}}$ , approximately the same between gate and source.

When the output of the device is reverse biased, the gate to drain voltage becomes:

$$V_{gd} = V_{gs} - V_{ds}.$$

The voltage drop in self commutated reverse conduction mode (SCRC) is computed as:

$$V_{sd} = V_{gd_{th}} - V_{gs} + I_d R_{sd_{rev}}$$

The reverse resistance between source and drain  $(R_{sd_{rev}})$  is usually higher than that one in the direct conduction mode and varies with the junction temperature  $T_j$ . Compared with the voltage drop that appears during the body diode conduction on a mosfet, the  $V_{sd}$  is quite higher (3-5 [V]) and for this reason the losses in reverse conduction mode could be excessive for long dead time, but the lack of a real body diode allows to ensure zero voltage switching condition also with small dead time.

#### 1.4.5 Variable on resistance

The breakdown voltage in the super junction devices is related to the distance between the external electrodes; since the on-resistance is directly proportional to the length of the drain-source path, it's clear that it depends linearly by the breakdown voltage.

The total resistance of the aforementioned path is given by the sum of the channel resistance,  $R_{ch}$ , and the drift region resistance,  $R_d$ .

$$R_{ch} = \frac{L_g}{W_g} \frac{1}{q\mu N_s} \tag{1.25}$$

$$R_{d} = \frac{L_{d}}{W_{g}} \frac{1}{q\mu N_{s}} = \frac{1}{W_{g}} \left(\frac{B_{v}}{E_{c}} \frac{1}{q\mu N_{s}}\right)$$

(1.26)

As can be seen in the equations (1.25) and (1.26), both contributes to on-resistance depend on design geometry parameters, in fact  $W_g$  is the gate width;  $L_g$  is the gate length;  $\mu$  is the electron mobility inside the two dimensional electron gas;  $N_s$  states the density of majority carriers.

Figure 1.11: Changing of  $R_{on}$  varying gate length, with  $E_c$  equal to 1 [MV/cm].

In figure 1.11 is represented the trend of different resistance contributes. Looking at the plot, it's possible to understand that  $R_{ch}$  and  $R_d$  have a different contribute on the value of  $R_{on}$ , depending especially by the breakdown voltage: in the low-voltage range  $R_{on}$  tends to the value of  $R_{ch}$ , instead in the high-voltage range  $R_d$  has the heavier effect. From this short analysis it emerges that decreasing the gate-length is useless in high-voltage range [4].

#### Low and high voltage device shrewdness

Decreasing on-resistance is one of the most important goal to be followed during the design of a power device, since it's related to device's efficiency. For what concern low-voltage working range, as said in the previous sentences,  $R_{ch}$ represents the major contribute to the total on-resistance. In a first approach it seems sufficient to decrease the gatelength, but in this way also the critical field  $E_c$  will be smaller and won't satisfy any more the requirement for blocking voltage. For this reason a minimum space between source and drain has to be ensured. From this point of view wide band gap semiconductors, like SiC and GaN have advantages with respect to Si, since the bigger specific  $E_c$  [V/µm] makes possible to miniaturize their structure, about 40 times smaller than Si devices. The most important aspect of miniaturizing is regarded the switching losses: with smaller devices, the charge required to charge and discharge the parasitic capacitances during each commutation is order of magnitude less, allowing for better efficiency and higher switching frequency than those ones obtained with band gap semiconductors. Since the on-resistance can be decreased also increasing the gate width, some attentions are involved in vertical structures, that can allow also higher range of voltage; these kind of devices are still at research step and not yet commercially available.

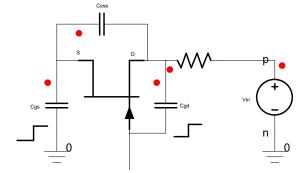

Figure 1.12: Switching power losses during turn-on (a) and turn-off (b) of a power device.

In high frequency converter one of the heavier "stones" on conversion efficiency is linked to switching losses, since conduction losses, thanks to small time period and low on-resistance, are negligible. As it's possible to see in figure 1.12, switching losses are linked to the contemporary presence of current and voltage. The switching power loss can be determined taking into account both voltage and current transition power losses ( $P_{Vt}$  and  $P_{Ct}$ ) and summing the two contributes like can be seen in the equation:

$$P_{sw} = P_{Vt} + P_{Ct} = \frac{1}{2} V_{BUS} I_L (t_{CR} + t_{VF}) f_{sw}.$$

In the aforementioned figure it emerges the slower slope of the gate-voltage during the switching time, which is linked to Miller's effect: as explained in previous paragraph, since the gate-drain capacitance  $C_{gd}$  is positively affected by the voltage gain, the time constant is smaller and hence the "reactivity" of the RC circuit becomes slower.

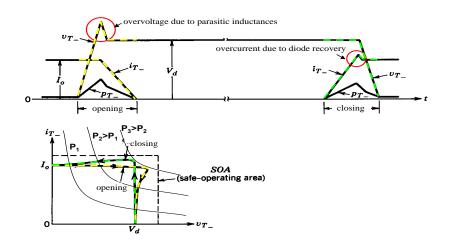

The other losses that occur in the enhancement mode HEMTs are regarded conduction in forward mode and during dead time. The first one can be computed taking into account the current that flows through the 2DEG and the total resistance of this "conduction pipe":