# UNIVERSITA' DEGLI STUDI DI PADOVA

Corso di Laurea Magistrale in Ingegneria Elettronica

a.a. 2015/2016

# Release and Verification of an Operating System for Testing e-Flash on Microcontrollers for Automotive Applications based on Multicore Architecture

**Studente**: Claudio Menin

**Matricola**: 1065593

Relatore: Ph.D. Prof. Andrea Cester

Correlatore Aziendale: Ing. Angelo De Poli

Tutor Aziendale: Ph.D. Ing. Giambattista Carnevale

Padova, 11 aprile 2016

# **Abstract**

The global automotive electronics industries are constantly growing as the cars produced contain an increasing number of electronic devices for active assistance to driving, safety controls, energy efficiency, passenger comfort and entertainment. Some future goals that we can mention are autonomous driving, gesture controls, 360° view parking assistance and so on. Safety is the keyword for these automotive systems and means to have electronic components high reliability. Infineon microcontroller division at Padua works to improve reliability and guarantee the quality of microcontroller flash memories. These last are actually tested by a firmware (single-core operating system Test-Application) called testware that aims to verify their proper functionalities through a long set of tests. The cost of these, on e-Flash memories, is high and highly dependent on the time employed in the tests. Due to the increase of number of electronic devices in cars, the size of flash memories increase more and more and then the company needs faster solutions to fully test these memories.

# **Table of Contents**

# Introduction

| 1 | Cor  | itext Analysis, Company Methodologies and Tools               | 1  |

|---|------|---------------------------------------------------------------|----|

|   | 1.1  | Infineon brief Presentation                                   | 1  |

|   | 1.2  | FTOS                                                          | 1  |

|   | 1.3  | Company's Methodology of Development                          | 3  |

|   | 1.4  | Testware Development Process                                  | 5  |

|   | 1.5  | Tools for Operating System Release and Testing                | 6  |

|   | 1.5. | 1 TASKING                                                     | 6  |

|   | 1.5. | 2 UDE                                                         | 7  |

|   | 1.5. | 3 JAZZ                                                        | 7  |

| 2 | Flas | sh Memories                                                   | 9  |

|   | 2.1  | Memories Introduction                                         | 9  |

|   | 2.2  | Single Flash Cell                                             | 10 |

|   | 2.3  | Flash Memory Architecture                                     | 13 |

|   | 2.4  | Flash Memory Defects and Tests                                | 15 |

| 3 | Sys  | tem on Chip Architecture                                      | 20 |

|   | 3.1  | Internal Buses                                                | 21 |

|   | 3.2  | On-Chip Debug Controller                                      | 22 |

|   | 3.3  | MMU                                                           | 23 |

|   | 3.4  | TriCore™ Core Architecture Overview                           | 26 |

|   | 3.5  | Context Management System                                     | 29 |

|   | 3.6  | System Timer and Interrupts Management                        | 31 |

| 4 | Оре  | erating System                                                | 32 |

|   | 4.1  | Why a Multi-core/Multi-task Functional Test Operating System? | 32 |

|   | 4.2  | Scheduler Module                                              | 36 |

|   | 4.3  | Multi-core Verify and Iterator Module                         | 39 |

|   | 4.4  | Test Results Merging                                          | 42 |

| 5 | Оре  | erating System Release                                        | 44 |

|   | 5.1  | Synchronization                                               | 46 |

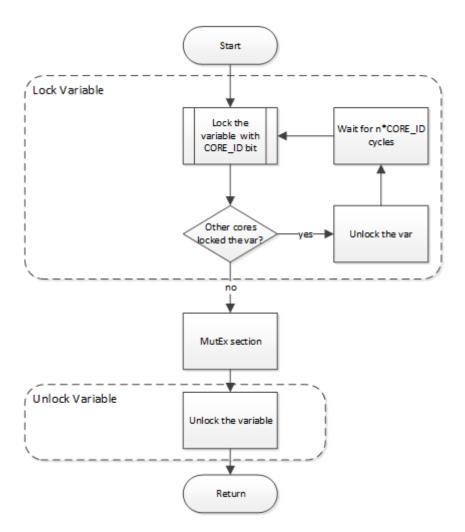

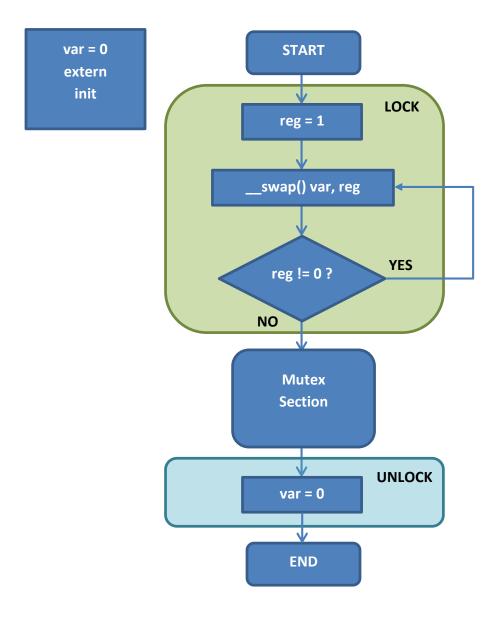

| Ç      | 5.1.1 | 1 Mutex                                    | 46  |

|--------|-------|--------------------------------------------|-----|

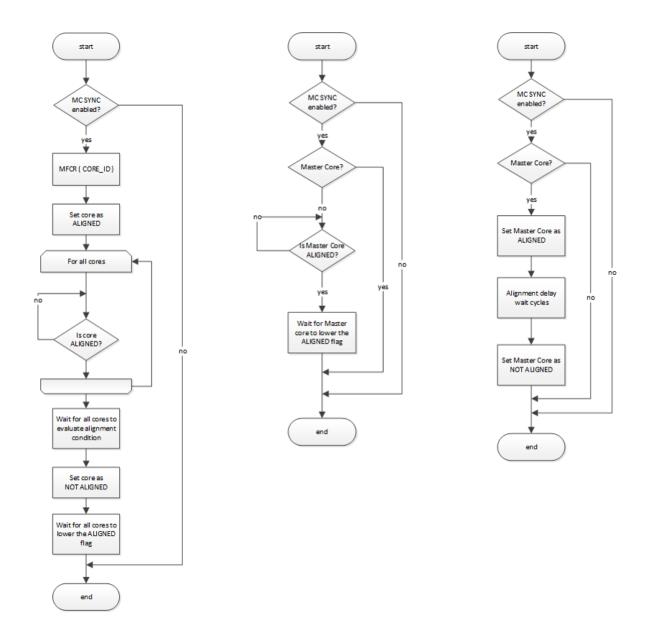

| į      | 5.1.2 | 2 Alignment Function                       | 55  |

| 5.2    | . (   | Code Cloning                               | 63  |

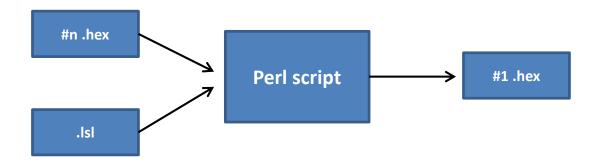

| į      | 5.2.1 | 2.1 The C build process                    | 64  |

| į      | 5.2.2 | 2.2 Code Cloning Requirements              | 68  |

| į      | 5.2.3 | 2.3 Feasibility Study                      | 68  |

| į      | 5.2.4 | 2.4 Reverse Engineering for Fixing Problem | 74  |

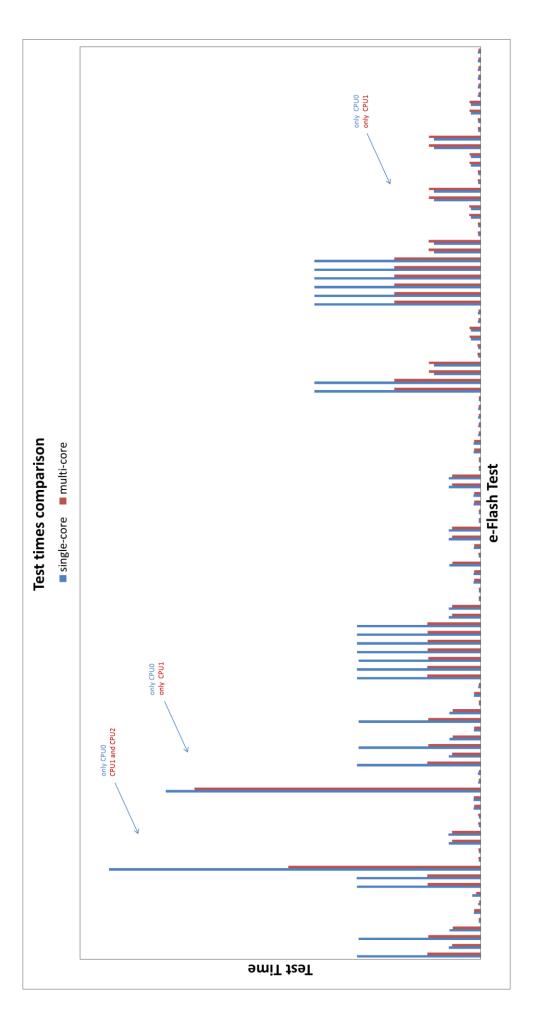

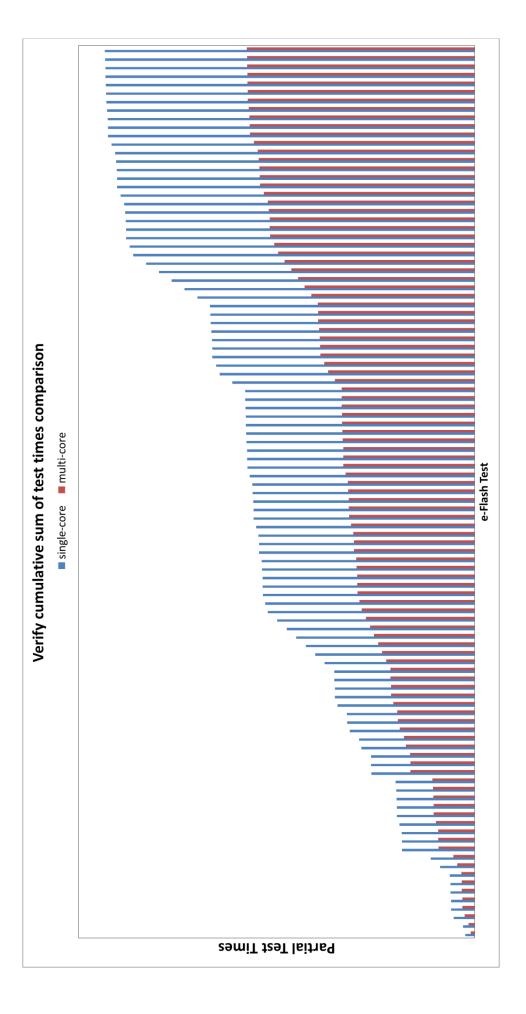

| 5.3    | ı     | Multi-Core vs Single-Core Measurements     | 76  |

| 6 9    | Sche  | neduler Characterization                   | 84  |

| 6.1    | l     | Measurements Results                       | 89  |

| 6.2    | . (   | Code Analysis                              | 91  |

| 6.3    | ,     | A New Concept for the Aligning Function    | 102 |

| 6.4    |       | New Aligning Function Implementation       | 104 |

| 7 (    | Cond  | nclusions                                  | 111 |

| 7.1    |       | Next Steps                                 | 112 |

| Appe   | ndix  | ix A                                       | 114 |

| Appe   | ndix  | ix B                                       | 117 |

| Biblio | grap  | aphy                                       |     |

# Introduction

The microcontroller-team challenge is to realize a fast method for testing e-Flash memories. The initial idea was a single-core *Functional Test Operating System* (FTOS) that checks autonomously with various tests the memory reliability. The increase of memory banks that must be analyzed lead to the idea of designing a multi-core multi-task FTOS, to decrease as much as possible the flash memory test time with parallel analysis and maximize the operating system throughput. Thanks to the studies of several thesis students and the determination of the MC team of Infineon Development Center in Padua we arrived today in a first implementation of this multi-core multi-task operating system.

The aims of the thesis are the new operating system release and the verification of multi-core and multi-task modes.

This thesis is divided into seven sections: first chapter focuses on the introduction to the working context explaining why we adopted an operating system to test the microcontroller flash memory, the company project development approach and the tools used in the analysis. The second, the third and the fourth chapters give a brief overview of the flash memories architecture, the microcontroller architecture and the operating system structure. These informations are then used in the next chapters: the fifth chapter focuses on my contribution to the operating system release with the implementation and the verification of new synchronization functions and the solution to the code cloning problem; at the end of the chapter there is the multi-core verification. The sixth chapter explains the multi-task analysis performed and proposes a solution to fix an issue found in the multi-task verification. The last chapter recaps the obtained results and lists the project next steps.

# 1 Context Analysis, Company Methodologies and Tools

#### 1.1 Infineon brief Presentation

The work presented in this brief document has been developed at the Infineon Technologies Development Center in Padua. Infineon Technologies is a German semiconductor manufacturer with headquarter in Munich founded in 1999 with more than 36,000 employees worldwide (as of Sep. 2015). Infineon focus areas are:

- Automotive (ATV)

- Industrial Power Control (IPC)

- Power Management & Multimarket (PMM)

- Chip Card & Security (CCS)

Infineon automotive market covers powertrain modules (engine and transmission control), comfort electronics (steering, shock absorbers, air conditioning etc.) and safety systems (ABS, airbags, ESP and so on). The product portfolio includes microcontrollers (MC), power semiconductors and sensors.

Padua Development Center activity in ATV MC sector is focused on embedded Flash testing in close collaboration with the partner sites of Villach, Munich and Singapore. The MC department is mainly split into a characterization team and a testware team. Product Engineering (PT) group works for characterization, validation and verification of device features and requirements. This group is involved in automotive microcontroller development activities, starting from first silicon analysis, till massive production support, trough customer validation, product qualification and testing support. Testware Engineers (TE) instead work on the development of software in order to speed up test execution and ideation of new test algorithms in order to increase test coverage.

#### **1.2 FTOS**

The quality and reliability required by the automotive industry are guaranteed by tight quality standards. The first approach used by the company to meet these standards for the test of e-Flash memories was the so called Build-In Self-Test (BIST), which is a main standard in many SoC modules. In this approach, a specific area on the dice is entirely dedicated to perform the desired tests on the target module. Anyway the BIST has several drawbacks, starting from silicon area occupation (consider that a flash module often occupies a huge percentage of the physical chip area), to the very low portability<sup>1</sup> of the designed test.

<sup>&</sup>lt;sup>1</sup> Portability is the capability of being used on different systems. In this particular case, the systems are different e-Flash memories.

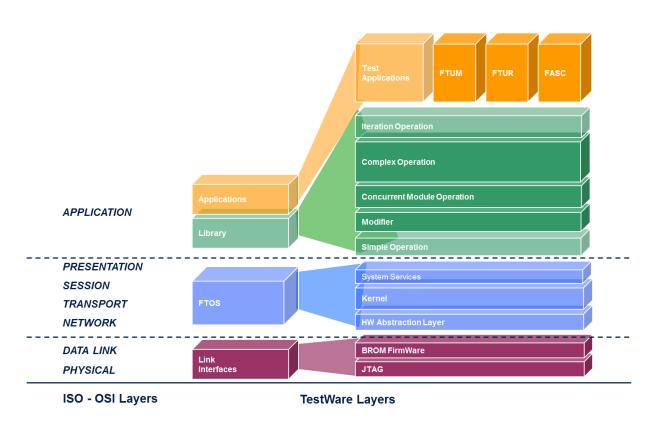

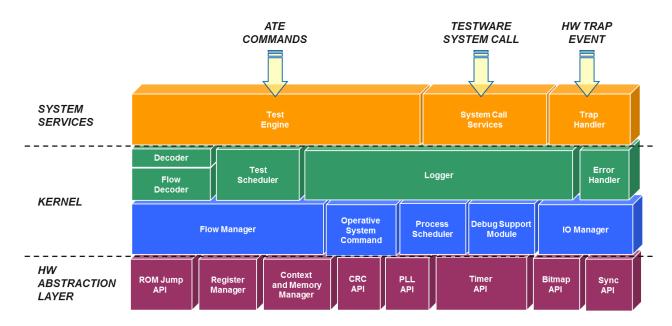

In 2002, Product and Test Engineers (PTE) chosen to use a different self-test for the SoC based on a software solution for embedded memories. This technique consists on using the DUT to test its memory itself, and this is possible only after a proper test of the necessary modules in the DUT (for instance, the CPUs, the RAM...). This is achieved by loading a dedicate test firmware (so called testware) into the already tested device's RAM. The testware is then executed by the processing units, which actually run the test. Testware fulfill quite well all the requirements of e-Flash testing, and the availability of DUT resources is powerful enough to support complex algorithms and to guarantee fast execution times. The PTE Padua team is owner of the library of e-Flash testware functions, and in 2007 the team developed a concept to standardize the testware layers [Figure 1], meeting given requirements to support different ATE machines and to have code easily portable among different DUT derivatives [1]. This was the birth of the Functional Test Operating System (FTOS).

Figure 1: The latest version of testware layers

But first, what is functional testing? It is a quality assurance (QA) process and a type of black-box testing that bases its test cases on the specifications of the software component under test. Functions are tested by feeding them input and examining the output, and internal program structure is not theoretically considered (contrary to white-box testing). Now that

we know a definition of functional testing we can define what FTOS is: it is a software layer to interface ATE and DUT, which is responsible for the management of activities and resources. FTOS is loaded in RAM at the beginning of the test flow and it supports execution of product family oriented Test Applications (TAs) containing functions and algorithms used for both e-Flash production test and e-Flash analysis purposes. TAs releases are scheduled quite often due to constant test coverage improvement or test costs reductions. This is a trade-off in software testing because optimal test coverage need time for design these tests and execute them (time is money) but an optimal coverage guarantee low post-production cost avoiding defects. FTOS releases are less frequent: they have to follow only ATE or DUT new hardware requirements. We can hence say that FTOS was born to standardize execution of Infineon microcontroller e-Flash tests and is meant to support several Test Applications execution over different products belonging to the same family. New generation products are introducing several cores into each microcontroller and memory space is rapidly increasing making the test time increase consequentially. These expansions are due to the increase of the power calculation demanded by the increase of the artificial intelligence into the cars and the space needed for processed data storing. In this sense the development of a multi-core version of the FTOS is required in order to:

- Reduce test time (thus reduce costs and upsurge the revenues) by making advantage of parallel memory access from different cores (timing requirement)

- Get closer to the actual multi-core usage of the costumer itself (test coverage requirement)

These two requirements justify the proposal of a multi-core OS.

FTOS is also a multi-task operating system. Multitasking permits to execute different processes simultaneously, alternating the execution of these. The change of process executed is called context switch, the switching decisions are taken by the scheduler and the dispatcher execute the switch operation. Multi-task permits to boost the throughput of the testing system.

#### 1.3 Company's Methodology of Development

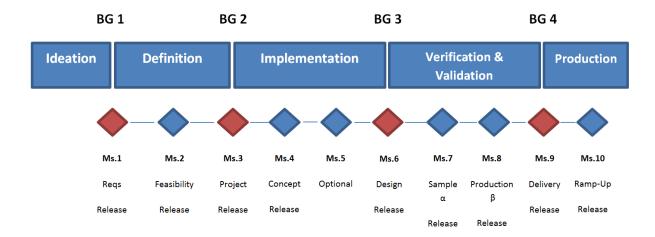

Infineon development process [2] is divided in 10 milestones which identify the current status of the product development. A milestone is the end of a stage that marks the completion of a work package or sub-phase, typically marked by a high level event such as completion, endorsement or signing of a deliverable document or high level review meetings. Five of these milestones are Business Gates (BG) that are management reviews of the business case and the technical risk assessment. They must have clear and visible criteria so that senior managers can make go/kill and prioritization decisions objectively.

**Figure 2: IFX Development Process**

Across these milestones we can identify five main phases:

- 1. **IDEATION:** The costumer and the developers study a new idea usually based on client's needs, market predictions and competitor's benchmarks

- 2. **DEFINITION:** The idea is synthetized to a concept, which is a collection of all system macro requirements (REQs, in short). The concept requires several team reviews, redefinitions, proposal and finally ends up with a specification for the implementation. The specification is than proposed again to the costumer, which have to agree before the implementation.

- 3. **IMPLEMENTATION:** The specifications are then implemented by the developers, who realize a prototype of the desired product. Implementation constraints that crops up because were not considered in the specs definition may stop the process development and require a redefinition of the original concept.

- 4. **VERIFICATION & VALIDATION:** to validate a product means to check whether it works properly respecting all requirements and specifications, in all operating situations and with all possible boundary conditions (e.g. inputs, software loading and executing, high/low temperature, supply voltage range). If some requirements are not achieved, the product is pushed back to Implementation phase.

- 5. **PRODUCTION:** when validation BG is passed, the production stars, delivering the product to the final costumer

The passage across different BGs is not unidirectional. The product development state can cycle many times among all phases, requiring a great communication from one team to another.

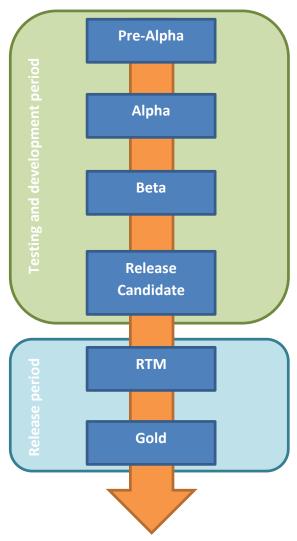

# 1.4 Testware Development Process

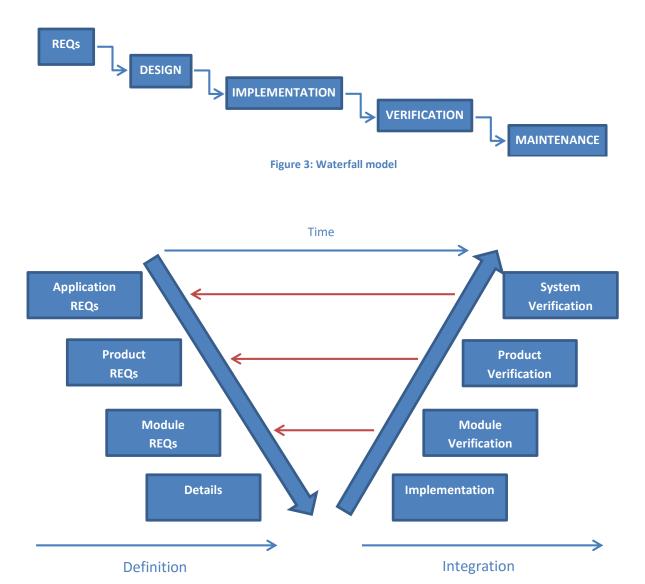

Testware process development is based on V-Model for software development structure. V-Model [Figure 4] is an extension of the waterfall model [Figure 3]. This last is simpler, should be used for developing small projects, has no overlap phases and finally is not suitable for projects where REQs have high risk of changes. If there is a change in one intermediate step, the subsequent steps must be repeated until the end of the process.

Figure 4: Testware V-Model

Instead of moving down in a linear way, the V-Model steps are bent upwards after the coding phase, to form the typical V shape. It is divided into:

- APPLICATION REQUIREMENTS: defines the external requirements of the product to be implemented

- 2. **PRODUCT REQUIREMENTS**: defines the system behavior

- 3. **MODULE REQUIREMENTS**: defines the macro architectural blocks which compose the system

- 4. **DETAILS**: the single module behavior is described in details (aka LLD standing for Low Level Design)

- 5. **IMPLEMENTATION**: all modules are transcript into the specific programming language

Any phase has an associated phase of testing in the shape. This permits to have a proactive defect tracking and avoids the downward flow of defects. Software is developed during the implementation phase (no early prototypes of the software are produced) and gives equal weight to development and testing. This structure guarantee a stable and ordered way of work compared to agile approaches, losing in flexibility. For more details about this phrase see [3].

## 1.5 Tools for Operating System Release and Testing

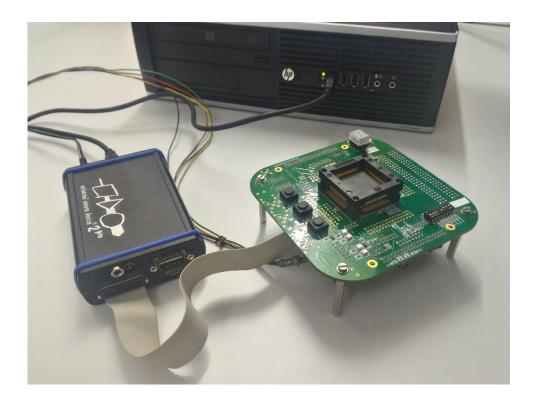

The FTOS code is written in C programming language to guarantee a good level of abstraction and use also opcode functions to speed up the code execution. The OS is always committed to have a backup of what is done with the possibility of comparing actual version of code with the one committed. The testing apparatus is formed by a personal computer, an interface device and the testing board with the 32 bit Infineon TriCore™ microcontroller (the *Device Under Test*). With its real-time performance, embedded safety and security features, the TriCore™ family is a platform for a wide range of automotive applications such as the control of combustion engines, electrical and hybrid vehicles, transmission control units, chassis domains, braking systems, electric power steering systems, airbags and advanced driver assistance systems. TriCore™-based products also deliver the versatility required for the industrial sector, excelling in optimized motor control applications and signal processing. The pc with the interface devices forms the *Automatic Test Equipment*.

#### **1.5.1 TASKING**

It is the Altium microcontroller compiler for advanced automotive applications and it is used for writing code and compiling it. It supports different family of products, also the Infineon TriCore. It supports *C/C++* coding, provides a project files trunk, a console for log/error

messaging and, last but not least, the workspace where write the code. For more info see [4].

#### 1.5.2 UDE

The abbreviation stands for Universal Debugging Environment and takes part in the interface devices of ATE. Debug sessions are part of the daily job during software development, due to the impossibility of never making mistakes. UDE software tool is the debugger used by the testware group before releasing new software. It supports most of Infineon products, using a standard JTAG connection and offers an easy access in read-write to RAM locations, windows to control directly CPU registers and memory locations, while new versions also allow a multi-core debug. Indeed cores can be set in halt/release state independently from the status of other ones, in order to better understand the execution of each CPU. Among other functionalities, a code profiler is provided, which can help in finding execution bottlenecks when unexpected slowdowns are detected. For more info see [5].

#### 1.5.3 JAZZ

It is the Infineon microcontroller test harness. It is an instrument for testing and analysis, which can reproduce the test sequences of the ATE using a PC. JAZZ tool provides interface to device under test, typically with a JTAG access. Moreover, it can drive several control and measure instruments like power supplies, thermo-chambers or multimeters. JAZZ development is based on Object Oriented Programming concept which is a very powerful solution to get test reusability and portability. JAZZ tool can also import or export test patterns from and to other testers, following the direction of strict collaboration between product and test engineers. It is also based on a graphical user interface (GUI), easing user work and training, minimizing man-made errors probability. In JAZZ tool it is possible to create a dedicated tests collection for each device. Tests collection permits to build different test flows. Test flow is a tests collection subset to perform a certain analysis or characterization task; it can contain many copies of the same test and it must return always a "pass" or "fail" depending on result of each test.

Context Analysis, Company Methodologies and Tools | Page 8

# 2 Flash Memories

Since the OS presented is meant for e-Flash testing, an overview on the destination architecture and e-Flash model is needed in order to better understand the specific design choices and the case study.

#### 2.1 Memories Introduction

For thousands of years, humans seek trickery to make less effort, which means evolve to a state of minimum energy. Manual tools, machinery, transportation equipment, industries, software tools, robots and so on are examples of trickeries that minimize the body energy consumption. A major reason of energy consumption of the human body is the brain: it represents only 2% of the weight of an adult but it uses 20% of the energy produced by the body [6]. Efficient energy supply is crucial for the mind so that our memory, mobility and senses can function normally. Then humans searched techniques for storing informations minimizing brain energy consumption and climb over the limits of manual storing. Today, almost every electronic device contains a memory device. Even in the automobile, electronic memories are becoming crucial, given the rise of artificial intelligence to be introduced in the control units of vehicles.

All memories, and in particular, Complementary Metal-Oxide-Semiconductor (CMOS) memories can be divided into two main categories: volatile and non-volatile. Volatile memories lose stored information as soon as the voltage supply is switched off; they require constant power to remain viable. Most types of Random Access Memories (RAM) fall into this category which can be further divided into Static-RAM (SRAM) and Dynamic-RAM (DRAM). On the other hand, memories that maintain their data when the power supply is removed are called Non-Volatile Memories (NVM). The first type of NVM was implemented by writing permanently the data in the memory array during manufacturing (maskprogrammed Read Only Memories, ROM). A big step in CMOS memories was made when Erasable Programmable Read Only Memories (EPROM) were introduced, which can be electrically programmed and erased by exposing them to Ultra-Violet (UV) radiation for about 20 minutes. Electrically Erasable Programmable Read Only Memories (EEPROM) are electrically erasable and programmable, but require more area on silicon to be implemented, lowering density of the memory itself. Flash memories are non-volatile memories in which a set of cells can be electrically programmed and a large number of cells (block, sector or page) are electrically erasable at the same time. So erase operation is very fast since the whole memory can be erased in a single operation. One of the major applications for Flash memories is their integration inside SoC to allow software updates,

reconfigure the system, and allow non-volatile storage; Flash memories which are integrated in SoC are generally called embedded-Flash memories (e-Flash). The two fundamentals parameters of a non-volatile memory are:

- 1. **ENDURANCE**: the capability of keeping stored informations are a huge number of erase/program/read cycles

- 2. **DATA RETENTION**: the capability of keeping the stored informations after a big lapse of time

The focus of this big overview is the embedded flash memory, the type of memory tested at Padua Development Center of Infineon Technologies AG.

# 2.2 Single Flash Cell

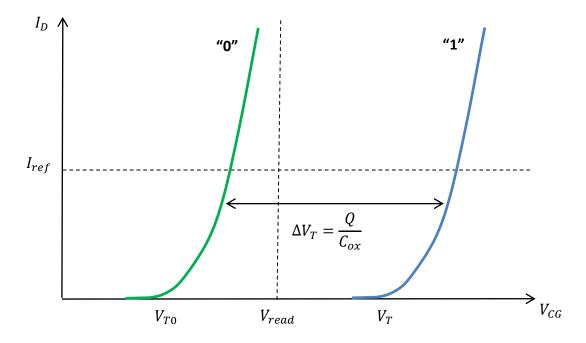

To have a memory cell that has two logical states and maintains its stored information independently of external conditions, the storage element needs to be a device whose conductivity can be altered in a non-destructive way and when it is turned off must keep the charge inside. In CMOS Flash memories, this is achieved changing the threshold voltage  $V_T$  of the transistor, by making it lower or higher of a predefined value, and thus identifying the two logical states of a "programmed" or "erased" cell. This threshold voltage can be described as

$$V_{\rm T} = K - \frac{Q}{C_{\rm ox}}$$

where

- *K* is a constant that depends on gate and substrate material, channel doping and gate oxide capacitance

- ullet Q is the charge in the gate oxide

- $C_{ox}$  is the oxide capacitance between CG and FG

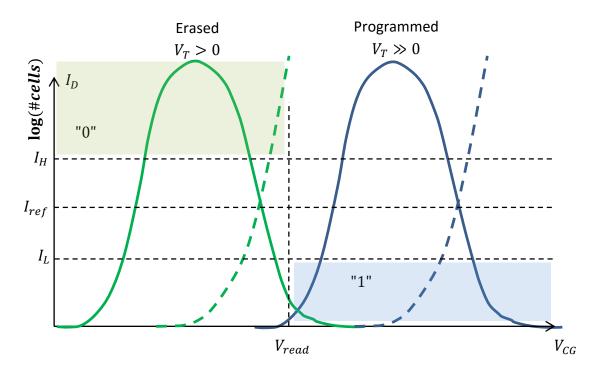

By modifying the charge trapped in the gate oxide, we can create a "shift" in the I-V curve of the transistor and then codify a right-shift with a logical state and a left-shift with the other logical state. Usually "0" states for "uncharged" (erased) and "1" as "charged" (or programmed) as it can see on [Figure 5].

Figure 5: I-V curves shifting for uncharged/charged cases

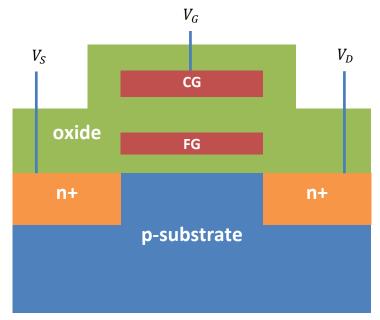

The technology adopted in the e-Flash memory used in the SoC is the FGMOS where the charge is stored in a conductive layer that is between the gate and the channel and is completely surrounded by insulator.

Figure 6: FGMOS cross section

The [Figure 6] shows the cross-sectional view of a flash cell. On top of a flash cell is the control gate (CG) and below is the floating gate (FG). The FG is insulated on both sides, on top by an inter-poly oxide layer and below by a tunnel oxide layer. As a result, the electrons

programmed on the floating gate will not discharge even when flash memory is powered off. The voltage applied on the CG generates and controls the conductivity of the conductive channel between the source and the drain electrodes. The minimum voltage that can turn on the channel is the threshold voltage. As we can see in the  $V_T$  equation, if are injected electrons between CG and FG the threshold voltage increase: this means that the cell is charged. Programming is done on one bit (or byte) at a time, while erasure is done on all cells in the same memory block. The saturation region for a conventional MOS is where  $I_{DS}$  is essentially independent of the drain voltage. In a FGMOS transistor, the drain current will continue to rise as the drain voltage increases and saturation will not occur. But, how it can be checked if a bit cell is programmed or erased? Simple, if charge is stored in FG, it is possible to measure the drain current  $I_D$  of the cell with a fixed  $V_{GS}$  voltage. If this current is over a reference current, the cell results erased ( $Q_{FG}=0$ ) and if it is under the reference value the cell can be considered as programmed. Storing/removing FG charge is commonly done using one of these mechanisms:

- Channel Hot Electron Injection (CHEI)

- Fowler-Nordheim (FN) tunneling

The choice of program/erase mechanism depends on the bit cell structure, array organization, and process technology. The physical mechanism of CHEI is relatively simple to understand qualitatively. An electron traveling from the source to the drain gains energy from the lateral electric field and loses energy to the lattice vibrations (acoustic and optical phonons). At low fields, this is a dynamic equilibrium condition, which holds until the field strength reaches approximately  $100\ kV/cm$ . For fields exceeding this value, electrons are no longer in equilibrium with the lattice, and their energy relative to the conduction band edge begins to increase. Electrons are "heated" by the high lateral electric field and a small fraction of them have enough energy to surmount the barrier between oxide and silicon conduction band edges. For an electron to overcome this potential barrier, three conditions must hold:

- 1. Its kinetic energy has to be higher than the potential barrier

- 2. It must be directed toward the barrier

- 3. The field in the oxide should be collecting it

If these conditions are satisfied, the electrons are injected by the high electric field in the FG. This is a power consuming mechanism due to the large currents and low injections efficiency. The FN tunneling instead is based on quantum mechanics. The solutions of the

<sup>&</sup>lt;sup>2</sup> Refers to the effective temperature term used when modelling carrier density (i.e., with a Fermi-Dirac function) and does not refer to the bulk temperature of the semiconductor (which can be physically cold, although the warmer it is, the higher the population of hot electrons it will contain all else being equal). The term "hot electron" was originally introduced to describe non-equilibrium electrons (or holes) in semiconductors

Schrodinger equation represent a particle. The continuous nonzero nature of these solutions, even in classically forbidden regions of negative energy, implies an ability to penetrate these forbidden regions and a probability of tunneling from one classically allowed region to another. This occurs with the presence of a high electric field. The FN tunneling method is widely used in NVM. The reasons for this choice:

- Tunneling is a pure electrical mechanism

- The involved current level is quite low

- It allows to obtain a program time shorter than retention time

But, on the other hand, the exponential dependence of FN tunnel current on the oxide field causes critical problems. A small variation of oxide thickness  $t_{ox}$  among the cells in a memory array results in a great difference in programming or erasing currents thus spreading the  $V_T$  distribution. Therefore, oxide defects must be avoided to control program/erase characteristics and obtain a good reliability.

A common problem for CHEI and FN tunneling is the high electric filed used for programming the cells. The negative charge trapped into the floating gate decrease the electric field across the gate oxide, so that at the increasing of cell living time it is more and more difficult to inject charge in the FG. Besides, for sustain high electric fields is requested a good doping profile shaping. For more detailed info about single flash cells see [7], [8] and [9].

#### 2.3 Flash Memory Architecture

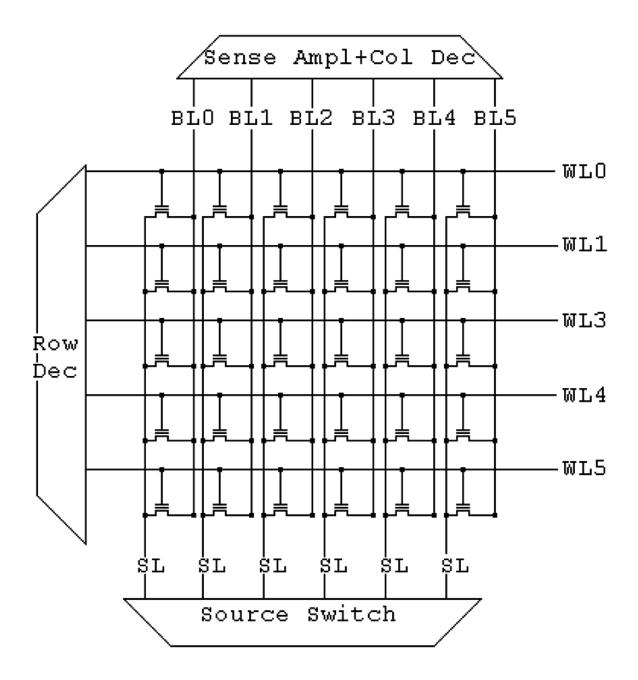

Two main technologies dominate the non-volatile flash memory market today: NOR and NAND. Both NOR and NAND flash memories were invented by Dr. Fujio Masuoka while working for Toshiba around 1980. The name "flash" was suggested by Dr. Masuoka's colleague, Mr. Sho-ji Ariizumi, because the erasure process of the memory contents reminded him of the flash of a camera [10]. NOR flash was first introduced by Intel in 1988. There are two main types of flash memory, which are named after the connection in a way that resembles NAND and NOR logic gates, as NAND and NOR flash memories. The NOR Flash memory is the most commonly used in a wide range of applications that require both medium density and performance. This is the memory architecture of our SoC. In a NOR matrix organization cells are arranged in rows (called word lines) and columns (called bit lines): all the gates of the cells in a row are connected to the same word line (WL), while all the drains of the cells in a column are connected to the same bit line (BL); the source of all the cells in the sector are connected to a common source line (SL). The read operation is done by byte or by word; therefore one cell for each output is addressed. There are some methods to identify the cell status but the most commonly used is to compare the current of the cell with the one of a reference current; the result of the comparison in then converted

into a voltage which is fed to the output. The Sense Amplifier converts this small voltage level to the external higher level. Like read, also program operation is generally performed by byte or by word. The array of cells is physically divided in different sector, each one erasable separately by means of a dedicated source switch. Sectors can be equal or of different size.

Figure 7: NOR flash matrix with decode circuitry and sense amplifiers

It is helpful to divide the memory into blocks, banks and sectors to reduce the delays over the wordlines and bitlines traces. The decoder has the task to enable rows and columns that must be accessed by the externa circuits.

The NAND Flash memory is similar to the NOR, but the access to the matrix is different because the cells are arranged into the array in serial chains: the drain of a cell is connected with the source of the following one. The elementary unit of a NAND architecture flash memory is not a single cell but a serial chains of more FG transistor connected to the bit line and ground through two selection transistors. This organization permits to eliminate all contacts between Word Lines (WL), reducing in this way the occupied area. The reduction of the matrix area is the main advantage of this solution. Selection transistors are biased to connect the chain to the bit line and isolate it from the ground. If the memory is organized in a NAND array, both program and erase mechanism are electrons tunneling. Since tunneling is more power efficient than CHE injection, currents are smaller and different supply voltages can be internally generated by charge pumping circuits implemented in the same die. NAND array are preferred for high-density Flash memories. During reading operation the selected cell has the control gate at OV while the other cells in series are driven at high voltage, thus acting as ON pass gates independently of their actual thresholds. The current, which flows through the series only if the selected transistor presents a negative threshold, can be detected by the sense amplifier, which can interpret the stored data.

# 2.4 Flash Memory Defects and Tests

A defect is a physical anomaly in the circuit's material, which can occur due to many factors in every manufacturing process. Defects can be characterized as a short, an open, increased resistance or capacitance and so on. A fault is the logical representation of a defect. Not all defects lead to faults. Some flash memories defects are listed below.

#### For the single cell:

- $t_{ox}$  oxide thickness variation

- WL to FG resistance

- FG to drain resistance

- FG to source resistance

- CG to drain resistance

- Source and drain to bulk resistances

- Source to drain resistance

- CG, drain, bulk opened

- Mobility reduced

#### Flash Memories | Page 16

#### For the word line:

- WL opened

- WL to bulk resistance

#### For the sectors:

- WL i-th to WL (i+1)-th resistance

- Local BL opened

- Local SL opened

- Local BL i-th to local BL (i+1)-th resistance

- Local BL i-th to local SL (i+1)-th resistance

#### For the memory blocks:

- Global BL opened

- Global SL opened

- Global BL i-th to global BL (i+1)-th resistance

- Global SL i-th to global SL (i+1)-th resistance

#### For the decoders:

- Same WL of two sectors selected

- Multiplexer incorrect output

#### For the sense amplifiers:

• Wrong reference current, i.e. not good sensing operation

These defects occurs after the manufacturing and must be tested how many are and correct it if it is possible. For this purpose, redundancy banks are often used in e-Flash memories: those banks are not used unless a defect is detected in the memory array. In this case, the failing BL/sector is logically replaced with a redundancy one, saving the SoC from being discarded. The mapping of redundancy bitlines is saved into a particular area location, and it is configured during the automated test flows.

The test and characterization engineers must take into account the list of some aspects reported below:

- PE<sup>3</sup> performance

- PE disturbs

- Retention

- Endurance

- DC test/parametric

When a cell is programmed (or erased) the threshold voltages are different depending on silicon process variations. The distribution of the threshold voltages for erased and programmed cells can compromise the operation of storing and reading information inside the memory array. As it can read on page 2 in [11], the  $V_T$  voltage of erased memory cells tends to have a wide Gaussian-like distribution:

$$p_E(x) = \frac{1}{\sigma_E \sqrt{2\pi}} e^{-\frac{(x-\mu_E)^2}{2\sigma_E^2}}$$

Where  $\mu_E$  and  $\sigma_E$  are the mean and standard deviation of the erased state threshold voltage. A test which verifies the correct writing of 0s and 1s patterns can detect anomalous distribution of threshold voltages. Flash memory PE cycling causes damage to the tunnel oxide of floating gate transistors in the form of charge trapping in the oxide and interface states which directly results in threshold voltage shift and fluctuation and hence gradually degrades memory device noise margin. Major distortion sources include:

- Electrons capture and emission events at charge trap sites near the interface developed over PE cycling directly result in memory cell threshold voltage fluctuation, which is referred to as random telegraph noise

- Interface trap recovery and electron detrapping gradually reduce memory cell threshold voltage, leading to the data retention limitation

Moreover, electrons trapped in the oxide over PE cycling make it difficult to erase the memory cells. On [Figure 8] we can see the Gaussian distributions of threshold voltages. The sketched lines represent the drain-source currents: when the cell is erased the FG is uncharged and all the charge is in the channel; for this reason the current is higher than  $I_H$ . When the cell is programmed the FG is charged and only a part of the total charge is in the channel; for this reason the current is lower than  $I_L$ . The Gaussian distributions (bold lines) are centered in the respective mean threshold voltages  $\mu_E$ .

<sup>&</sup>lt;sup>3</sup> **PE** stands for **Program/Erase**. Flash memory cells gradually wear out with the PE cycling which is reflected as gradually diminishing memory cell storage noise margin (or increasing raw storage bit error rate).

Figure 8: Statistical distributions of  $V_T$  during erase and program operations

A test which verifies the correct writing of 0s and 1s patterns can detect anomalous distribution of threshold voltages. Reference currents for the read operations define the tolerance in the variation of threshold voltages, and are generally set differently for erase and program operations, as shown in figure. A sweep on the read currents is performed for the characterization of the flash memory and can provide useful information about "how well" or "how bad" cells are programmed or erased (margin sweep test). Likewise a test which modifies the Control Gate voltages for the read operations can provide similar information (CG scan).

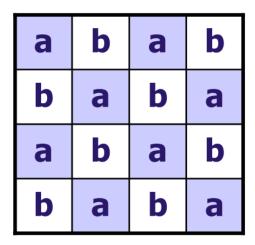

The failure mechanisms referred to as program disturb concern data corruption of written cells caused by the electrical stress applied to these cells while programming other cells in the memory array. Considering a NOR array of flash cells, if we want to program a cell, a high voltage applied to the WL and a negative voltage to the BL are necessary to permit FN tunneling. In these bias conditions there are two major disturbs. The first one, due to the high positive voltage applied to the WL, is called Gate Disturb. This kind of disturbs stress FGMOS which have their gate connected to the WL. There might be tunneling through the oxide and so it is possible to put some charge into the FG of transistors that are not selected. In the second kind of disturb, called Drain Disturb, a relatively high voltage applied to the selected BL can stress the drain of all the cells whose are in the same bit line of the cell to program. In this way, a loss of the charge trapped into the FG could happen. The test flow of a Flash memory, have also to detect if Gate Disturbs and Drain Disturbs can compromise the information stored into disturbed bitcells. Programming *Checkerboard* [Figure 9] or *Zebra patterns* can help the tester to detect these stress conditions. A *checkerboard pattern* [12]

alternates 0s and 1s in both rows and columns of the array, while a *zebra pattern* alternates columns of all 1s with columns of all 0s. The pattern must be programmed at physical level and not at logical level.

Retention errors are value dependent; their frequency is asymmetric with respect to the value stored in the flash cell. Examples of retention errors are  $00 \rightarrow 01$ ,  $01 \rightarrow 10$ ,  $01 \rightarrow 11$  and so on. During retention test, the electrons stored on the floating gate gradually leak away under stress induced leakage current. When the floating gate loses electrons, its  $V_T$ shifts left from the state with more electrons to the state with fewer programmed electrons. For more details [13].

As blocks are repeatedly erased and programmed the oxide layer isolating the gate degrades. This reduces the endurance of the e-Flash memory. Program/erase endurance can be tested by repeatedly programming a single page with all 0s (vs. the erased state of all 1 bits), and then erasing the containing block; this cycle can be repeated until a program or erase operation terminated with an error status [14]. This parameter is measured as number of PE cycles.

DC tests/parametric are contacts tests (opens and short checks), power consumption tests, leakage tests, threshold tests (max and min input voltage at which the device switch from high to low), current tests, timing measurements (rise and fall time, delay, access time measurements), Schmoo plots, etc.

Figure 9: Example of checkerboard pattern where a and b are 0 and 1

# 3 System on Chip Architecture

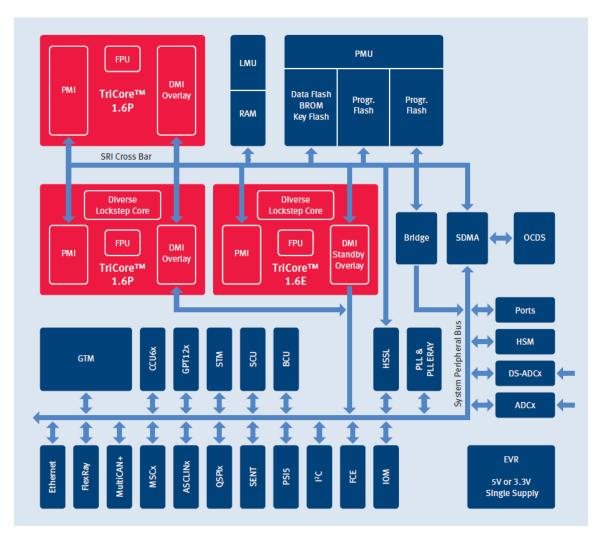

Figure 10: Aurix™ system architecture

Aurix is Infineon's family of microcontrollers serving the needs of the automotive industry in terms of performance and safety. Some applications, where AURIX™ is used, are: chassis domain control, ADAS⁴, gasoline engine management and the transmission control unit (TCU). AURIX™ permits to achieve the ASIL-D level. ASIL stands for *Automotive Safety Integrity Level* and refers to the highest classification of initial hazard (injury risk) defined within ISO 26262 and to that standard's most stringent level of safety measures to apply for avoiding an unreasonable residual risk [15].

<sup>&</sup>lt;sup>4</sup> Advanced Driver Assistant Systems is the group of safety mechanisms like lane assist, emergency brake assist, distance control, etc. Radar technology collects the information in and around the vehicle and the microcontroller elaborate the informations.

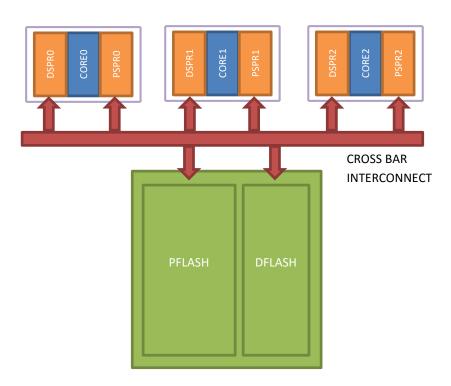

It has a multi-core architecture that is based on three 32-bit TriCore™ CPUs running at 200 MHz in the full automotive temperature range. The block diagram of the presented SoC is showed in [Figure 10]. The 3 red blocks are the CPUs in the SoC. The TC27x sub-family includes two high performance TriCore TC1.6P CPU cores and one high efficiency TriCore TC1.6E CPU core. The two cores are slave cores and the high efficiency core is the master core [16].

In this chapter will be reported, synthetically, some selected features of the SoC needed to understand the operating system release and the validation.

#### 3.1 Internal Buses

The SoC has two independent on-Chip buses:

- **SRI** crossbar<sup>5</sup>, that is the Shared Resources Interconnect protocol that connects the TriCore CPUs, the high bandwidth peripherals and the Direct Memory Access module (DMA) to its local resources for instruction fetches and data accesses

- **SPB** (System Peripheral Bus) that connects the TriCore™ CPUs, the high bandwidth peripherals and the DMA module to the medium and low bandwidth peripherals

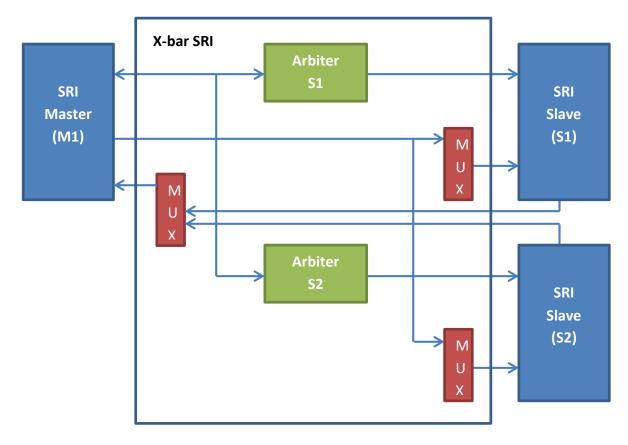

For our intents we use the SRI crossbar (X-bar) that supports parallel transaction between different SRI-Master and SRI-Slave peripherals, which are both referred as Agents of the SRI bus. The SRI X-bar supports also pipelined requests from the SRI-Master interfaces. This is the first important capability of the presented SoC, which actually allows us to consider the implementation of a Multi-Core OS in which a parallel access to the e-Flash memory is desired. The arbitration of the SRI X-bar supports atomic<sup>6</sup> transfers that are generated by atomic assembly instructions which require two single transfer instructions of read and write.

Due to the support for parallel transactions, an arbiter module, on [Figure 11], is implemented for each SRI-Slave, as shown in the figure. The operating frequency is called  $f_{SRI}$  and is generated separately from the Clock Control Unit (CCU).

<sup>&</sup>lt;sup>5</sup> In analogy with old electromechanical telephony crossbar switches

<sup>&</sup>lt;sup>6</sup> Uninterruptable read-modify-write memory operations limited to specific functions and data size

Figure 11: SRI arbitration module

# 3.2 On-Chip Debug Controller

The SoC provides the infrastructure for the various tools used during the development and maintenance of the application. A fundamental tool is the internal debugger: in this situation the application is not yet ready, the system outside of the microcontroller is either not connected or under control by other means so that misbehavior of the software has no catastrophic consequences. In this condition, the user is a software engineer with thorough knowledge of the device and the system, in other words, no protection is needed. From the debug tool the user expects:

• **Download capability**: The memories of the SoC (and of other external memories attached to the SoC) must be written (and programmed in case of non-volatile memories) without need to disassemble the application system

- Running Control: Each processor core can be stopped and started at will, either separately or synchronously throughout the SoC

- **Visibility/Writability**: The content of all storage locations inside the SoC, i.e. memories, SFRs and processor registers, can be read and written, preferably even while the system is running

- Traceability: A log of the processing is desired, as detailed ("cycle accurate") and wide (aligned trace of parallel processes) as possible

These capabilities are mainly managed via the *On-Chip Debug Support* infrastructure (OCDS). Of particular interest are the Run Control features, by which the running CPUs are dynamically configured via access of dedicated Debug Status Register (DBSR). The internal implementation of the SoC sets only the CPU0 in run mode at startup, and puts other CPUs in a Halt-After-Reset state. Halted CPUs have to be released by user (via Debug control features, see [Paragraph 1.5.2]) or by the running CPU with specific debug control instructions. Of course a state-aware watchdog timer suspension during debug sessions is implemented.

#### 3.3 **MMU**

As the FTOS is oriented to test the Flash Memory Unit of the presented SoC, a deeper insight of the Memory Management Unit (MMU) is required. Furthermore, since the FTOS code is downloaded into the RAM memory, we will also have a look at both volatile and non-volatile memories contained in the SoC.

The TriCore microcontroller has the following CPU related memories:

Program Memory Unit (PMU0) with:

- 4 MB of Program Flash Memory

- 384 KB of Data Flash Memory

- User Configuration Blocks (UCB)

- 32 KB of Boot ROM (BROM)

#### CPU0 with:

- 24 KB of Program Scratch-Pad SRAM (PSPR)

- 112 KB of Data Scratch-Pad SRAM (DSPR)

- 8 KB of Program Cache (PCache)

#### CPU1 with:

- 32 KB of Program Scratch-Pad SRAM (PSPR)

- 120 KB of Data Scratch-Pad SRAM (DSPR)

- 16 KB of Program Cache (PCache)

- 8 KB of Data Cache (DCACHE)

#### CPU2 with:

- 32 KB of Program Scratch-Pad SRAM (PSPR)

- 120 KB of Data Scratch-Pad SRAM (DSPR)

- 16 KB of Program Cache (PCache)

- 8 KB of Data Cache (DCACHE)

The system has non-uniform memory access timing (NUMA), i.e.:

#### Fast (1 cycle typical)

- Read/Write to local Data Scratch (DSPR) or DCache

- Fetch from local Program Scratch (PSPR) or PCache

## Medium (6-8 cycles)

other DSPRs/PSPRs (including data in local PSPR and fetch from local DSPR)

## Slow (8-20 cycles)

Program Flash

#### Very Slow (> 20 cycles)

Data Flash (EEPROM + UCB)

Boot ROM is the memory sector that permits the startup of the system. Scratchpad RAMs are high-speed internal memories used for temporary storage of calculations, data, and other work in progress. They are used to hold small items of data for rapid retrieval and are mostly suited for storing temporary results (as it would be found in the CPU stack) that typically wouldn't need to always be committing to the main memory. In particular PSPR (Program Scratchpad RAM) stores codes and DSPR (Data Scratchpad RAM) stores data. Each

RAM segment can be accessed in an absolute addressing mode, or with a relative addressed mode. Using the relative address mode, each CPU can access only its own PSPR and DSPR, and this feature is useful to make some particular data/code private for each CPU (i.e. not accessible from other cores). As a consequence, a CPU trying to access a private data/code, different from its own one, will trap into an illegal instruction or load a wrong content. In order to increase performances, every data/code frequently used by a CPU should be located inside the relative RAM (PSPR or DSPR), reducing the penalty for accessing far memory location. The *cache* instead, is a component that stores data so future requests for that data can be served faster; the data stored in a cache might be the result of an earlier computation, or the duplicate of data stored elsewhere. A cache hit occurs when the requested data can be found in a cache, while a cache miss occurs when it cannot. The caches are usually very small to be cost-effective and to enable efficient use of data. Naturally PCache stands for Program Cache and DCache for data cache.

Also the flash module is divided into program and data sections:

- Program flash 0

- Program flash 1

- Data flash 0

- Data flash 1

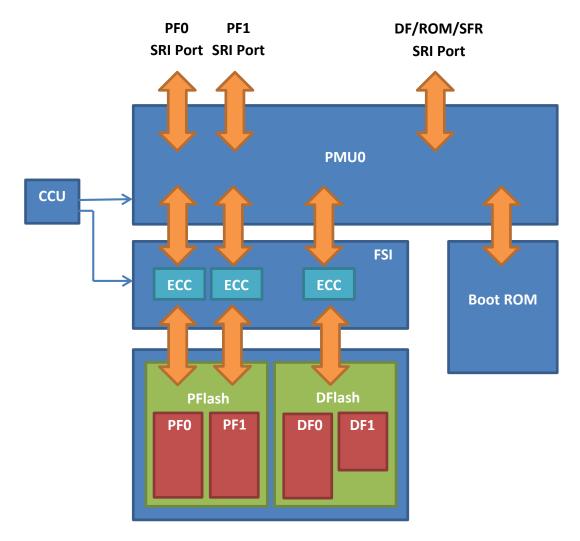

Each bank is further divided in Physical Sectors which contain a different number of Logical Sectors. Logical Sectors are divided in word-line clusters, word-lines and then in pages. The benefit of having sectors is that the Flash memory is sector-erasable, meaning you can erase one sector at a time. In the past, erase commands erased the entire memory chip - therefore to keep a working copy of that data during run-time, an application required additional memory [17]. For reliability reasons, each page has a subset of Error Correction bits, which guarantee the detection and correction of failing bits, referred as ECC. This expensive correction mechanism is fundamental in automotive applications, where errors must be avoided for safety reasons. Flash memory consists also of some redundancy sections, as already mentioned. Whenever a bit-line has a process defect, it is logically replaced (i.e. mirrored) with a new bit-line of the redundancy section. The PMU is connected with the SRI X-bar via dedicated SRI Ports on the Program Flash 0, Program Flash 1, and Data Flash [Figure 12]. That means that a concurrent access is possible for PFO and PF1, but not for DFO and DF1 (it should need between arbitration master agents, introducing some access delay). The operating frequency of the PMU is generated by the CCU, which also provides the clock for all modules inside the SoC. Low level instructions on the flash triggered by the CPU ( such as read, program, erase, ECC check, etc.) are executed by the internal logic of the PMU and by a finite state machine.

Figure 12: PMU synthetic scheme

#### **3.4** TriCore<sup>™</sup> Core Architecture Overview

TriCore™ is a 32-bit DSP and microcontroller with single-core architecture optimized for real-time embedded systems. The TriCore™ Instruction Set Architecture (ISA) combines the real-time capability of a microcontroller, the computation power of a DSP and the high performance/price ratio of RISC architectures, in a compact re-programmable core. The ISA supports a uniform, 32-bit address space, with virtual addressing capabilities and memory-mapped I/O. The architecture allows for a wide range of implementations, ranging from scalar through to superscalar, and is capable of interacting with different system architectures, including multiprocessing. The architecture supports both 32-bit and 16-bit instructions formats (as a subset of the 32-bit instructions chosen by their frequency of use) to reducing code space occupation, lowering consequently memory requirements and power consumption. Typical DSP instructions and data structures are largely supported by seven addressing modes used, for instance, in Finite Impulse Response (FIR) filters, or in FFT calculation. They also support efficient compilation of C/C++ programs.

Real-time responsiveness is largely determinate by interrupt latency and context-switch time<sup>7</sup>; the high-performance architecture minimizes the interrupt latency by avoiding multicycle instructions and by providing a flexible hardware-supported interrupt scheme which also grants a fast-context switch.

The key features are here summarized:

- 32-bit architecture

- 4GBytes of address space (physical and virtual)

- 16/32-bit instructions for reduced code size

- Most instructions executed in one cycle

- Branch instructions with branch prediction module

- Low interrupt latency with fast context-switch using wide pathway to on-chip memory

- Zero-overhead loop capabilities

- Floating-Point Unit (FPU)

- Memory Management Unit (MMU)

- Single bit handling capabilities

- Flexible interrupt prioritization scheme

- Little-endian byte ordering for data memory and CPU registers

- Memory protection

- Coprocessor support

- Debug support

The main topics of interest will be the Context-Management System, supported by an Infineon international patent, the System Timer Module (STM), Interrupts and Traps management. The registers are divided into:

- 32 General Purpose Registers (GPRs)

- Program Counter (PC)

- Two 32 bit registers containing status flags, previous execution informations and protection informations: Previous Context Information (PCXI) and Program Status Word (PSW)

PCXI, PSW and PC are fundamental for storing and restoring task's context.

<sup>&</sup>lt;sup>7</sup> In order to be classifiable as an RTOS an operating system must: have a time predictably response and be deterministic. For these reasons interrupt latency and context-switch time must be minimized to have the sureness of execute the processes in a determinate fixed times, imposed by the work context.

| A [15] (Implicit Base Address)  | D [15] (Implicit Data) |    | PCXI   |   |

|---------------------------------|------------------------|----|--------|---|

| A [14]                          | D [14]                 |    | PSW    |   |

| A [13]                          | D [13]                 |    | PC     |   |

| A [12]                          | D [12]                 | 31 | Custom | ( |

| A [11] (Return Address)         | D [11]                 |    | System | , |

| A [10] (Stack Return)           | D [10]                 |    |        |   |

| A [9] (Global Address Register) | D [9]                  |    |        |   |

| A [8] (Global Address Register) | D [8]                  |    |        |   |

| A [7]                           | D [7]                  |    |        |   |

| A [6]                           | D [6]                  |    |        |   |

| A [5]                           | D [5]                  |    |        |   |

| A [4]                           | D [4]                  |    |        |   |

| A [3]                           | D [3]                  |    |        |   |

| A [2]                           | D [2]                  |    |        |   |

| A [1] (Global Address Register) | D [1]                  |    |        |   |

| A [0] (Global Address Register) | D [0]                  |    |        |   |

| Address 0 3                     | Data                   | 0  |        |   |

|                                 |                        |    |        |   |

| Y                               |                        |    |        |   |

| GPR                             | S                      |    |        |   |

Figure 13: TriCore™ context registers

The 32 GPRs are divided into sixteen 32-bit data registers (D [0] to D [15]) and an equal number of address registers (A [0] to A [15]). Architectural registers, together with the Context Management registers, compose the *context of a task*. Registers  $[0_H - 7_H]$  are referred to as the Lower Context registers and registers  $[8_H - F_H]$  are called Upper Context registers. In addition to the GPRs, the core registers are composed of a certain number of Core Special Function Registers (SFRs) which control the operation of the core and provide status information about the core itself.

The TriCore microcontroller implements Harvard architecture [18], which means physically separate storage and signal pathways for instructions and data. The term originated from the "Harvard Mark I" relay-based computer, which stored instructions on punched tape (24 bits wide) and data in electro-mechanical counters. This architecture is in contrast with von Neumann classical architecture where the CPU can be either reading an instruction or reading/writing data from/to the memory, but one and the other cannot occur at the same

<sup>&</sup>lt;sup>8</sup> The IBM Automatic Sequence Controlled Calculator was installed at Harvard University in 1944. 51 feet long, 5 tons and incorporates 750,000 parts which was including 72 accumulators and 60 sets of rotary switches, each of which can be used as a constant register, plus card readers, a card punch, paper tape readers, and typewriters.

time since the instructions or data use the same bus system. Then using Harvard architecture permits to concurrent write/read data and reading codes.

The TriCore™ CPU has also a *superscalar architecture*: this means that the CPU executes more than one instruction during a clock cycle by simultaneously dispatching multiple instructions to different execution units (ALU, bit shifter, multipliers, etc.) within it.

Any CPU in the microcontroller accesses separate Program and Data Stretch Pad RAM (PSPR and DSPR), with their own caches and interfaces. This distinction will be relevant while discussing the code/data allocation during the linking phase. While operating context switches<sup>9</sup>, a particular attention to the pipelines state will be required, using specific Data-Synchronization instructions (DSYNC) in order to avoid Pipeline hazards<sup>10</sup>. These last are situations that must be avoided. There are 3 types of hazards:

- Structural hazards: when a planned instruction cannot execute in the proper clock cycle because the hardware does not support the combination of instructions that are set to execute

- Data hazards: when a planned instruction cannot execute in the proper clock cycle because data that is needed to execute the instruction is not yet available (pipeline stall<sup>11</sup>)

- Control hazards: arises from the need to make a decision based on the results of one instruction while others are executing

For more detailed info about hazards and computer structures read intensively [19]. In the TriCore™ CPUs pipeline hazards are minimized by the use of forwarding paths between pipeline stages allowing the results of one instruction to be used by a following instruction as soon as the result becomes available. For the 1.6 Efficiency core, single pipeline architecture is implemented (scalar Harvard), in order to allow a power efficient computation, at the cost of a slower processing.

#### 3.5 Context Management System

An overview of Context Management System will be reported below. A more detailed explanation can be found in the thesis [20] and in the Infineon Patent [21]. In the TriCore architecture, the RTOS layer can be very thin and the hardware can efficiently handle much of the switching between one task and another. At the same time the hardware architecture

<sup>&</sup>lt;sup>9</sup> Context switch is the process of storing and restoring the state of a process or thread so that execution can be resumed from the same point at a later time. This operation is fundamental for the multi-core system.

<sup>&</sup>lt;sup>10</sup> Situations in pipelining when the next instruction cannot execute in the following clock cycle

<sup>&</sup>lt;sup>11</sup> (aka bubble) is a delay in execution of an instruction in an instruction pipeline in order to resolve a hazard

allows a software management of the context switch with relatively few constraints imposed to the system designer by the architecture.

"A task is an independent thread of control", as defined in [22]. The state of a task is defined by its context. When a task is interrupted, the processor uses that task's context to re-enable the continued execution of the task when is requested. The lower context registers are similar to global registers in the sense that an interrupt/trap handler or a called function sees the same values that were present in the registers just before the interrupt, trap or call. Any changes made to those registers that are made in the exception routine or call, remains after the return from the event: that means that the lower context registers can be used to pass arguments to called functions and pass return values from those functions.

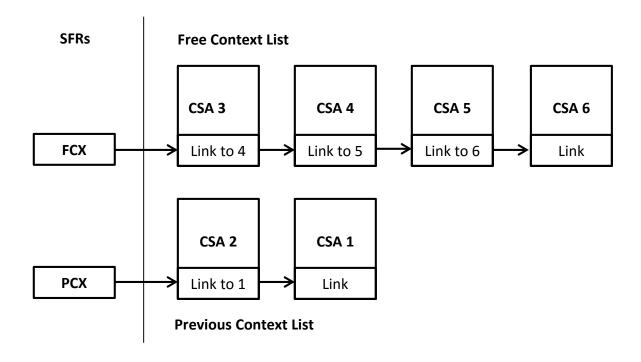

Contexts, when saved to memory, occupy blocks of storage referred as Context Save Areas (CSAs). The architecture uses linked lists of fixed-size CSAs, and each CSA can thus hold exactly one upper or one lower context, linked together through the Link Word. During a context save operation, the upper and lower contexts can be saved into CSAs. The unused CSAs are linked in the Free Context List (where FCX is the free context pointer) and the CSAs that contain the upper and/or lower context are linked in the Previous Context List (where PCX is the previous context list pointer), as can be seen in [Figure 14].

Figure 14: CSA chain before a function call (this image is present on the US 7434222 B2 patent's extract available online)

The Link Word "Link to 4" e.g. takes account that CSA4 is the next CSA available after CSA3. Before a context is saved in the first available CSA (in this case CSA3), the Link Word of this last is read to supply a new value for the FCX register. PCX is updated as soon as the new task completes its execution. There is also another register that points to the last free CSA: the LCX register. When FCX matches with LCX, the CSA chain is full. An important detail is that the upper context is saved automatically by the hardware instead the lower context is saved through an instruction.

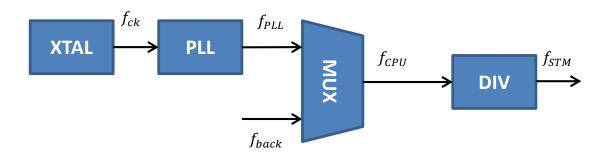

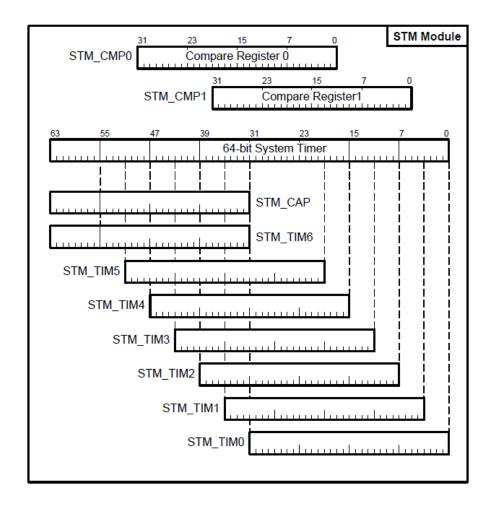

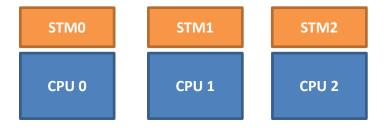

# 3.6 System Timer and Interrupts Management

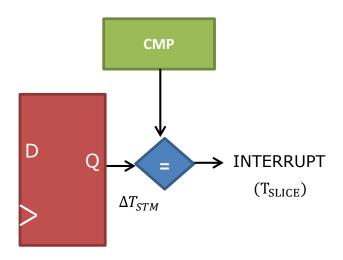

Any CPU has a System Timer Module (STM), after a reset is always enabled and starts counting. The timer is implemented as a 64-bits upward counter register running at the system frequency. There are 7 registers (STM\_TIMO...STM\_TIM6), each with different timing range and resolution. The content of these registers can be compared with other registers (STM\_CMPO and STM\_CMP1). Each CMP register has its compare match interrupt request flag that is set by hardware on a match event. An interrupt is an exception signaled by a peripheral or generated by a software request. Not all interrupts has the same priority, for this reason is defined an interrupt priority level for any of it. Service Request Nodes (SRNs) are linked to the Interrupt Control Unit (ICU). This last manages the arbitration among the requests from the SRNs, provides the winner and checks the signal integrity possible errors. SRNs instead are nodes whose skill is to request the interrupts and have registers that takes account of priority level. When an interrupt is triggered by a CPU, an Interrupt Service Routine (ISR) is executed as a callback function<sup>12</sup>. While the processor executes an ISR, it works in an isolated context since an interrupt with higher priority have been triggered. For more info refer to [20].

$<sup>^{\</sup>rm 12}$  It is a function that is passed as an argument to another function

# **4 Operating System**

# 4.1 Why a Multi-core/Multi-task Functional Test Operating System?

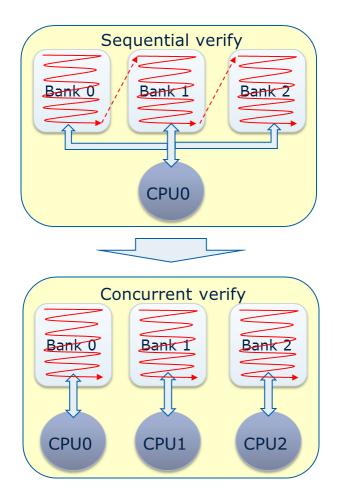

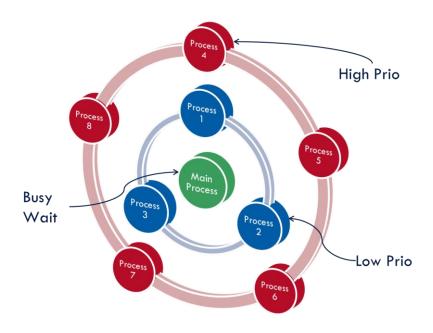

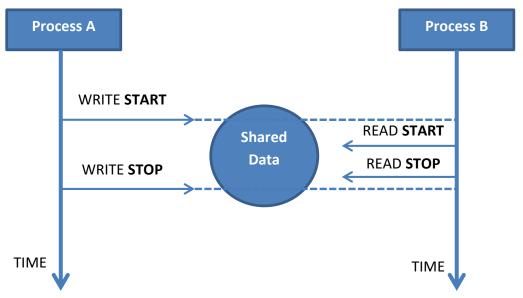

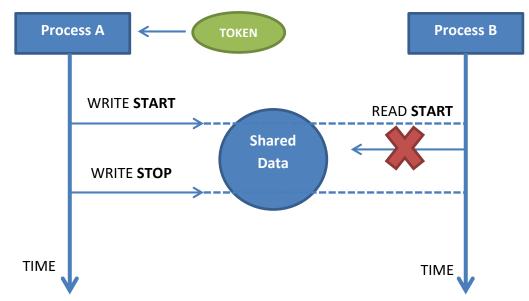

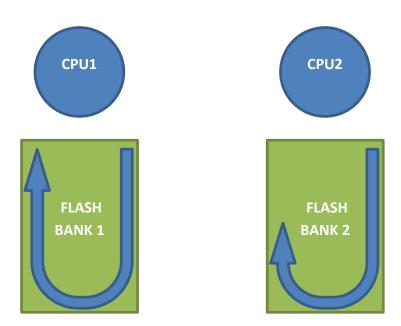

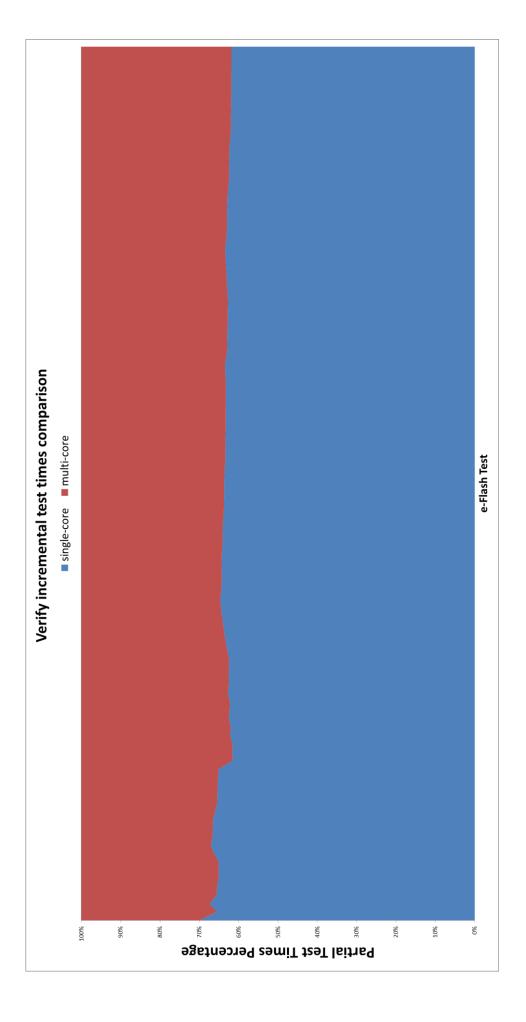

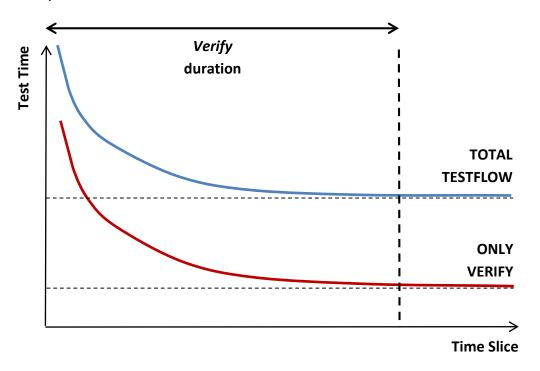

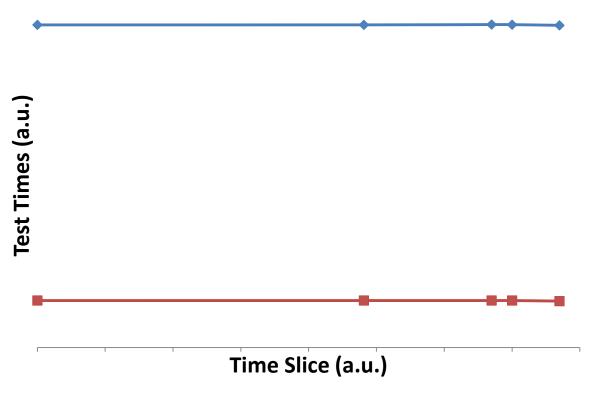

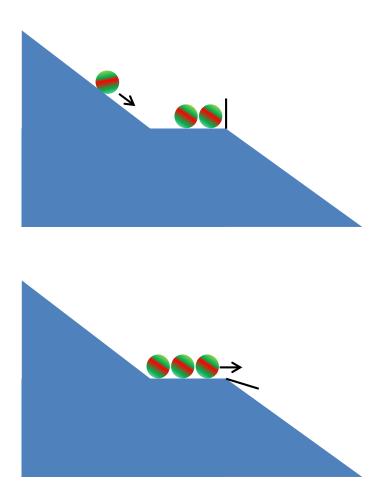

In [Paragraph 1.2] has been introduced the road traveled by the company from the old Built-In Self-Test mechanism to the Functional Test Operating System. This version, nowadays used by Infineon's e-Flash test engineers, is a single-core OS<sup>13</sup>. This system permits to test different families of products respect to BIST where there is no portability because any test must be written for any microcontroller and stored on any of it. But, the increase of the requested computing power for the AI<sup>14</sup> has pushed the technology to realize multi-core CPU architectures and increasing the e-Flash dimensions for storing more pre and post-elaborated data. Then, the single-core Functional Test OS has become obsolete, because the test times are increased and the software don't gives total hardware coverage (a single-core OS on a multi-core architecture). So, the MC team proposed to improve the OS with a multi-core version. As it can be seen in [Figure 15], with a single CPU it can be test a memory bank at time (sequential memory test) and if the memory dimension increase the test time increase. With a multi CPU system it can be possible to concurrent test the memory banks, reducing the test time respect to single core architecture. The MC team decided also to have a multi-task OS. Thus, as already said, the target is a multi-core multi-task operating system.

But, let's do some order.

For definition a multi-core OS is a system that can handle a multiprocessor architecture. There are several types of it:

- **Symmetric** Multi-Processor (SMP) system: each core shares the same OS and user applications, resulting in a system in which each core can run all programs and perform all operations. It is reliable, use resources effectively, can balance workloads well but it is the most difficult configuration to implement

- Loosely Coupled Multi-Processor system: each core has its own memory, I/O devices and operating system. The cores can communicate each other. When a job arrives, it's attached to the free processor. To keep the system well balanced and to ensure the best use of resources, job scheduling is based on several requirements and policies. When a processor fails, the other continues to work independently

<sup>&</sup>lt;sup>13</sup> Stands for "Operating System"

<sup>&</sup>lt;sup>14</sup> Stands for "Artificial Intelligence": the ability of a computer or other machine to perform actions thought to require intelligence. Among these actions are logical deduction and inference, creativity, the ability to make decisions based on past experience or insufficient or conflicting information, and the ability to understand spoken language (definition of "The American Heritage® New Dictionary of Cultural Literacy, Third Edition")

Figure 15: Single-core vs Multi-core e-Flash tests

• Master-Slave Multi-Processor system: only one core, referred as the Master Core, has a complete access to all OS code and to all user applications. All other cores (Slave Cores), can access only a small subset of the OS and are usually triggered by the Master Core in order to execute any program. This configuration is well suited for computing environments in which processing time is divided between front-end and back-end processors; in these cases, the front-end processor takes care of the interactive users and quick jobs, and the back-end processor takes care of those with long jobs using the batch mode. The reliability is not higher because if the master core fails, the system fails. It increases the interrupts because anytime slave cores need an OS intervention they must interrupt the master core. It can lead to poor time management because a free slave core must to wait the master core for the next operation

As we see, there are various pro and cons. The TriCore<sup>™</sup> has a master-slave configuration, because the SMP solution was discarded due to the HW limitations of the SoC. Another

problem to the SMP configuration was coming from the ATE communication protocol, which expects the executions of flows to be sequential, and not parallel, so ATE commands are always triggered one by one. This also limits the parallelization of the execution if no update to the ATE interface is desired. But it has also a scheduler that permits the multitasking. This means that is not the traditional master-slave configuration.

Multitasking instead is not related to the core architecture, but is related to the processes scheduling. It can be implemented also in a single-core CPU. More rigorously, it is a synonym for multiprogramming, a technique that allows a single processor to process several programs residing simultaneously in main memory and interleaving their execution by overlapping I/O requests with CPU requests.

Thus, the engineers choose to implement a multi-core master and slave OS with a multitasking ability for any CPU. The scheduler was designed and developed during multitask and also multi-core improve. This not means that the scheduler is designed for having a multi-core OS. The multi-core speeds up the e-Flash tests execution. The multitasking instead improves any core's throughput. This last is the rate at which the processes are executed. In pragmatic way, the multitasking avoids dead time in the mechanism of processes execution on any core. Finally we can answer to the initial question: it is used a multi-core multi-task OS because it is improved the e-Flash tests speed using a master-slave configuration (this to maintain a lower power consumption when only one core is needed to execute) and the multi-task feature needs to compensate the problem of a low throughput of a traditional master-slave configuration. For more theory definitions and deepening of theory read [22] and [23].

Now that the idea is clear, we can proceed to the OS structure. The multi-core version has been coded from the single-core version. Thus, we can analyze some basic things that we have also in the multi-core version. The Functional Test OS is initialized at the startup of the testing sequence (where only master core is running), and is active across the whole execution, in order to provide a standard interface with the ATE and the DUT, handling the correct scheduling of the test flow. The ATE can start the execution of Task Applications from the testware libraries, while the Task Application itself sees in the FTOS a hardware abstraction of the Device Under Test. The list of sequence of test is grouped into some Flow Tables (FT) where any element contains the list of tests that must be performed. Flow tables are loaded in RAM with the TW library, and thanks to the FTOS the ATE can ask the DUT to execute all the tests inside the FT one by one. After the entire sequence of test executed, the OS returns a log of the tests executed. In [Figure 16] are represented the operating system modules and how can be accessed.

Figure 16: OS modules and layers

#### Functional Test OS can be accessed through:

- ATE command interface: ATE access to the RAM locations and writes the opcode of the command

- Testware System Call: when a Task Application (TA) needs to perform a low level operation a jump to FTOS is taken. This allows the upper code layers to be more portable across different microcontrollers (μCs) families

- **Hardware Trap Event**: If an illegal instruction (contained in the trap vector table) is performed, the trap handler provides informations about the anomalous termination

The tests are executed via flow commands. The Flow Manager module permits to embed test flows into DUT and to handle their execution threads. Tests are stored in DUT SRAM in a structured Flow. Flow Manager saves the index of test to run and the flow status.

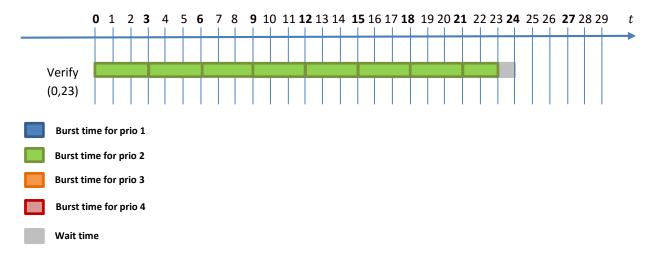

Regarding the multi-core scenario, the master core is the only CPU running at the startup and awakes the other cores during the initialization sequence. All the commands from the test equipment are received from the master core that coordinates the other cores deciding what processes they must execute. All slave cores are always on waiting for new commands coming from the master and can't create any process. The multi-core feature has been introduced for a specific task called *Verify*. This last contains a list of tests performed of the e-Flash memories.

The new Functional Test OS guarantee the backward compatibility with the old operating system. It also guarantee the scalability of the system to more CPUs, more e-Flash banks, major dimensions of Word Lines, Sectors, Pages, redundancy and so on. For more detailed informations see [20].

#### 4.2 Scheduler Module

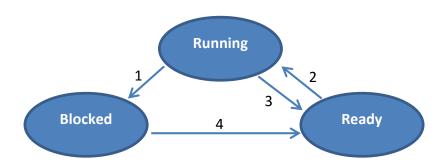

The scheduler is the module that choices what process to run next. To describe the OS scheduler, we must to define and explore what are processes and the difference between threads. A process is all the software that is runnable. There are two types: foreground processes (principal processes that interact with the user) and daemons (processes that run in background). A process could be in one of the next three states:

- Running: when a CPU is using this process

- Ready: when the process execution is stopped temporarily till another process, usually with high priority, is running on the same CPU

- Blocked: unable to run until some external event happens

Figure 17: States possible transitions

Four transitions are possible:

- 1. Process blocks for input

- 2. Scheduler picks another process

- 3. Scheduler picks this process

- 4. Input becomes available

A process is an entry of the process table where are stored informations, stack pointers, program counters, memory allocations, etc. about the process. For any process there are lightweight processes called threads. When a process thread interrupts its execution, another thread of the same process continues to run. This multitasking solution permits a high throughput, because the core has no dead time. The [22] is a good reference for what concerning OS, processes, threads and schedulers theory.

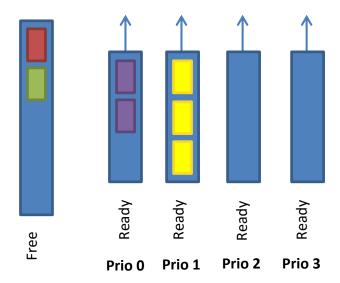

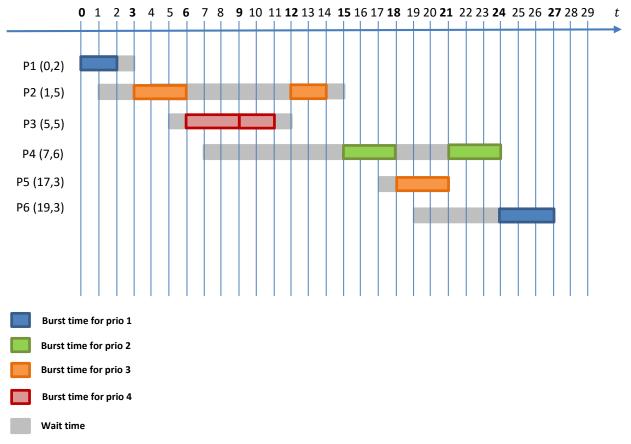

In the new FTOS, the scheduling policy is a round robin which accepts a configurable maximum number of processes, priority levels and maximum call depth per process. To each process is assigned a time interval, called its quantum, during which it is allowed to run. If a process is still running when its quantum is finished, the CPU is preempted and given to another process. If the process has blocked or finished before the quantum has elapsed, the CPU switching is done when the process blocks. All the schedulers need to maintain a list of runnable processes. An interesting issue is the length of quantum. Switching from a process to another requires some time for doing the administration (saving and loading registers, updating tables, flushing and reloading caches, etc.). This operation is called context switch (see what has almost been said in [Paragraph 3.5]). If the quantum is set too short causes too many process switches and lowers the CPU efficiency, but setting it too long may cause poor response to short interactive requests. The scheduler has a priority scheduling: each process is assigned a priority and the runnable processes with highest priority are allowed to run before which have a lower prio<sup>15</sup>. All other processes are organized in queues [Figure 18], sorted by the level of priority. When no process is running, they are all listed inside a "Free processes queue". When a new task is needed by the CPU, a process for that task is created, popping it from the list of free processes. When the process is created, a priority level is assigned to it, and it is immediately pushed inside the proper priority queue. If no other process is ready for the execution, or if the process wins the priority competition, that process is set as running process for a quantum time slice. During the quantum time slice, the process can't be interrupted by the scheduler, and it continues its execution until next scheduler's step, which is automatically triggered by a System Timer Interrupt. The duration of the quantum is configured during the initialization procedure of the scheduler itself, and when the time quantum elapses, the process' context is saved and the scheduling routine starts executing, also if no other process is ready. Instead, if new processes are available, the schedulers set as running the ready process with the highest priority, keeping other processes in wait until the higher processes terminate their execution. Round robin policy is applied for processes which share the same priority level [Figure 19].

<sup>&</sup>lt;sup>15</sup> Abbreviation of "priority"

Figure 18: Free process queue and priority queues

The processes are implemented as structures in C programming language. They contains the context registers (LCX, PCX and FCX) and the pointer to the users stack (pstack). A pointer to the next\_process implements the process queue. The process\_id and the index are useful to identify the process among the whole program (process\_id) and inside its queue (index). For more detailed info on the scheduler implementation refer to [20].

Figure 19: Round robin scheduling

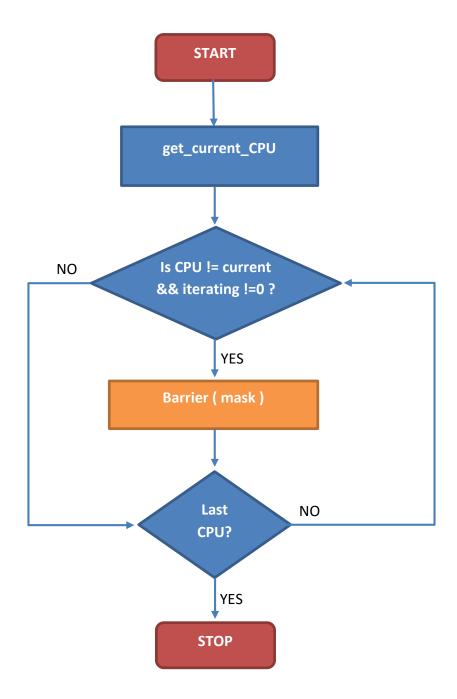

# 4.3 Multi-core Verify and Iterator Module

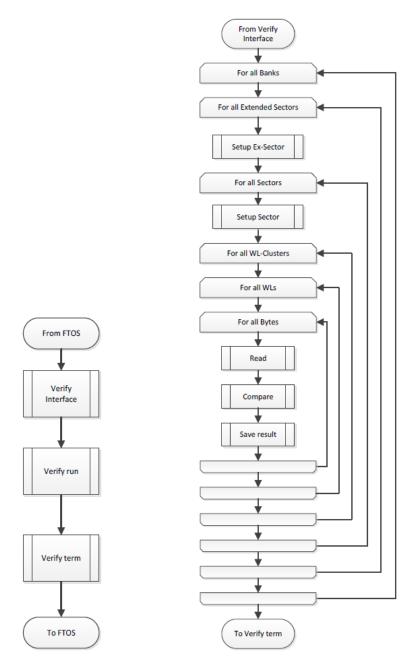

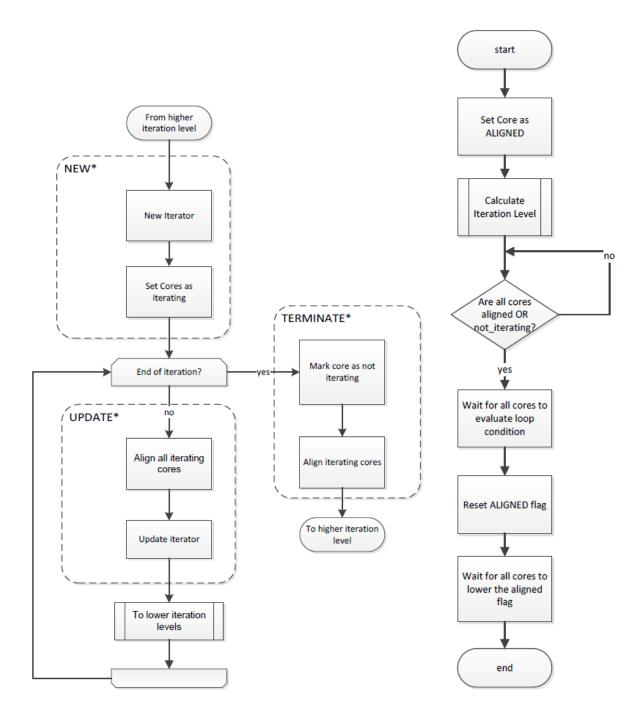

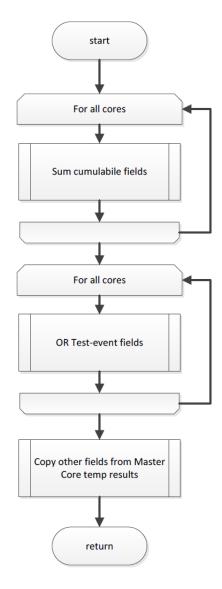

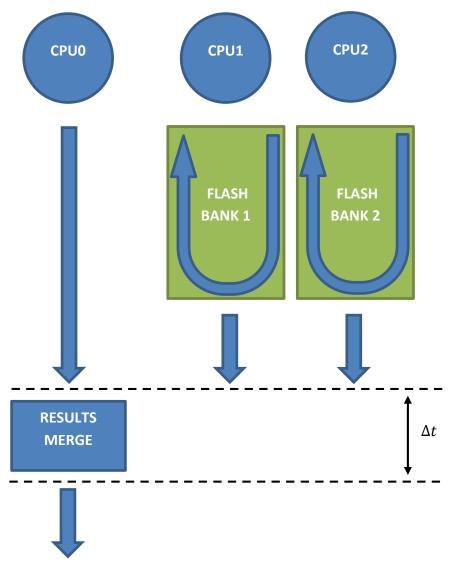

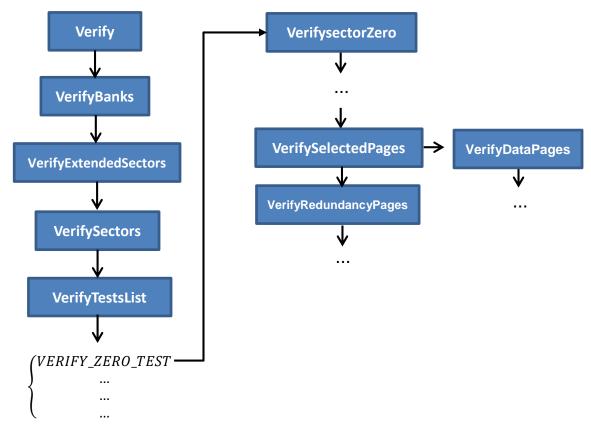

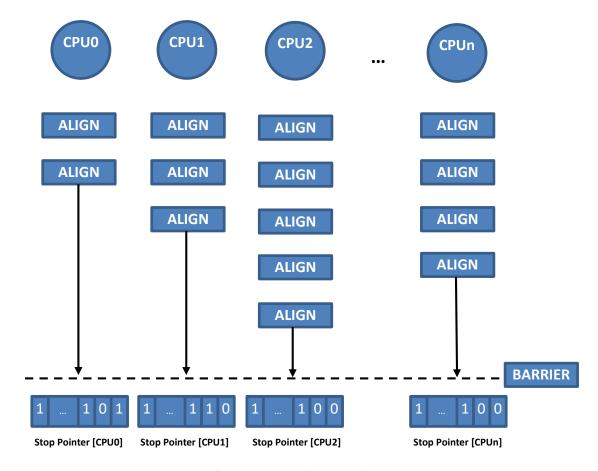

As it can be seen in [Figure 15] some pages back, the multi-core verify permits to reduce the test time used for testing memory banks using a concurrent e-Flash modules scanning. The function flowchart is depicted below in [Figure 20].

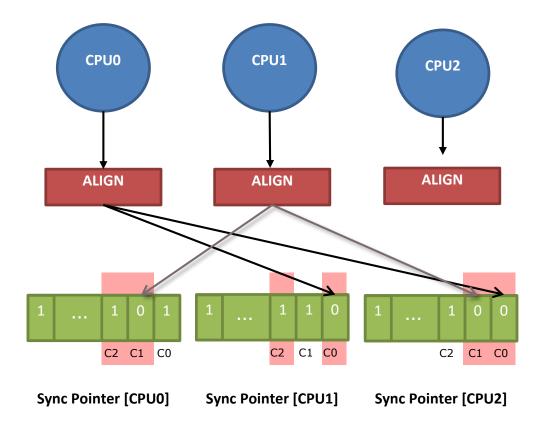

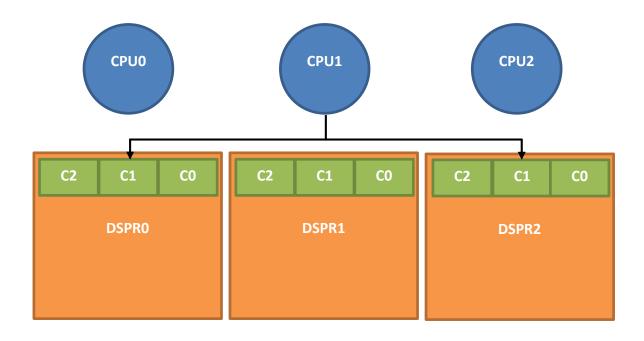

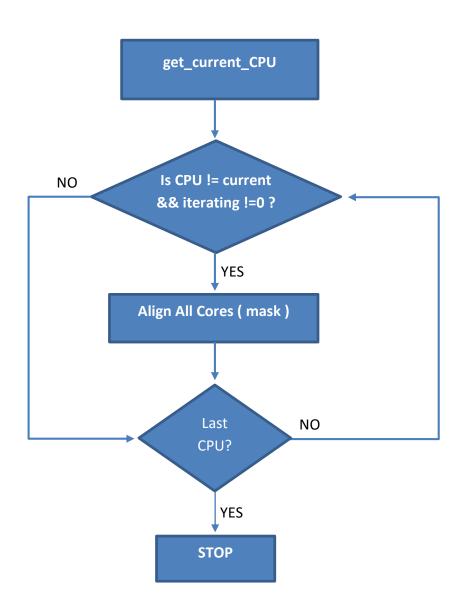

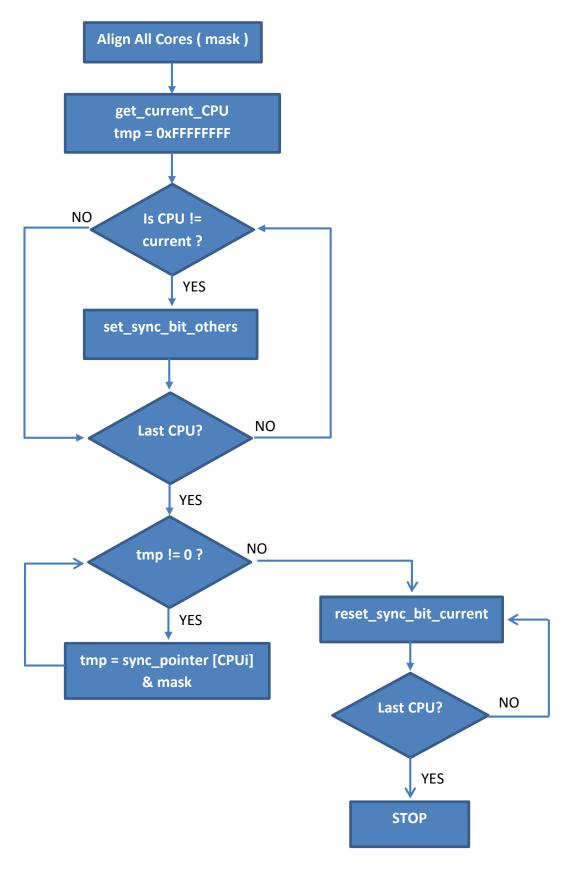

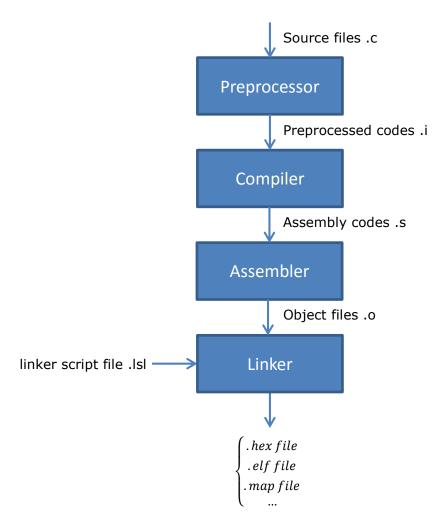

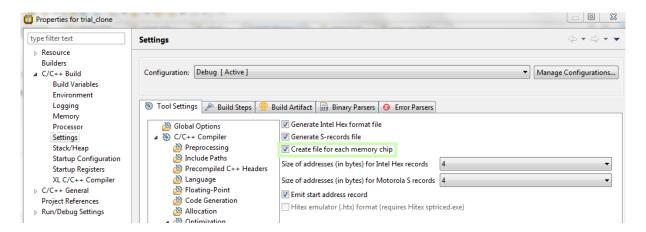

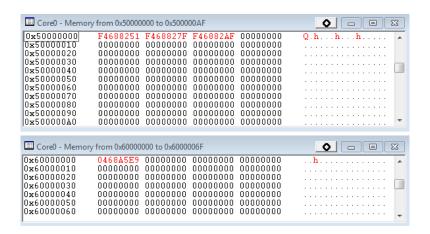

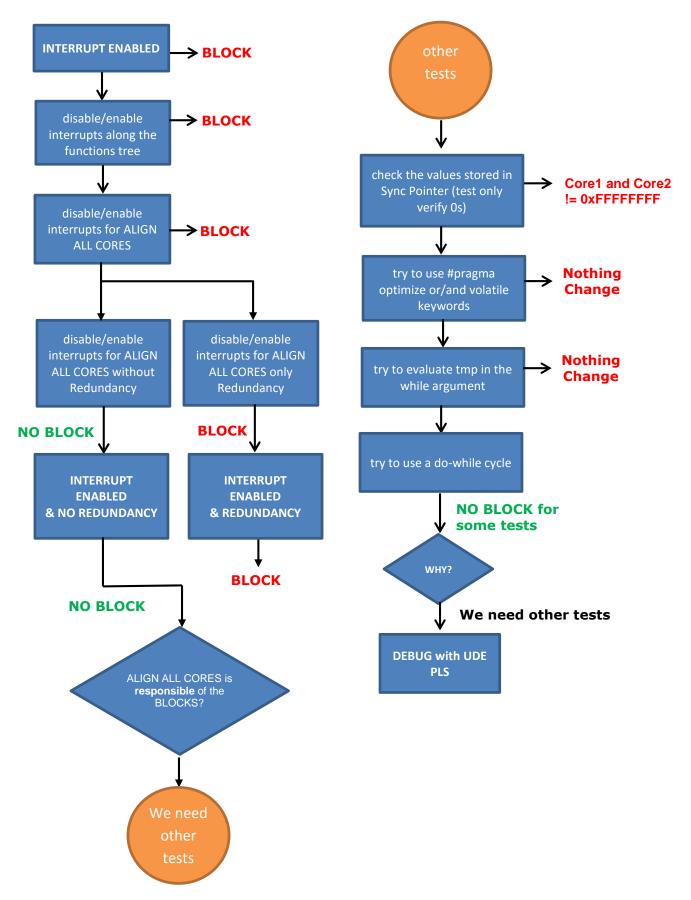

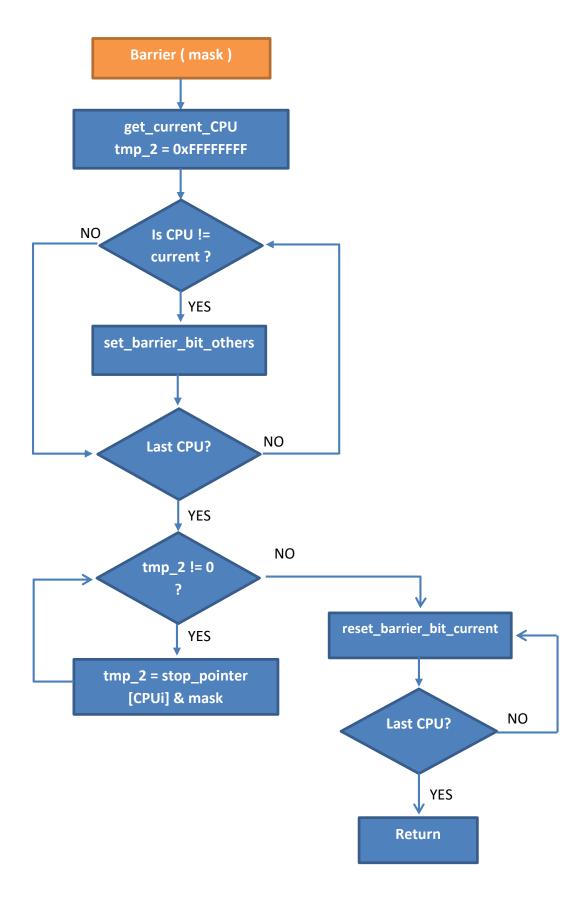

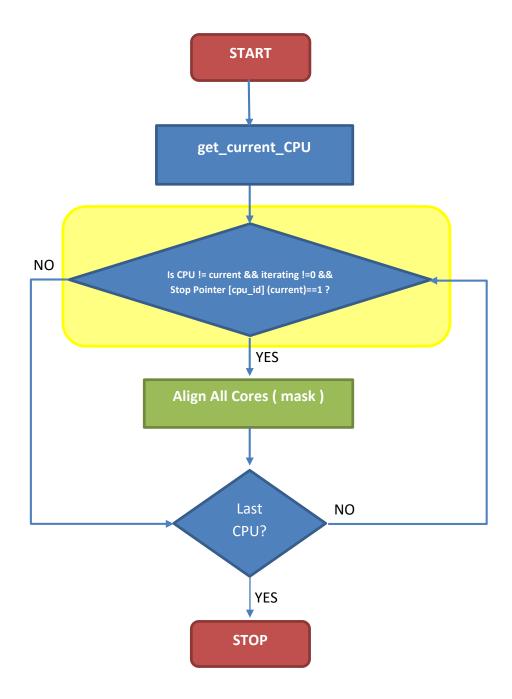

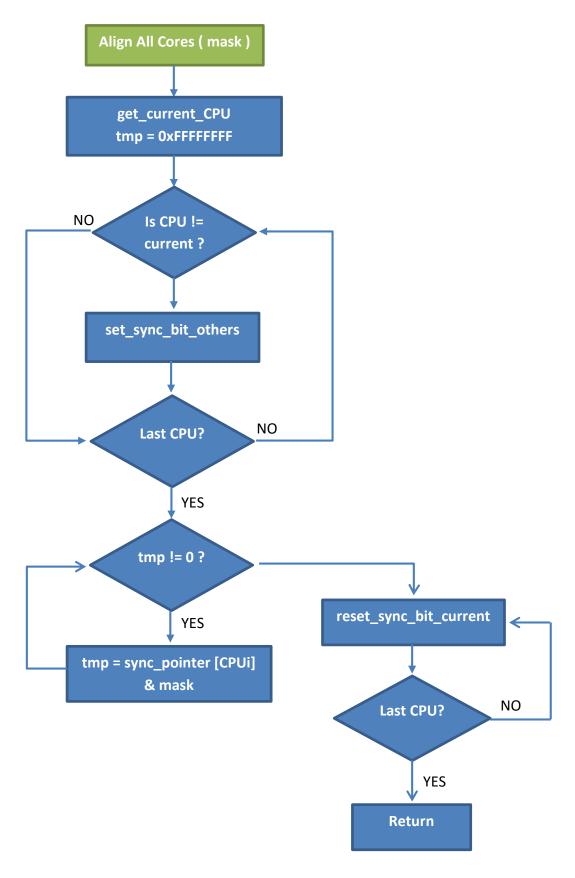

Figure 20: Verify function flowchart