## DIPARTIMENTO DI INGEGNERIA DELL'INFORMAZIONE

# CORSO DI LAUREA MAGISTRALE IN INGEGNERIA ELETTRONICA

# "WAVEFORM ENGINNERING IN INTEGRATED HARMONIC OSCILATORS: ANALYSIS AND EXAMPLES"

## "INGEGNERIZZAZIONE DELLE FORME D'ONDA NEGLI OSCILLATORI ARMONICI INTEGRATI: ANALISI ED ESEMPI"

Relatore: Prof. Andrea Bevilacqua

Laureando:Bellemo Luca

ANNO ACCADEMICO 2022 – 2023 Data di laurea 07/09/2023

#### **Abstract**

This thesis analyzes the effect of the presence of a second harmonic resonance in the differential LC oscillator, starting form the first intuitive idea that leads to the usage of it and going inside the different effects that it causes on waveform's shapes and phase noise improvement, considering different mechanisms. The analysis is carried out starting from the easiest topology of harmonic oscillator, giving general condition under which this technique has a practical advantage or not, even in other oscillator topologies. The thesis is closed with a practical example where all previously illustrated concepts are used.

# **Contents**

| 1 | Prel                    | Preliminaries on Digital Communication Systems |                                                       |          |  |  |  |  |

|---|-------------------------|------------------------------------------------|-------------------------------------------------------|----------|--|--|--|--|

|   | 1.1                     | Digital modulation                             |                                                       |          |  |  |  |  |

|   |                         | 1.1.1                                          | Digital Demodulator                                   | 5        |  |  |  |  |

|   |                         | 1.1.2                                          | The minimum distance receiver                         | 7        |  |  |  |  |

|   |                         | 1.1.3                                          | Effects of phase noise                                | 7        |  |  |  |  |

| 2 | Inte                    | Integrated LC Harmonic Oscillators             |                                                       |          |  |  |  |  |

|   | 2.1                     | Genera                                         | al structure of harmonic oscillators                  | 10       |  |  |  |  |

|   | 2.2                     | The C                                          | ross-Coupled Pair                                     | 11       |  |  |  |  |

|   | 2.3                     | The C                                          | lass-B oscillator                                     | 13       |  |  |  |  |

|   |                         | 2.3.1                                          | Oscillator's Steady State                             | 14       |  |  |  |  |

|   |                         | 2.3.2                                          | Current and voltage efficiency                        | 16       |  |  |  |  |

|   |                         | 2.3.3                                          | Current and Voltage Limited Regime                    | 17       |  |  |  |  |

|   |                         | 2.3.4                                          | Real behaviour of Steady State drain current          | 18       |  |  |  |  |

|   | 2.4                     | Phase                                          | Noise                                                 | 23       |  |  |  |  |

|   |                         | 2.4.1                                          | Effect of other noise sources                         | 30       |  |  |  |  |

|   |                         | 2.4.2                                          | Flicker Noise and effect of the common mode resonance | 31       |  |  |  |  |

|   |                         | 2.4.3                                          | The figure of Merit (FoM)                             | 32       |  |  |  |  |

|   | 2.5                     | Differe                                        | ent oscillator topologies                             | 32       |  |  |  |  |

| 3 | The class F2 oscillator |                                                |                                                       |          |  |  |  |  |

|   | 3.1                     | The id                                         | lea of introducing the second harmonic resonance      | 34       |  |  |  |  |

|   |                         | 3.1.1                                          | Class J waveform                                      |          |  |  |  |  |

|   |                         | 3.1.2                                          | Common mode resonance                                 |          |  |  |  |  |

|   | 3.2                     | Class 1                                        | F2 Waveform                                           |          |  |  |  |  |

|   |                         | 3.2.1                                          | Effect on drain current                               | 40       |  |  |  |  |

|   | 3.3                     | Tail ge                                        | enerator's noise reduction                            | 42       |  |  |  |  |

|   |                         | 3.3.1                                          | Class-B - Noise from bias current's generator         | 42       |  |  |  |  |

|   |                         | 3.3.2                                          | Tail's noise reduction with common mode resonance     | 44       |  |  |  |  |

|   | 3.4                     | Effect                                         | of second harmonic on noise tank                      | 45       |  |  |  |  |

|   | 3.5                     |                                                |                                                       |          |  |  |  |  |

|   |                         | 3.5.1                                          | Reduction of the noise from tail generator            | 48<br>48 |  |  |  |  |

|   |                         | 3.5.2                                          | Reduction of the overall noise coming from the tank   | 49       |  |  |  |  |

|   |      | 3.5.3     | Increasing in the current efficiency                                      | 52 |

|---|------|-----------|---------------------------------------------------------------------------|----|

|   | 3.6  | Chip ar   | rea saving of class-F2 oscillator                                         | 53 |

|   | 3.7  | Applic    | ation of the second harmonic resonance to other oscillator's topologies . | 54 |

| 4 | Desi | gn Issue  | es and an Example                                                         | 56 |

|   | 4.1  | The pro   | oblem of tuning                                                           | 56 |

|   |      | 4.1.1     | Discrete tuning                                                           | 58 |

|   |      | 4.1.2     | Fine tuning                                                               | 59 |

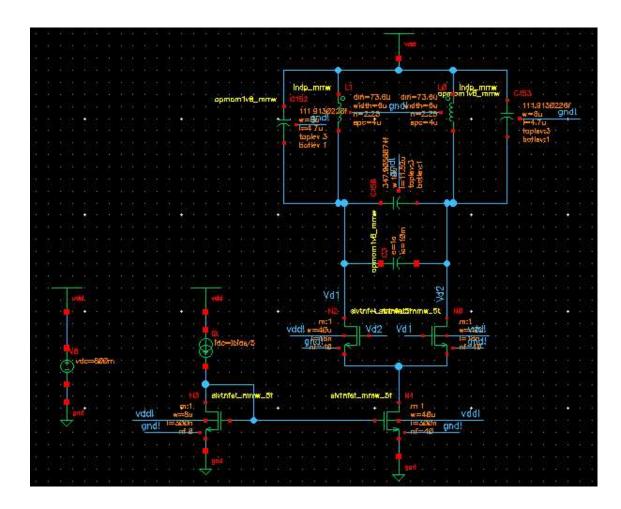

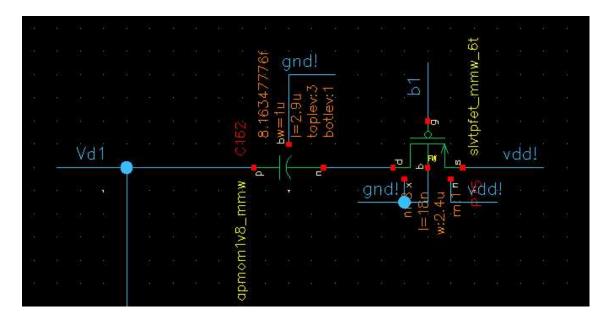

|   | 4.2  | Design    | Example                                                                   | 60 |

|   |      | 4.2.1     | Design procedure                                                          | 60 |

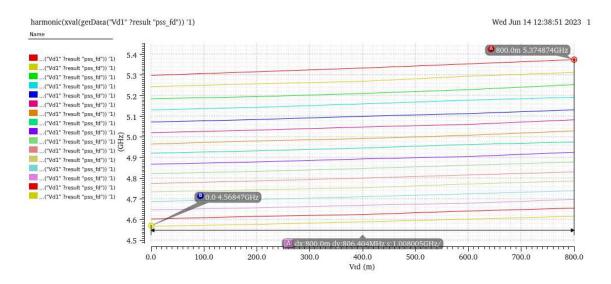

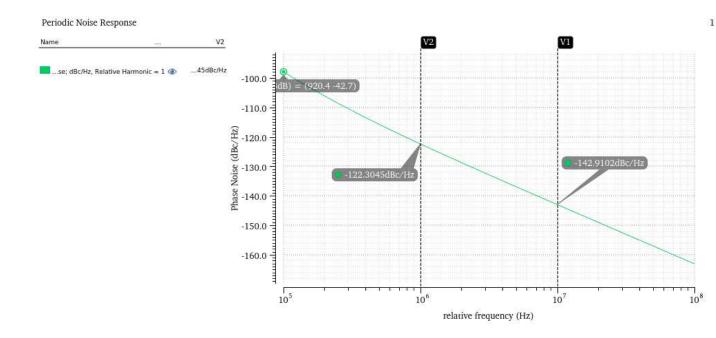

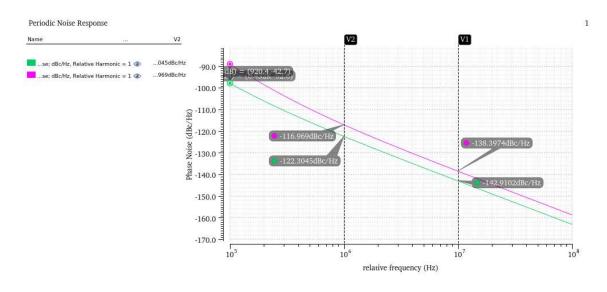

|   |      | 4.2.2     | Simulation Results                                                        | 63 |

| A | Sim  | ulation ( | of the noise factor                                                       | 1  |

## Introduction

Nowadays, most of communications systems are carried out using wireless technologies, which enable to exchange informations without complex infrastructures. However, wireless systems require a proper design of all the circuit that are part of the transmitter and receiver, taking into account all practical problems that are present. Most used radio communications technologies are nowadays digital, since this way to transmit information enables to reach higher speeds, and, since most of transmissions happen between digital systems (like computers), it's naturally to use such systems. Digital communication structures always require specific circuits, as briefly explained in the next chapter. One of the most critical component of every digital communication system is the oscillator, the circuit that provides to the other components a proper signal that is necessary for the functionality of the transmitter or the receiver. One of the most problems in designing wireless technologies is how to manage the presence of noise, which affects the signals present in the system, leading, in some cases, to limitation in the bitrate of the system or in the requirement, for it, to consume more energy. Noise sources are several: from electromagnetic interferences given by other analogous systems places in the neighborhood, to natural field always present, conditions of the medium (such as weather, ...) but also from the electronic noise sources present in all the circuits that are part of the transmitter and the receiver. Among all different types of noise sources in the system, this thesis will deeply study the effect that the noise has on the functionality of the oscillator, which is, as explained before, one of the most important block of all digital communication systems, concentrating on a way that can be used to reduce it and focusing on integrated solutions which are, nowadays, practically the only way used to realize wireless systems. The thesis is organized as follows: the first chapter shows, in general, how a digital communication system is realized, with a general review of most used digital protocols, focusing then on phase noise requirements of the local oscillator that must be satisfied for the proper working of the system. The second chapter introduces the well-known topology of the integrated class-B oscillator, including a brief review of other existing topologies developed to reach higher performances, with the full explanation of the most used theory on phase noise. In the third chapter the main idea of the thesis is presented, explaining how it's possible to use it an what are the advantages that it offers in term of phase noise, deriving all the conditions under which the ideas explained before are worth for a improvement of performances. Finally, the last chapter explains some practical problems and a complete example is shown.

# **Chapter 1**

# **Preliminaries on Digital Communication Systems**

In this section an introduction on digital communication systems is given. The following sections are not intended to be an exhaustive explanations of all details of digital communications, remanding to specialized books for further informations, but rather to be a small introduction to the Phase Noise problem that will be extensively discussed in the following chapters.

## 1.1 Digital modulation

A digital modulation is a way to transmit information in a different way with respect to analogue transmissions. When a digital modulation is used (in general not only in wireless systems), all informations are sent from the transmitter to the receiver in the form of a sequence of bit (called *bitstream*), that can, obviously, assume only two binary values (0/1). The principle of a digital modulation is to divide the input bitstream into groups of one ore more bit, choosing consecutive bits in the overall bitstream. For every of the different possible input sequence (called *symbol*) a different signal is associated via a biunivocal assignement, like the Example 1.1.1 clarifies.

#### **Example 1.1.1** (4 symbols digital modulation)

Considering to take consecutive pairs of two bits in the input bitstream, the association between the four possible combinations and its corresponding signals could be, for istance, the one shown in Table 1.1, where  $\omega = \frac{2\pi}{T}$ , with T is a given *symbol period*

| Input binary sequence | Associated signal       |

|-----------------------|-------------------------|

| 00                    | $s_1 = 2cos(\omega t)$  |

| 01                    | $s_2 = 3cos(\omega t)$  |

| 10                    | $s_3 = -2cos(\omega t)$ |

| 11                    | $s_4 = -3cos(\omega t)$ |

Table 1.1: Example of digital modulation using 4 symbols

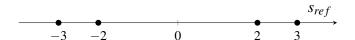

In this example, all four signals are multiple of a reference signal, in this case  $s_{ref}$

$\cos(\omega t)$ . It's important to notice that the reference signal is not necessary part of the modulation's set of signals, but it might be. This is a general property of the modulation's set of signals. As in the case of the Example 1.1.1, in a digital modulation, all chosen signals must be obtained via a linear combination of one or more reference signals, which constitutes the basis of the modulation. In the Example 1.1.1, the basis consists of an unique signal, but usually the basis can have dimension greater than one (a typical case is two). When more than one reference signal is chosen, they all must be linearly independent, meaning that the only linear combination that gives the zero signal is the one with all coefficients equal to zero. In this way every signal of the modulation can be expressed as a vector whose components are the coefficients of the linear combination of the signal of the basis that gives rise to a certain signal. Still considering the Example 1.1.1, the signal associated to the sequence "00", can be simply expressed via the number 2, with respect to  $s_{ref}$ . The working principle of a digital communication system is to transmit, either wireless or via a cable the different signals representing all the bits that must be sent to the receiver. Than, the receiver must use an appropriate circuit to understand which was the original signal to have been sent, reconstructing, symbol by symbol, the original bitstream. In the receiver, the presence of noise (from different sources) must be taken into account. The presence of the noise is what actually causes the fact that, sometimes, the receiver miss a correct reception of the right symbol.

## 1.1.1 Digital Demodulator

To understand the working principle of the receiver it's necessary to represent the different possible receivable signals in a graphical representation, where every signal is represented with its vector components with respect to the different elements of the basis. Example 1.1.2 shows the graphical representation of the signals of Example 1.1.1. This type of representation is usually known as *constellation* of the digital modulation. Example 1.1.3, instead, shows another example of modulation's constellation, where, in this case, the basis has dimension two.

#### Example 1.1.2

Considering the example 1.1.1, the constellation is shown in Figure 1.1

Figure 1.1: Constellation of Example 1.1.1

#### **Example 1.1.3** (4-QAM)

Considering now a different modulation, constituted by the four signals of Table 1.2, which shows also the vector representation with respect to the basis (1.1), where, again,  $\omega = \frac{2\pi}{T}$ , with T being a given symbol period. This type of modulation is known as *quadrature amplitude*

$$s_{ref1} = cos(\omega t); s_{ref2} = sin(\omega t)$$

(1.1)

| Input binary sequence | Associated signal                        | Vectorial representation w.r.t $(s_1, s_2)$ |

|-----------------------|------------------------------------------|---------------------------------------------|

| 00                    | $s_1 = cos(\omega t) + sin(\omega t)$    | (1,1)                                       |

| 01                    | $s_2 = cos(\omega t) - sin(\omega t)$    | (1,-1)                                      |

| 10                    | $s_3 = -\cos(\omega t) + \sin(\omega t)$ | (-1,1)                                      |

| 11                    | $s_4 = -\cos(\omega t) - \sin(\omega t)$ | (-1, -1)                                    |

Table 1.2: Example of digital modulation using 4 symbols and two reference signals

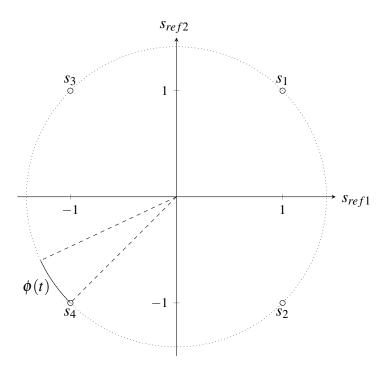

Figure 1.2: Constellation of Example 1.1.3, axis divide the plane into 4 decision regions

The goal of the demodulator is to understand, every symbol period, which was the original transmitted signal, given that the received signal is surely affected by **noise**, which is added to the received signal. The working principle of a digital demodulator is to divide the plane of the constellation in some regions, called *decision regions*. For istance, in the Figure 1.2, the axis divide the plane into 4 different decision regions (corresponding, in this case, to the four quadrants), each including one of the symbols. When a signal, which includes noise, is received, the components along the elements of the basis are calculated. Then, based on the position of the found point in the constellation, the demodulator understands what was the signal **probably** sent. The effect of noise (of any type) is to move the signal's point in the constellation from the original position to another one. If the other position is still contained in the decision region belonging to the transmitted symbol, the symbol is received correctly. In other cases, the receiver makes an *error*.

### 1.1.2 The minimum distance receiver

The way to associate the received signal to one of the symbols of the constellation are many, one of these is the *minimum distance* receiver. The way it works is dividing the constellation into decision regions in such a way that the symbol associated to a received signal (that includes noise) is the one which has the *minimum distance* (in sense of euclidean distance) in the constellation, like the Figure 1.2 already shows. To perform this analysis the receiver must, as first step, find the component of the received signal  $S_r$  along all the reference signals of the basis. The generic i-th component of the signal  $S_r$  along the reference signal  $S_i$  is:

$$S_i = \frac{1}{E_{s_i}} \int_0^{t=T} S_r(t) \, s_i(t) dt = \tag{1.2}$$

where  $E_{s_i}$  is the *energy* of the reference signal  $S_{ref}$ , namely the integral over a period of its square. So the receiver must include, for every element of the basis, at first a component, called *mixer*, that does the multiplication inside the integral in (1.2), then an integrator that integrates the result, followed by a sampler that samples the output of all integrators to find the values of the component at time t = T. A proper circuit calculates the distance of the signal from every symbol of the constellation outputting the right value that follows the minimum distance rule.

## 1.1.3 Effects of phase noise

As seen before, the presence of noise can move the point on the constellation and cause an error. Noise can come from different noise sources, but this thesis will concentrate only on phase noise, explaining, in an intuitive way, why its value is important in digital communication systems. Considering again the Example 1.1.3, the receiver must multiply the received signal by a cosine and a sine, in order to reconstruct the two components of the transmitted signal. To generate that reference signal, a *local oscillator* is used, which generates the reference signal  $s_{ref1}$ .

$$s_{ref1} = cos(\omega_0 t) \tag{1.3}$$

The signal  $s_{ref2}$  is always obtained by simply phase shifting  $s_{ref1}$  by 90° using an appropriate circuit. However, the oscillator, as all other electronic circuits, has some noise. For this reason, the signal generated by it is actually:

$$s_{ref1}^* = cos(\omega_0 t + \phi(t)) \tag{1.4}$$

where  $\phi(t)$  is a random signal due to the presence of the noise. The reason why noise affects only the phase of (1.4) will be clear in the next Chapter. To understand what happens when  $s_{ref1}^*$  is used in place of  $s_{ref1}$ , the situation when there are no other noise sources is considered. The effect of the presence of a random phase disturbance is a movement of the point inside the constellation into a location different from the place where the received signal should be, along a circle centered in the origin and passing through the point itself, as Figure 1.3 clarifies. If, then, other noise sources are present, the effects sum up in the vector sense.

Figure 1.3: Effect of phase noise in the case of a 4-QAM digital modulation, in this case the reception of  $s_4$  is taken as example, while  $\phi(t)$  is the effect of phase noise

The amount of difference in point's position on the constellation depends on the statistical properties of  $\phi(t)$ , in particular its variance. If the variance is high, the point moves along the circle more, eventually causing a receiving error to happen more frequently.

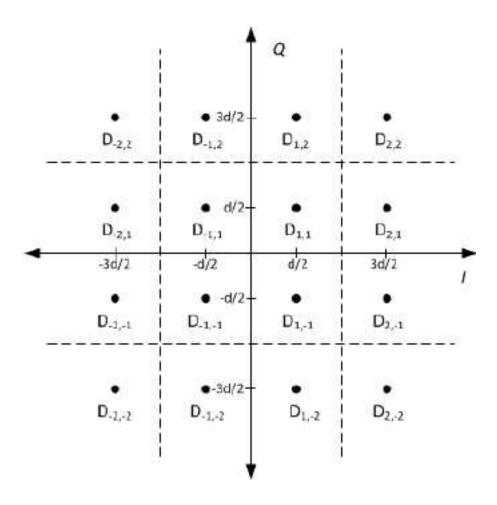

When the requirements on bitrate become higher, usually more symbols are added to the constellation, to increase the number of bits sent for every period. For example, Figure 1.4 shows the constellation of a 16-QAM modulation. It's clear that, in this case, requirements on noise are more strict than 4-QAM. A 64-QAM will then require further strict specifications, and so on. Table 1.3 summarizes the phase noise requirements for some standardized wireless communication systems. It's evident the fact that, over the years, specifications are becoming more and more strict, requiring a research activity to develop oscillators capable to reach such values<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>Since, as extensively discussed in Chapter 2, the effect of the disturbance is to create nonzero frequency components at frequencies different from  $\omega_0$ , phase noise is practically always expressed as the ratio between the power of the noise component at a given *offset frequency* from  $\omega_0$  and the power of the sinusoidal carrier. In this way specifications in Table 1.3 are given, too.

Figure 1.4: Constellation of a 16-QAM, where dashed line separate the decision regions. It's clear that the system is more sensitive to phase noise, that must be lower

| Standard          | Year | Oscillator's   | Phase Noise re- | Corresponding    |

|-------------------|------|----------------|-----------------|------------------|

|                   |      | frequency      | quirement       | offset frequency |

| Bluetooth 1.0 [1] | 1999 | 2.4GHz         | -111dBc/Hz      | 3МН г            |

| E - GSM [2]       | 1999 | 900 <i>MHz</i> | -141dBc/Hz      | 3MHz             |

| RFID [3]          | 2007 | 900 <i>MHz</i> | -109dBc/Hz      | 80 <i>kHz</i>    |

| 5G [4]            | 2017 | 20GHz          | -117dBc/Hz      | 1MHz             |

Table 1.3: Phase Noise requirements for some wireless communication standards

# Chapter 2

# **Integrated LC Harmonic Oscillators**

## 2.1 General structure of harmonic oscillators

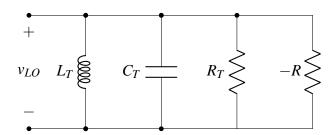

An *harmonic oscillator* is a circuit capable to continuously provide a sinusoidal (from which "harmonic") waveform without any external input. The general structure of an oscillator is the one reported in Figure 2.1 [5]. It's important to notice that model explained in Figure 2.1 refers to the so called *negative resistance* structure. Harmonic oscillators can be also viewed as particular feedback circuits, however, for oscillators that will be discussed now on, the negative resistance approach is highly recommended and gives simpler analysis.

Figure 2.1: General structure of harmonic oscillators

The general working principle of an oscillator is the presence of a LC tank, which has some losses elements, represented, in Figure 2.1, by the equivalent parallel resistance  $R_T$ . A negative resistance, realized with active components, compensates the positive resistance of the tank in such a way to make the overall system unstable, letting an oscillation to start. Considering the circuit above, the impedance of the overall circuit is given by:

$$Z = \left(\frac{1}{sL_T} + sC_T + \frac{1}{R_T} - \frac{1}{R}\right)^{-1} = \frac{sL_TR_TR}{R_TR + s^2L_TC_TR_TR + sL_T(R - R_T)}$$

(2.1)

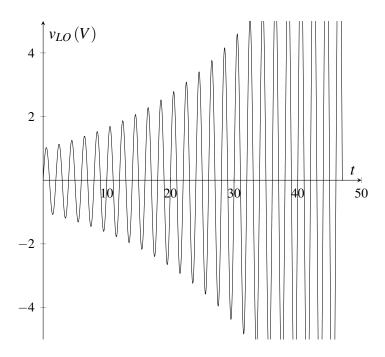

As clear form (2.1), the system, if  $R > R_T$ , is unstable, since the poles have positive real part, and an oscillation at frequency  $\omega_0 = \frac{1}{\sqrt{L_T C_T}}$  starts, as shown in Figure 2.2. From a linear point of view, oscillation should grow in amplitude indefinitely. Actually, in a real circuit, nonlinearities become more effective as the amplitude of the oscillation increases, limiting it to a certain value at the point where the oscillator reaches the so-called *Steady State*. However, to

properly understand the behaviour of the oscillator in steady state, the practical implementation of the principle schematic of Figure 2.1 must be analyzed, since different topologies lead to different steady state conditions.

Figure 2.2: Behaviour of  $v_{LO}$  when the system is unstable. Oscillations start with  $\omega_0 \simeq 3.14 \, rad/s$  (in this example). Notice that, theoretically, there's no limit in the amplitude of the oscillation.

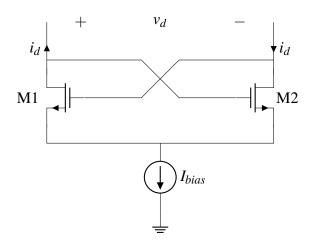

## 2.2 The Cross-Coupled Pair

The ways to implement the negative resistance are many different. However, in integrated harmonic oscillators most of the time it's implemented via two transistors (either MOS or bipolar), connected as shown in Figure 2.3, realizing the so-called *cross-coupled pair*. This type of circuit, where, of course, the bias current generator is realized with a proper current mirror, can easily implement a *differential* negative resistance, namely that the *differential* voltage  $v_d$  is proportional to the current  $i_d$  via a negative constant (at small signals). Since the bias current generator is an open circuit at small signals, the currents flowing into the drain of two devices are the same but with opposite direction.

Figure 2.3: General structure of the cross-coupled pair

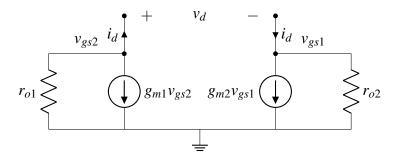

To analyze the cross-coupled pair and calculate the value of its negative resistance, it's necessary to move to its equivalent small signal circuit of Figure 2.4, where parasitic capacitances are not shown since they can be embedded in the tank capacitance  $C_T$ .

Figure 2.4: Equivalent small signal circuit of the cross-coupled pair

For the symmetry of the circuit and the voltages, the common source is an *ac ground*, for differential signals only. The gate to source voltages are:

$$v_{gs2} = -v_{gs1} = \frac{v_d}{2} \tag{2.2}$$

From which, considering, for istance, the left branch of Figure 2.4:

$$i_d = -\left(\frac{v_d}{2r_{o1}} - g_{m1}\frac{v_d}{2}\right) = \frac{v_d}{2}\left(\frac{1}{r_{o1}} - g_{m1}\right)$$

(2.3)

The differential resistance seen at the port is then:

$$R_d = \frac{v_d}{i_d} \simeq -\frac{1}{g_m} \tag{2.4}$$

Since, in (2.3),  $r_{o1} >> 1/g_{m1}$ , and the two devices are supposed to have the same small signal transconductance  $g_m = g_{m1} = g_{m2}$

## 2.3 The Class-B oscillator

Hence, it has been shown that the cross-coupled pair can provide a negative resistance, whose value depends on the transconductance of the device used to create it. With this structure, one can finally arrive to the general structure of the first oscillator topology, largely used especially in integrated oscillators, which is composed by a tank whose differential behaviour is equal to the one of Figure 2.1, and a cross-coupled pair used to realize the appropriate negative resistance. The so obtained oscillator is also known as  $Class\ B\ oscillator$ , and it's shown in Figure 2.5, where the current source has been replaced with a current mirror, the resistance  $R_T$  is actually created by the equivalent parallel of the inductance's series resistance, given by (2.5), and the inductor has been split into two halves, to let the bias current properly flow from the supply to the cross-coupled pair's devices.

$$R_T \simeq Q_L^2 * R_{sL} \simeq Q_L \omega_0 L_T \tag{2.5}$$

Figure 2.5: Complete circuit of the class-B oscillator. The reference branch of the current mirror is not shown

As explained before, there's no explicit resistor in the tank, but the resistive component shown in Figure 2.1 is created using the losses of the inductors. In fact, the more the inductor is ideal, the higher is the equivalent parallel resistance (since Q in (2.5) increases), leading to higher oscillation amplitudes, as explained in the next subsection.

## 2.3.1 Oscillator's Steady State

If the condition for the instability of the system whose general transfer function is the one in (2.1) is met, the oscillation starts, theoretically diverging to infinite amplitudes. In reality, nonlinearities of the devices limit the amplitude of the oscillation in such a way that, after a given amount of time, the oscillator reaches a *Steady State* condition, where the oscillation's amplitude is stable. This is mainly due to the behaviour of the devices forming the cross-coupled pair. When the amplitude of the gate to source voltages increases, that devices start to operate in the triode region, so decreasing the value of  $g_m$ , leading to a stable oscillation amplitude<sup>1</sup>.

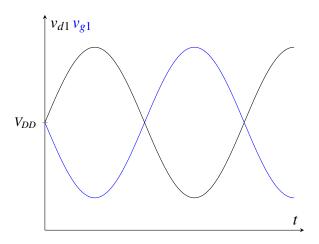

When the steady state condition is reached, both drain nodes oscillate with a given amplitude equal to  $V_{LO}/2$  with respect to ground.  $V_{LO}/2 = V_o$  is known as *single ended* amplitude, while  $v_{LO}$  is the differential voltage, oscillating with an amplitude equal to double the single ended one. Since the gate of a device is connected to the drain of the other one, waveforms at the drain and gate terminals of a device are reported in Figure 2.6. As clearly visible, when the oscillation's amplitude reaches steady state, the devices forming the cross-coupled pair operates with gate and drain voltages given by (2.6) and (2.7), where the mean value of the drains' voltages is  $V_{DD}$  and the single ended oscillation's amplitude is  $V_{LO}/2$

$$v_g = V_{DD} - \frac{V_{LO}}{2} sin(\omega_0 t) \tag{2.6}$$

$$v_d = V_{DD} + \frac{V_{LO}}{2} sin(\omega_0 t)$$

(2.7)

In the steady state condition, the two transistors of the cross-coupled pair operate alternatively in triode region or in the OFF region. This behaviour is known as *Hard Switching* and the oscillator in steady state is properly modelled as shown in Figure 2.7, where switches and their parasitic resistance equivalently model the transistor in triode region. Moreover, if the capacitor is considered to be split in a series of two equal capacitors with double value, the point between them is a differential ac ground.

<sup>&</sup>lt;sup>1</sup>In some topologies, different from the class-B, oscillation's amplitude might be, under some conditions, unstable

Figure 2.6: Class-B Steady State waveform, with  $V_{DD} = 1V$

Figure 2.7: Equivalent Steady State model of the class-B oscillator, where both the supply and the midpoint of the two capacitors representing  $C_T$  are AC grounds. Every half a period, one of the two switches (transistors) is ON while the other is OFF, and viceversa

From Figure 2.7, it's clear that the current flowing into the two terminals of the tank is **ideally** (as clear later) a squarewave ranging from 0 to  $I_{bias}$ , with a period equal to the period of the oscillation. At  $\omega_0$ , both the halves of the tank, redrawn as in Figure 2.7, operate in resonance, so they display an impedance equal to  $R_T/2$ , where  $R_T$  is the equivalent parallel resistance of (2.5), at the frequency  $\omega = \omega_0$ , and a low impedance for all other frequencies multiples of  $\omega_0$  (the out-of-resonance impedance is actually capacitive for  $\omega > \omega_0$ , but in this approximate analysis it's considered to be zero). Since the current is a periodic signal, it can be decomposed into its harmonic components. In particular, the amplitude of the first current

harmonic is:

$$I_1 = \frac{2}{\pi} I_{bias} \tag{2.8}$$

while further harmonics are irrelevant since they are multiplied by the impedance of the tank out of resonance, which results in a very low (ideally zero) voltage at the two drains. It's now easy to find the expression of  $v_{d1} = -v_{d2}$ :

$$v_{d1} = \frac{R_T}{2} I_1 sin(\omega_0 t) = \frac{2}{\pi} I_{bias} \frac{R_T}{2} sin(\omega_0 t)$$

(2.9)

where the fact that only half of the inductor is present at any of the two halves of the circuit has been used. From (2.9) the amplitude of the differential oscillation is:

$$V_{LO} = V_{d1} - V_{d2} = \frac{2}{\pi} R_T I_{bias}$$

(2.10)

## 2.3.2 Current and voltage efficiency

Analyzing the equation (2.10), it's possible to define some parameters used to characterize different oscillator topologies that are nowadays available, different from the traditional class-B. In any oscillator which contains a bias generator at the common source of the cross-coupled pair, the final oscillation's amplitude is always function of the first harmonic current's value  $I_1$ . The difference among various oscillator topologies is in the shape of the drain current of the devices at steady state, which can be different from the square wave of Class-B oscillator. For this reason, the *current efficiency* is defined by (2.11), quantifying how much the bias current is converted into first harmonic current (the only one that is further converted into a voltage).

$$\eta_I := \frac{I_1}{I_{bias}} \tag{2.11}$$

For the class-B,  $\eta_I = \frac{2}{\pi} \simeq 0.64$ , at least **theoretically**. For a real circuit, actually  $\eta_I \sim 0.55$ . Another situation that limits the amplitude of the oscillation is the fact that the lower limit of  $v_{d1}$  and  $v_{d2}$  cannot be the ground voltage. In fact, as clear from Figure 2.6 there must be enough "space" between the minimum value of  $v_{d1}$  or  $v_{d2}$  to guarantee the operation in saturation of the current mirror and the presence of a voltage across the devices operating in triode. For this reason, the maximum single ended swing is lower than  $V_{DD}$ . Letting  $V_{o_{max}}$  be the maximum single ended oscillation's swing, (2.12) defines the *voltage efficiency*.

$$\eta_V := \frac{V_{d_{max}}}{V_{DD}} \tag{2.12}$$

For the class-B,  $\eta_V = (V_{DD} - r_{on}I_{bias} - V_{mirror}^*)/V_{DD}$ ,  $V_{mirror}^*$  being the minimum voltage required by the mirror to keep itself in saturation.

With the above definitions  $V_{LO}$  can be expressed as:

$$V_{LO} = \eta_I R_T I_{bias} = 2\eta_V V_{dd} \tag{2.13}$$

It's important to notice that (2.13) is valid for any oscillator topology, given that  $\eta_I$  and  $\eta_V$

have been properly defined. Table 2.3.2 shows the typical value of the above defined parameters for some typical oscillator topologies. The *class-F2* oscillator is the one which constitutes the main part of the following chapters.

| Oscillator Topology | $\eta_I$    | $\eta_V$             |

|---------------------|-------------|----------------------|

| Class B             | $\sim 0.55$ | $\sim 0.6 \div 0.8$  |

| Class-C             | ~1          | $\sim 0.9$           |

| Class-D             | ~ 1.5       | $\sim 1.5$           |

| Class-F2            | $\sim 0.6$  | $\sim 0.75 \div 0.8$ |

Table 2.1: Typical values of voltage and current efficiency for different oscillator topologies. Values of voltage efficiency assume  $V_{DD}$  to be in the range  $0.8 \div 1.2V$

## 2.3.3 Current and Voltage Limited Regime

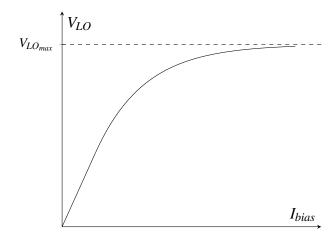

The behaviour of the oscillator modelled as in Figure 2.7 is valid if the tail's transistor operates in saturation for the entire period. This operation region is called *current limited regime*. If  $I_{bias}$  is increased, the amplitude of the oscillation is increased up to a point where the tail device enters the triode region for part of the cycle. If the current is further increased, that device is always in the triode region and the bias current cannot increase anymore, reaching the maximum possible value of it. This operating condition is called *voltage limited regime* and the tail generator could be also removed, leading to the class-D topology, where the value of the bias current cannot be controlled. Between these two regions, there exist a transition region where the tail's device enters triode only for part of the cycle. The dependence of the output amplitude on the average value of the tail's device current is shown in Figure 2.8, where the slope of the linear part of the graph should be in theory  $(2/\pi)R_T$ .

Figure 2.8: Differential amplitude with respect to the bias current

## 2.3.4 Real behaviour of Steady State drain current

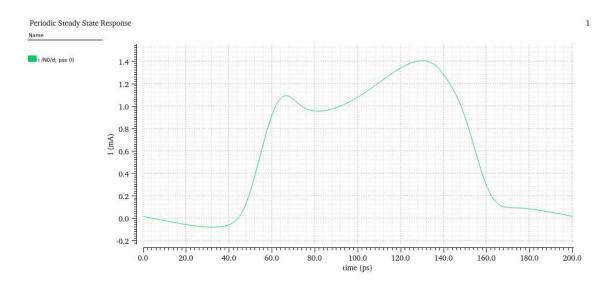

In a real circuit, the waveform of the drain current of the cross-coupled pair's devices<sup>2</sup> is not a square wave anymore. In fact, the transition of that devices between the active and the triode region, together with the parasitic capacitance of the current mirror, shapes the drain current in a way that is different from a squarewave. Example 2.3.1 show a simulation of a real circuit where this fact is shown.

#### Example 2.3.1 (Class-B Drain Current)

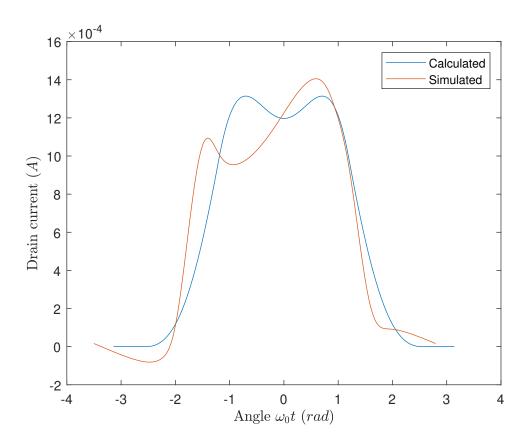

Just as an example, a real circuit employing the 22-nm GlobalFoundries technology is simulated, using ideal components for the tank, with  $L_T = 400pH$ ,  $C_T = 2.53pF$  (this values gives  $\omega_0 \simeq 5GHz$ ),  $R_T = 1k\Omega$  and real transistors for the cross-coupled pair and the bias current generator. The bias current is fixed to  $I_{bias} = 1.2mA$ , resulting in a theoretical oscillation amplitude of  $V_{LO} = 750mV$ . The dimensions of the cross-coupled pair's devices are  $(W = 8\mu m, L = 18nm)$ , allowing a ON voltage of  $\simeq 50mV$ , while the tail generator has  $(W = 8\mu m, L = 300nm)$  as dimensions, allowing it to always work in saturation. Figure 2.9 shows the simulated current which is not a squarewave at all. Moreover, the simulated oscillation amplitude is 711mV, which gives  $\eta_I = 0.59$ , lower than the theoretical one.

Figure 2.9: Simulated current waveform of the oscillator of Example 2.3.1

A detailed theoretical analysis of the waveform of Example 2.3.1 can be made only in an approximate way, which makes use of the long channel model for the transistor of the cross-coupled pair [6]. For more accurate models one should use the proper short channel model (especially if deep-scaled technologies are used). However, still with the long channel model calculations are quite complex and, at the end, it's still necessary to use numerical simulations to solve the final equation since, as it will be clear, it has not a closed form solution.

To analyze theoretically the current's waveform, at least in an approximate way, some hypothesis (not always perfectly true) are made:

• cross-coupled pair's transistors follow the long channel model;

<sup>&</sup>lt;sup>2</sup>In many works, devices creating the cross-coupled pair are called *gm-devices*

• The parasitic drain-to-bulk capacitance of the tail generator is large enough to be assumed as a short circuit at  $\omega_0$ .

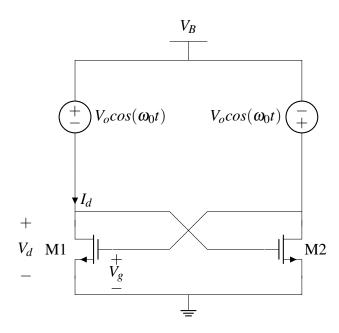

The second point allows to consider the voltage of the common source  $V_S$  to be constant, in general different from the bias point's value. To study the circuit, it's convenient to move the reference point of voltages to the common source, studying the circuit of Figure 2.10, where, since the interest is on the drain current, the tank has been substituted with a sinusoidal voltage source with the right amplitude. Moreover, moving the reference to the common source will change  $V_{DD}$  to  $V_{DD} - V_S$ . Obviously, changing the reference doesn't change the values of currents.

Figure 2.10: Circuit used to calculate the drain current, with the reference on the common source

With respect to Figure 2.10, and focusing only on one device (for istance M1), drain and gate voltages are, respectively:

$$V_d = V_{ds} = V_B - V_o cos(\omega_0 t) \tag{2.14}$$

$$V_g = V_{gs} = V_B + V_o cos(\omega_0 t)$$

(2.15)

defining  $V_B := V_{DD} - V_S$ .

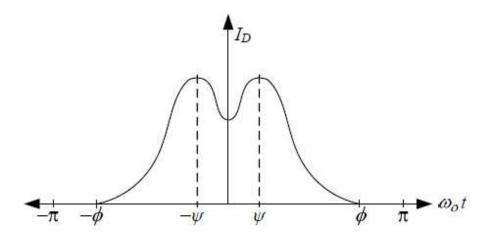

The current waveform can be decomposed into some regions, as explained in Figure 2.11. In Figure 2.11, the three operating regions of the transistor are highlighted. Referring only to positive values of  $\omega_0 t$ , for angles between 0 and  $\Psi$  the transistor operates in triode region, between  $\Psi$  and  $\phi$  it operates in saturation, for the remaining part of the period it's off. For the other transistor of the cross-coupled pair the situation is the same, with a  $\pi$  angle shift only in the angles axis. For this reason, considerations below always refers to one transistor. Using

long channel model, and defining  $\beta = \mu C_{ox}W/L$ , the steady state current of the transistor can be expressed as function of drain and gate voltages as:

$$\begin{cases} I_d = \beta (V_{gs} - V_T)^2 & \text{Saturation region} \\ I_d = \beta ((V_{gs} - V_T)V_{ds} - V_{ds}^2/2) & \text{Triode region} \\ I_d = 0 & \text{Off region} \end{cases}$$

(2.16)

Figure 2.11: Behaviour of the drain current according to the approximate model of [6]

In any case, the average drain current  $I_D$  of the transistor is imposed by the tail generator to be  $I_{bias}/2$ .

$$I_D = I_{bias}/2 = \beta (V_{GS} - V_T)^2 \tag{2.17}$$

where  $V_T$  is the threshold voltage. From (2.17), the bias point gate-to-source voltage  $V_{GS}$  is:

$$V_{GS} = \sqrt{I_D/\beta} + V_T \tag{2.18}$$

Taking the ratio between the equation (2.16), in saturation region, and (2.17), and using the expression of  $V_{gs}$  given by (2.15), one gets:

$$\frac{I_d}{I_D} = \left(\frac{V_B}{V_{GS} - V_T} + \frac{V_o}{V_{GS} - V_T} cos(\omega_0 t) - \frac{V_T}{V_{GS} - V_T}\right)^2$$

(2.19)

which is valid in **saturation** region. In triode region, with a similar reasoning, equation (2.19) becomes:

$$\frac{I_d}{I_D} = \frac{V_B + V_o cos(\omega_0 t) - V_T}{V_B - V_T} \frac{V_B - V_o cos(\omega_0 t)}{V_{GS} - V_T} - \frac{1}{2} \left( \frac{V_B - V_o cos(\omega_0 t)}{V_{GS} - V_T} \right)^2$$

(2.20)

To find the limit angle between triode and saturation regions, it's necessary to consider that the device enters saturation from triode when  $V_d = V_g - V_T$ , which implies, using (2.14) and (2.15):

$$\psi = \cos^{-1}\left(\frac{V_T}{2V_o}\right) \tag{2.21}$$

While imposing the drain current in saturation given by (2.19) to be zero, one gets:

$$V_B = V_T - V_o cos(\phi) \tag{2.22}$$

However, since  $V_B$  is not known, it's necessary to find a different way for the calculation of  $\phi$ . In particular, the average drain current is found by piecewise integrating (2.16) and equating it with the average current value given by (2.17).

$$I_{bias}/2 = \int_0^{\Psi} I_{d_{triode}} + \int_{\Psi}^{\phi} I_{d_{sat}}$$

(2.23)

After some steps [6], an expression containing only  $\phi$  as unknown is obtained:

$$\pi = \frac{V_o^2}{(V_{GS} - V_T)^2} \left[ \frac{\phi}{2} - 2\psi - \frac{3}{2} sin(\phi) cos(\phi) + \phi cos^2(\phi) - 2 cos(\psi) sin(\psi) \right] + 4 \frac{V_o V_T}{(V_{GS} - V_T)^2} sin(\psi) + \frac{V_o^2}{(V_{GS} - V_T)^2} \psi$$

$$- \frac{V_T^2}{(V_{GS} - V_T)^2} \psi$$

(2.24)

which can be solved numerically to find the value of  $\phi$ .

Once  $\psi$  and  $\phi$  has been obtained,  $V_B$  can be simply found using (2.22).

At this point, having all expressions of  $V_d$ ,  $V_g$  and  $V_B$ , it's possible to explicit find the drain current in all three operating regions, by simply multiplying (2.19) and (2.20) by the average drain current  $I_D$ . Figure 2.12 shows the result of the calculation for Example 2.3.1, it's possible to notice the differences between simulation and theory.

Figure 2.12: Comparison of drain current's approximate analysis with the values of Example 2.3.1, compared with the result of the simulation

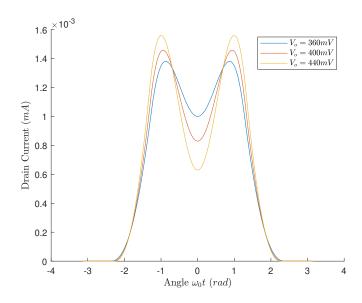

It's clear that the theory is quite complex and it doesn't still provide enough accurate results. For this reason, in all practical design problems it's never used and simply some margin on  $\eta_I$  is considered, given that it's lower than  $2/\pi$ . However it can be useful to understand how the current's shape and spectrum depend on the shape of  $V_d$  and  $V_g$ . For istance, Figure 2.13 provides the current waveform for different values of  $V_o$ , while in Table 2.2 the corresponding Fourier coefficients are reported. It's noticeable that, the more the transistor enters the triode region, the higher is the value of the second harmonic, while the first slightly gets lower, since the waveform differs from the ideal squarewave more.

Figure 2.13: Effect of the value of  $V_o$  on the shape of the drain current, whith  $I_{bias} = 1.2 \text{mA}$

| Amplitude $V_o$ | First harmonic $ I_1 $ | Second harmonic $ I_2 $ |

|-----------------|------------------------|-------------------------|

| 360 mV          | 729 µA                 | 28 μΑ                   |

| 400 mV          | 702 μΑ                 | 99 μΑ                   |

| 440 mV          | 669 μΑ                 | 184 μΑ                  |

Table 2.2: Effect on the first and the second harmonic of the drain's current, considering  $I_{bias} = 1.2mA$ , according to the approximate theory

## 2.4 Phase Noise

In this section the effects on the oscillator of the noise generated by various noise sources present in the circuit is analyzed. Since, as it will be clear, the effect of the noise can be viewed as a perturbation in the phase of the oscillation, while it does not affect its amplitude, noise in electronic oscillators is referred as *Phase Noise*<sup>3</sup>. Main noise sources in an oscillator are:

- Lossy components of the tank  $(R_T)$ ;

- Noise generated by cross-coupled pair's devices;

- Noise generated by the bias circuit;

Different theories allowing the study of the phase noise have been developed since 90s, going from intuitive approaches to extremely rigorous approaches making use of the theory of Linear-Time-Variant systems. The theory it's going to be presented is the one by Hajmiri and Lee [7],[8], widely used to analyze oscillators in a decently rigorous way. Next, a more general theory, that considers also the harmonics of the output voltage different from the first, will be briefly presented, too.

<sup>&</sup>lt;sup>3</sup>"PN" in the following

Considering a generic oscillator, it's easy to understand that noise may, in principle, change both the amplitude and the phase of the output sinewave. However, amplitude's variation are compensated by nonlinearities of the circuit, reaching a condition in which oscillation's amplitude is stable<sup>4</sup>, so the relevant perturbation due to noise is the one on the phase. For this reason, the output voltage can be expressed as:

$$v_{LO} = V_{LO}cos(\omega_0 t + \phi(t)) \tag{2.25}$$

where  $\phi(t)$  is a random phase perturbation caused by noise. Since  $\phi$  is a random signal, the spectrum of  $v_{LO}$  is not a single line at  $\omega_0$  but it displays some nonzero components also at values close to  $\omega_0$  but different from it by an *offset frequency*  $\Delta \omega$ , operating as a phase modulation. For any offset frequency  $\Delta \omega$ , it's possible to find a value for the power spectral density of the output signal  $v_{LO}$ ,  $S_{v_{LO}}(\omega_0 + \Delta \omega)$ . This is a value expressed in  $[V^2/Hz]$ , but it's usually expressed with respect to the power of the carrier defined as:

$$P_{carrier} = \frac{V_{LO}^2}{2} \left[ V^2 \right] \tag{2.26}$$

Furthermore, the ratio of the PSD of the noise with respect to the carrier's power is normally represented in a logarithmic scale, defining the noise, at  $\Delta\omega$  from the carrier, as:

$$L(\Delta \omega) = 10 \log_{10} \left( \frac{S_{\nu_{LO}}(\omega_0 + \Delta \omega)}{P_{carrier}} \right) [dBc/Hz]$$

(2.27)

Using dBc as unit of measurement, with the meaning of dB with respect to the power of the carrier (per unit frequency).

Any sinusoidal oscillator, regarding noise, can be represented with the block diagram shown in Figure 2.14, where it's possible to identify two main blocks:

- The first block converts the disturbance signal, represented with a noise current  $i_n$ , into the proper phase error.

- The second block converts the phase error into the output voltage, by simply calculating the value of the cosine function at the istantaneous phase properly accounting the phase error  $\phi(t)$

$$\begin{array}{c|c}

i_n(t) & \phi(t) \\

\hline

h_{\phi}(\tau) & cos(\omega_0 t + \phi(t)) \\

\end{array}$$

Figure 2.14: Block diagram of a generic harmonic oscillator used to study the effect of the noise

Focusing on the first block, the way the phase error is calculated is based on the so-called *ISF approach*, which is the main point of the Hajmiri and Lee theory [7]. The analysis of the

<sup>&</sup>lt;sup>4</sup>In some cases, oscillation amplitude may be unstable [9], however, this phenomenon happens when large tail capacitors are used, which is not the case of circuits presented in this thesis

phase noise is first carried out considering the noise coming from the tank **only**. The effect of noise coming from other sources is discussed later. Noise coming from the tank is only due to the equivalent parallel resistance  $R_T$ . Referring to the circuit of Figure 2.7, tank's noise is generated from the equivalent resistance of  $L_T/2$  inductor, namely  $R_T/2 = Q^2 R_{s_L}/2$ . Noise from a resistor can be modelled as a parallel current source injecting a noise current  $i_n$  with PSD:

$$S_{i_n} = \frac{4kT}{R_T/2} \tag{2.28}$$

where k is the Boltzmann constant and T is the absolute temperature. It's important to notice that the analysis is considering only the thermal noise. Furthermore, also flicker noise generated by active devices will be considered.

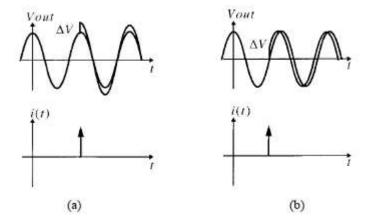

When a noise current is injected into a node of the circuit, the oscillation waveform is perturbed. First of all, an impulsive current's disturbance, injecting a charge q into a given node of the circuit is considered. The effect of perturbation depends on when the disturbance is injected with respect to the entire period of the oscillation. In fact, if an impulsive disturbance happens at the peak of the oscillation, it causes only an error in the amplitude of the waveform, not affecting the phase of it. On the contrary, a disturbance arriving when the oscillation crosses the mean value will cause the maximum possible phase error. Figure 2.15 clarifies this concept. For intermediate points the phase error caused by an impulse depends on when the impulse arrives. The function giving the phase error as a function of the time  $\tau$  when the impulse current arrives is called *Impulse Sensitivity Function* (ISF). It's a dimensionless function, with  $2\pi$  as period, giving the phase error with respect to the moment the impulse happens. The ISF' maximum value is equal to 1, namely that it's normalized to the maximum possible phase shift, no matter what it is. For a traditional class-B oscillator with cosinusoidal output waveform, the ISF of drain nodes is:

$$\Gamma(\tau) = \sin(\omega_0 \tau) \tag{2.29}$$

As clear from (2.29), an impulse of charge q has no effect on phase if it's injected at  $\omega_0 \tau = 0$ ,  $\pi$  (peak of oscillation), while the effect is maximum for  $\omega_0 \tau = \pi/2, 3\pi/2$ . In general, the calculation of the ISF is not simple, the rigorous derivation of (2.29) can be find in [7].

Figure 2.15: Effect of the same impulsive current at different moments inside the period of the oscillation. In case (a) there's no phase error, while in case (b) there's a phase error lasting indefinitevely

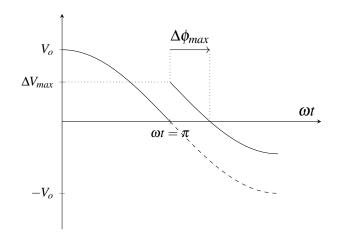

Referring to the block diagram of Figure 2.14, it's clear that the phase error  $\phi(t)$  is given by the response of the first block to a generic input current  $i_n$ , and it can be obtained via the convolution with the impulse response of the block  $h_{\phi}(t,\tau)$ . The impulse response of the block is the response of it when an unitary impulsive current injecting a total charge  $q=1C^5$  is given as input. Since q is injected in a infinitesimal amount of time, it causes a voltage variation on the tank's capacitor only, equal to  $\Delta V_{max}=q/2C_T$ . Then, since the ISF is normalized to the maximum possible phase shift if a charge q is injected, it's necessary to compute the maximum phase shift  $\Delta \phi_{max}$ . Looking at the ISF, the maximum phase error occurs when the sinewave crosses the zero level. In that condition, if an instantaneous voltage change, equal to  $\Delta V$  happens, the oscillation continues (with the phase error), reaching again the zero value after an amount of time which corresponds to the maximum phase error  $\Delta \phi_{max}$ , as clear from Figure 2.16. The phase error is:

$$\Delta V_{max} = -\frac{V_{LO}}{2} sin(\Delta \phi_{max}) \simeq \frac{V_{LO} \Delta \phi_{max}}{2}$$

(2.30)

<sup>&</sup>lt;sup>5</sup>The impulse response is defined as the response to a unitary impulse, namely a current  $i_n(t) = (1A)\delta(t)$ , whose area, representing the total injected charge, is 1C

Figure 2.16: Calculation of the maximum phase error

where the last step uses a first order approximation of the sine function. This is called the *linearity* approximation, which is practically always true, as widely demonstrated in the literature [7].

From (2.30), by solving for  $\Delta \phi_{max}$  and considering that  $\Delta \phi = \Delta \phi_{max} \Gamma(\tau)$ , the impulse response of the block converting the noise current into the phase error is:

$$h_{\phi}(t,\tau) = \frac{\Gamma(\tau)}{C_T V_{LO}} \delta_{-1}(t-\tau)$$

(2.31)

where  $\delta_{-1}$  is the step function. The meaning of (2.31) is that, before the moment of injection, there's no phase error. After the q impulse arrives, the phase error suddenly steps to the value given by the ISF, considering the maximum possible phase error. Once the impulse response in known, the output phase error is given by the usual convolution (2.32). Notice that that's valid only in linearity condition, even if the system is not time-invariant.

$$\phi(t) = \int_{-\infty}^{\infty} h_{\phi}(t,\tau) i(\tau) d\tau = \frac{1}{C_T V_{LO}} \int_{-\infty}^{t} \Gamma(\tau) i(\tau) d\tau$$

(2.32)

To easily calculated the integral in (2.32), it's necessary to express the ISF with its Fourier series, since it's a periodic signal:

$$\Gamma(\tau) = \frac{c_0}{2} + \sum_{n=1}^{+\infty} c_n \cos(\omega_0 t + \theta_n)$$

(2.33)

By inserting (2.33) into (2.32):

$$\phi(t) = \frac{1}{C_T V_{LO}} \left[ \frac{c_0}{2} \int_{-\infty}^t i(\tau) + \sum_{n=1}^{+\infty} c_n \int_{\infty}^t i(\tau) \cos(n\omega_0 \tau) d\tau \right]$$

(2.34)

Beside the computation of (2.34), it's important to analyze it to understand what's its practical meaning. To do this, the effect of a cosinusoidal disturbance  $i(\tau) = I_k cos((k\omega_0 + \Delta\omega)\tau)$ , of amplitude  $I_k$  and frequency  $\Delta\omega + k\omega_0$ , k = 1, 2, ..., namely a frequency close to the (fixed) k-th multiple of  $\omega_0$ , is analyzed. By inserting the expression of the current in (2.34):

$$\phi(t) = \frac{1}{C_T V_{LO}} \left[ \frac{c_0}{2} \int_{-\infty}^t I_k \cos((k\omega_0 + \Delta\omega)\tau) + \sum_{n=1}^{+\infty} c_n \int_{\infty}^t I_k \cos((k\omega_0 + \Delta\omega)\tau) \cos(n\omega_0\tau) d\tau \right]$$

(2.35)

$$\phi(t) = \left(\frac{1}{C_T V_{LO}}\right) \frac{c_0}{2} \int_{-\infty}^{t} I_k \cos(k(\omega_0 + \Delta \omega)\tau) + \sum_{n=1}^{+\infty} \frac{c_n}{2} \int_{\infty}^{t} I_k \cos((n-k)\omega_0 t + \Delta \omega)\tau) d\tau + \sum_{n=1}^{+\infty} \frac{c_n}{2} \int_{\infty}^{t} I_k \cos((n+k)\omega_0 t + \Delta \omega)\tau) d\tau + \sum_{n=1}^{+\infty} \frac{c_n}{2} \int_{\infty}^{t} I_k \cos((n+k)\omega_0 t + \Delta \omega)\tau d\tau$$

(2.36)

Moving to the frequency domain, the integral has a filtering effect. Since  $\Delta\omega$  is much lower than  $\omega_0$  (and therefore all its positive or negative multiples), the only relevant term in (2.36) is the one coming from the second integral, when n = k. All other terms give rise to harmonic components that are strongly attenuated in frequency by integration. Hence, the phase error associated to the injection of a sinusoidal disturbance at frequency close to the k-th multiple of the oscillation frequency  $\omega_0$  can be well approximated by:

$$\phi(t) \simeq \frac{I_k c_k \sin(\Delta \omega t)}{2C_T V_{LO} \Delta \omega} \tag{2.37}$$

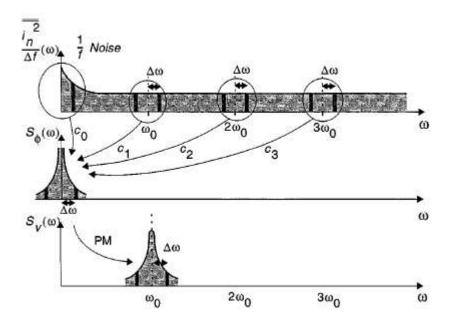

Since the noise is not constituted by a single spectral line but rather it looks like a continuous spectrum ranging the whole band of frequencies, the PSD of the noise error at frequency  $\Delta\omega$  is given by the downconversion of all components located at a distance  $\Delta\omega$  from **any** multiple of the oscillation frequency, as clarified from Figure 2.17

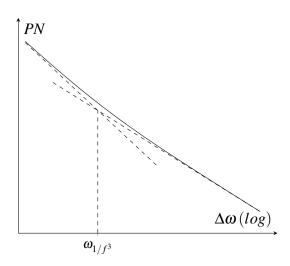

Moreover, if the PSD of the noise current is flat, the PSD of the phase error is proportional to  $\frac{1}{f^2}$  (considering the the PSD is somehow the square of the Fourier transform and the integral is equivalent to a division by  $j\omega$ ), while if the PSD of the noise is proportional to  $\frac{1}{f}$  (flicker noise), the PSD of the phase error directly depends on  $\frac{1}{f^3}$ .

Figure 2.17: Mechanism of conversion between the PSD of the noise into the PSD of the phase error (first two plots), the third plot represents the conversion of phase error into the output voltage, which will be explained later

To calculate the total noise PSD at a given offset frequency, it's necessary to find the total noise power. Considering that (2.37) gives the phase error for a given k, it's necessary to sum the power of (2.37), for all possible value of k. The power of a single value of k is given by (2.38), since the power of a sinewave is half the square of the amplitude.

$$|\Phi(\Delta\omega)|^2 = \frac{1}{8(C_T V_{LO})^2 (\Delta\omega)^2} c_k^2 (I_k^2)$$

(2.38)

Summing the power of all sinewaves obtained for different value of k and dividing by a small frequency range  $\Delta f$ , to get the PSD of the phase error  $S_{\phi}(\Delta \omega)$ , one gets:

$$S_{\phi}(\Delta\omega) = \frac{1}{8(C_T V_{LO})^2 (\Delta\omega)^2} \frac{4kT}{R_T/2} \sum_{k=0}^{+\infty} c_k^2 = \frac{kT/R_T}{(C_T V_{LO}^2)} 2\Gamma_{rms}^2$$

(2.39)

where the fact that  $I_k^2/\Delta f = \frac{4kT}{R_T/2}$ , for every k has been exploited in (2.39), together with the Parseval's theorem, to substitute the sum of all  $c_k$  with  $2\Gamma_{rms}^2$ .

Finally, to understand the effect of the noise on the output voltage rather than the phase error, it's necessary to consider the effect of the second block of Figure (2.14). In the frequency domain, the multiplication by a cosine function simply upshifts the spectrum of the phase error centering it near  $\omega_0$ . For this reason, (2.39) is the same when the PSD of the output voltage is considered instead of the one of the phase error, by simply remembering that, while  $\Delta \omega$  used to represent the frequency offset with respect to the zero frequency, it represents now the offset with respect to the carrier frequency, as Figure 2.17 explains. By substituting  $\Gamma_{rms}^2$  with the right value, in this case 1/2, the final phase noise equation, in logarithmic scale, known as *Leeson*

Equation is:

$$S_{\nu}(\Delta \omega) = 10 \log_{10} \left( \frac{kT/R_T}{(C_T V_{LO})^2 (\Delta \omega)^2} \right)$$

(2.40)

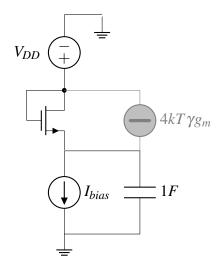

## 2.4.1 Effect of other noise sources

The above analysis considers only the effect of the noise generated by the tank. To consider also the effect of other noise sources, like the transistors of the cross-coupled pair or the bias generator, it's necessary to consider that the PSD of the noise current generated by the transitors vary along the period and it's not constant anymore. For istance, the PSD of the noise current generated by a transistor in the saturation region is:

$$S_{in} = 4kTg_m\gamma \tag{2.41}$$

where  $\gamma$  is a technological parameter which tends to be equal to 2/3 in case of long channel MOS and it's higher for short channel devices (it can reach values up to 2). To manage with this noise sources (called *cyclostationary noise sources*) a generalization of the ISF is introduced. For each of these noise sources, the *effective ISF* is defined as:

$$\Gamma_{eff}(\tau) = \Gamma(\tau) * \alpha(\tau) \tag{2.42}$$

where  $\Gamma(\tau)$  is the usual ISF of the tank, while  $\alpha(\tau)$  is a function that takes into account the fact that the noise current PSD is not constant entire the whole cycle and/or it has not the same maximum value of the tank's one. In case of the cross-coupled pair,  $\alpha(\tau) = g_m(\tau)\gamma/R_T$

With this remark, the analysis carried on previously is exactly the same, where  $\Gamma_{eff}$  must be used in place of  $\Gamma$ . For this reason, the final result differs from the one in (2.40) only by a proportionality constant, since  $\Gamma_{effrms}^2$  can be different from  $\Gamma_{rms}^2$ . This reasoning is valid for all noise sources, so the total noise PSD differs from the one of the tank only by a proportionality constant, the *noise factor F*. With this consideration, the Leeson equation becomes:

$$S_{\nu}(\Delta\omega) = 10log_{10}\left(\frac{(kT/R_T)F}{(C_TV_{LO})^2(\Delta\omega)^2}\right)$$

(2.43)

The exact calculation of the noise factor can be find in literature, it involves the calculation (if possible) of the rms value of  $\Gamma_{eff}$ , comparing it with the rms value of  $\Gamma$ , for every noise source. A typical value for a class-B oscillator is around 5. The exact calculation of the noise factor for the tail generator is somehow shown in the next chapter. Instead, for the noise generated by the cross-coupled pair, it's possible to show that it's proportional to the one generated by the tank via  $\gamma$ , with no dependence on all other parameters of the circuit. The proof of this requires long calculations that are extensively presented in [10]. For this reason, the noise factor's increment due to the cross-coupled pair is simply  $F_{cc} = \gamma$ .

### 2.4.2 Flicker Noise and effect of the common mode resonance

Up to now, only white noise sources have been considered. However, devices different from the tank also display flicker noise, whose PSD can be modelled altogether with:

$$S_{i_{flick}} = \frac{A}{\Delta \omega} \tag{2.44}$$

where A is a constant that takes into account all the parameters determining the flicker noise that are not frequency dependent. With the same approach used before, flicker noise causes PN in the same way explained in Figure 2.17. However, in this case the PSD is not constant. Using (2.44) instead of (2.41), it's possible to neglect all terms different from  $c_0$  in (2.39), obtaining, doing the next steps in the same way as before, the Leeson equation valid in presence of flicker noise only:

$$S_{v_{flick}}(\Delta \omega) = 10 log_{10} \left( \frac{Ac_0^2}{8(C_T V_{LO})^2 (\Delta \omega)^3} \right)$$

(2.45)

where the dependence on  $1/f^3$  is clear. For this reason Phase Noise's plot contains a -30dB/dec slope for low frequencies and the usual -20dB/dec slope for higher frequencies. Of course, the transition between the two parts is not abrupt an there exist a region where both noise contributions are relevant, as Figure 2.18 clarifes. For low frequencies only the flicker noise is relevant. For high frequencies only the thermal noise is significant. Taking the tangent of the plot representing the phase noise for a relatively low value of offset frequency and a relatively high value, the crossing point is somehow an indication on the transition between the two regions. This frequency is called  $1/f^3$  corner frequency and it can be find by equating (2.45) with (2.40), obtaining:

$$\omega_{1/f^3} = \frac{Ac_0^2}{4kT}R_T \tag{2.46}$$

The effect of the second harmonic resonance on flicker noise is outside the purpose of this thesis that mainly focuses on the thermal region. However, the improving effect of the common mode resonance on flicker noise is an extensively treated topic in literature [9].

Figure 2.18: Plot of the phase noise considering also flicker noise

## 2.4.3 The figure of Merit (FoM)

Leeson's equation shown in (2.40) can be expressed in several different ways. One of this involves the replacement of the value of the capacitor  $C_T$  with  $\frac{Q}{\omega_0 R_T}$ , where Q is the quality factor of the tank, which is usually dominated by the one of the inductor  $Q_L$ .

$$S_{\nu}(\Delta \boldsymbol{\omega}) = 10 \log_{10} \left( \frac{kT}{V_{LO}^2} \frac{R_T}{Q^2} \left( \frac{\omega_0}{\Delta \boldsymbol{\omega}} \right)^2 \right)$$

(2.47)

Looking at (2.47), it's clear that there's a square dependence of phase noise with respect to the ratio  $\omega_0/\Delta\omega$ . Moreover, the fact that the phase noise is inversely proportional to the square of the oscillation's amplitude means that it's also inversely proportional to the square of the bias current, namely that it's inversely proportional to the power consumption. For this reason, to compare different topologies of oscillator, working at possibly different frequencies, the *Figure of Merit* (FoM) is defined, normalizing the phase noise with respect to this two quantities [11].

$$FoM = S_{\nu}(\Delta\omega) - 20log_{10}\left(\frac{\omega_0}{\Delta\omega}\right) + 10log_{10}\left(\frac{P_{dc}}{1\,\text{mW}}\right) \, [dbC/Hz] \tag{2.48}$$

where  $P_{dc}$  is the DC power consumption of the oscillator.

## 2.5 Different oscillator topologies

To improve phase noise performances, a lot of different circuit topologies have been developed since 90s, trying to improve the phase noise with the same power consumption of the oscillator or the same chip area occupation. The main strategy used to achieve this goal is to increase the current and the voltage efficiency, to reach higher oscillation amplitudes which leads to better phase noise performances. In *Class-C* oscillators, cross-coupled pair devices are designed to operate always in saturation (using a proper bias circuit), and a big capacitor is added in parallel to the tail generator. In this way, the shape of the current is no longer the one reported in Figure 2.9, but it's composed by short pulses, with the current efficiency that is almost equal to 1,

giving an advantage in terms of phase noise. Another solution is the so-called *class-D*, where the tail generator is removed to let the oscillator work in the voltage limited regime. In this way, it's possible to reach higher amplitudes and there's no longer the noise contribution of the bias circuit (which, in a traditional class-B oscillator, can reach the 50 % of the total noise). A lot of other different topologies have been developed, the next chapter focuses on one possible solution to improve phase noise, which is the addition of the second harmonic resonance in the tank. As it'll be clear, there're some advantages that will be extensively discussed. The oscillator making use of the second harmonic resonance is called, in the literature, *class-F2* oscillator [12].

# Chapter 3

## The class F2 oscillator

## 3.1 The idea of introducing the second harmonic resonance

As seen in the previous chapter, the current's waveform differs from the theoretical square wave, displaying also even harmonics. Most of the time, the tank has a low impedance for all frequencies different form the resonance's one, giving rise to a sinusoidal oscillation at the drains. In reality, since the impedance of the tank is not zero for frequencies multiples of the oscillation's one, there are some higher order harmonics in the drain waveform, but they're usually negligible and the output waveform can be considered sinusoidal for all practical purposes. However, the presence of a non-zero second harmonic current must be useful to improve the performances of the oscillator, in a way that next subsections explains detailedly.

## 3.1.1 Class J waveform

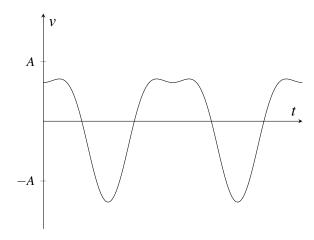

This concept is outside the environment of oscillators, but it's the starting point of the entire idea of the thesis. In literature, there exist a type of power amplifier, called *Class-J*, which makes use of a particular voltage waveform at the load, which is shown in Figure 3.1. In power amplifiers, the purpose of the "clipping" in the low side of the sinewave is to prevent the transistor entering the triode region. Similarly, one can think that having that waveform at the drain of the transistor of a traditional class-B oscillator could increase the maximum possible voltage amplitude since the tail generator enters triode region for higher voltages.

To proper understand this concept it's necessary to know the expression of the waveform of Figure 3.1, which is:

$$v = A\cos(\omega_0 t) + \frac{A}{2\sqrt{2}}\cos(2\omega_0 t)$$

(3.1)

where A is a generic value of the amplitude.

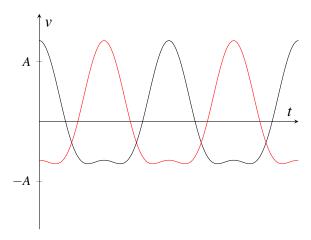

Figure 3.1: Class-J waveforms, black and red ones have the first harmonic phase shifted by  $\pi$

As clear from (3.1), the waveform of Figure 3.1 is composed by two **in phase** sinewaves, with proper amplitude. It's important to notice that, if a time shift by  $t_0$  is applied, waveform's expression becomes:

$$v = Acos(\omega_0(t - t_0)) + \frac{A}{\sqrt{2}}cos(2\omega_0(t - t_0)) = Acos(\omega_0t - \omega_0t_0) + \frac{A}{\sqrt{2}}cos(2\omega_0t - 2\omega_0t_0)$$

(3.2)

Hence, in general, the waveform in Figure 3.1 is represented by a sum of two sinewaves which must have zero phase shift or, if the first has a phase shift  $\theta$ , the second must have a phase shift equal to  $2\theta$ , to have the same waveform, only shifted in time. A particular case is when  $\theta = \pi$ , in this case the expression becomes (3.3), and it's represented in red colour in Figure 3.1.

$$v = A\cos(\omega_0 t + \pi) + \frac{A}{\sqrt{2}}\cos(2\omega_0 t + 2\pi) = -A\cos(\omega_0 t) + \frac{A}{\sqrt{2}}\cos(2\omega_0 t)$$

(3.3)

so if the first harmonic is inverted in sign, to keep the same waveform the second one **must not** be inverted in sign. This concept will be crucial in next explanations. Another important thing to notice is that the minimum value of the waveform in (3.2) is actually higher than the minimum value of a sinewave with amplitude A.

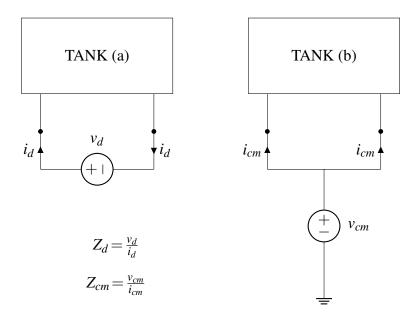

### 3.1.2 Common mode resonance

A way to exploit the fact previously shown is to introduce in the tank the *common mode* resonance. In fact, since the waveforms at the two drains are opposite in sign, they actually have the even harmonics in phase each other, while odd harmonics are in opposition of phase between the two drains. For this reason, the tank may have also a common mode resonance, which can have a frequency different from the *differential mode* one. The usual differential mode impedance is defined as the impedance seen connecting a test generator like the Figure 3.2(a), while the common mode impedance is defined as the one seen with the configuration of Figure 3.2(b). Since the second harmonic is a common mode signal, the voltage at the drain of a device is.

$$v_d = -R_T I_1 cos(\omega_0 t) - R_{T2} I_2 cos(2\omega_0 t)$$

(3.4)

where  $R_T$  is the usual tank's resistance as defined up to now (differential mode), while  $R_{T2}$  is the resistance of the tank at common mode at  $2\omega_0$ , supposing to have a resonance at twice the oscillation frequency **for common mode signals**. It's important to notice that, in general,  $I_1$  and  $I_2$  can have a non-zero phase. By next expressing them as magnitude and phase, the voltage waveform at one of the drains becomes:

$$v_d = -R_T |I_1| cos(\omega_0 t + \phi_1) - R_{T2} |I_2| cos(2\omega_0 t + \phi_2)$$

(3.5)

where  $\phi_1$  and  $\phi_2$  are the phase of  $I_1$  and  $I_2$ , respectively.

Figure 3.2: Definition of differential (a) and common mode (b) impedances

If  $\phi_2 = 2\phi_1 + 180^\circ$  the drains' waveform will be equal to the one of Figure 3.1. This is an advantage since the minimum value of the drain voltage is higher than a traditional class-B oscillator and, considering that the voltage drop across cross-coupled pair's devices is the same, it means that the tail generator works with an higher  $V_{ds}$ , delivering more current or, countersome, it's possible to have a tail generator with reduced area with the same current delivered by it<sup>1</sup>. However, to have the correct waveform at drains, it's necessary that  $\phi_2 = 2\phi_1 + 180^\circ$ . If, arbitrarily,  $\phi_1 = 0$ , to have (3.5) equal to (3.3), it's necessary to have  $\phi_2 = 180^\circ$ , which means that the second harmonic of the current must be in opposition of phase with the first. If the two are in phase, this technique is not applicable anymore.

To understand why, instead, this tecnicque can be used in traditional class-B oscillators, it's necessary to analyze the drain current's spectrum, in particular the phase of the second harmonic with respect to the first. Considering the example of the previous chapter, it's possible

<sup>&</sup>lt;sup>1</sup>Drain-to-source saturation voltage is proportional to the square root of the form factor W/L of the transistor, according to short channel model [13]

to (numerically) calculate the first two Fourier coefficient  $I_1$  and  $I_2$  of the waveform of Figure 2.9, obtaining:

$$\begin{cases} \frac{I_1}{I_2} = 0^{\circ} \\ \frac{I_2}{I_2} = 180^{\circ} \end{cases}$$

(3.6)

The first remarkable point is that the theoretical analysis behind the calculation of (3.6) assumes the capacitance connected to the common source to be a short circuit at  $\omega_0$ . If it's not true, the phase of the second harmonic with respect to the first changes. To retrieve a situation with the right phase shift between  $I_1$  and  $I_2$ , adding an extra capacitance, in the order of fF at the source may be necessary. Figure 3.3 show the phase shift between  $I_1$  and  $I_2$  in Example 2.3.1, with respect to the value of an external tail capacitance. It's clear that, after a certain value, what is theoretically claimed by (3.6) is practically true, noticing that "class-J" waveforms are obviously achieved (with some minor differences) even if the phase shift is not exactly  $180^{\circ}$ , but still a value closer to it. However, in this particular Example, bias current is set to 1.2mA, since the tank's resistance is fixed to  $1k\Omega$ . In practical oscillators, the equivalent parallel resistance of the tank is few hundreds of  $\Omega$ , giving the need of higher bias current. This implies that the transistor creating the current source must be bigger and therefore its parasitic capacitance is already enough to guarantee (3.6) with no external capacitance. This is the reason why, in practical applications shown in the next chapter or in literature [12], this aspect is never considered.

Figure 3.3: Relative phase between  $I_1$  and  $I_2$  with respect to the external capacitance. After  $C_{tail} = 22 \, fF$ , equation (3.6) is practically true

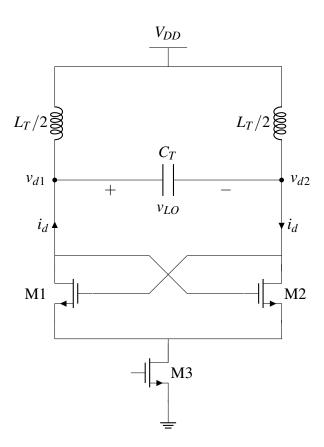

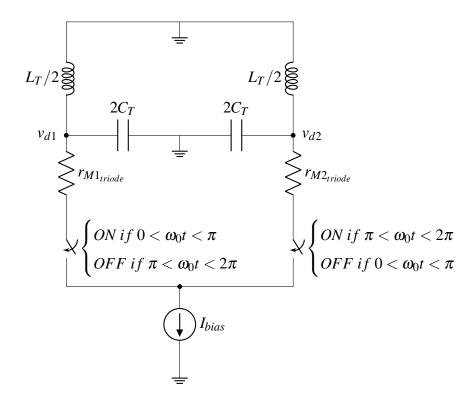

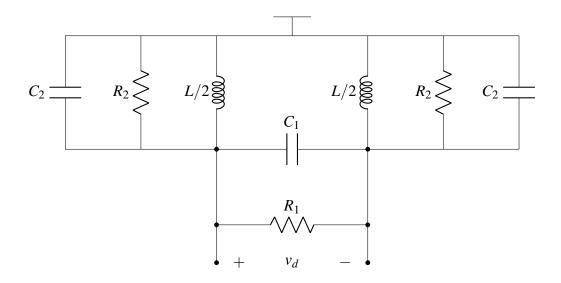

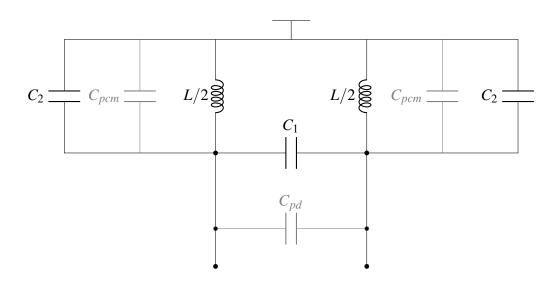

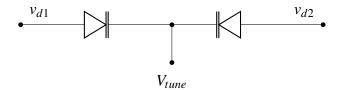

Once the condition in (3.6) is verified, it's possible to exploit the presence of the second harmonic by modifying the tank adding the second harmonic resonance, as Figure 3.4 shows.

Figure 3.4: Tank used to exploit the second harmonic resonance

With a reasoning similar to the one shown before, the resonance frequency for differential signals is:

$$\omega_{dm} = \frac{1}{\sqrt{L(C_1 + C_2/2)}} \tag{3.7}$$

At  $\omega_0$ , the impedance of the tank is  $R_1//(2R_2)$ .

From the common mode, instead, it's like  $C_1$  and  $R_1$  were not present. Hence, the circuit is composed by two identical halves that display a resonance at

$$\omega_{cm} = \frac{1}{\sqrt{\frac{C_2 L}{2}}} \tag{3.8}$$

at which the impedance of every half is  $R_2$ , that, multiplied by  $I_2$ , gives the second harmonic voltage. A class-B oscillator modified using this tank, or an equivalent one, is named in the literature class-F2. It gives several advantages in term of phase noise that will be discussed in next sections. It's important to notice that whatever follows is already present in literature but there's no "summary" work that show if, or if not, is possible to sum up all this advantages together.

## 3.2 Class F2 Waveform

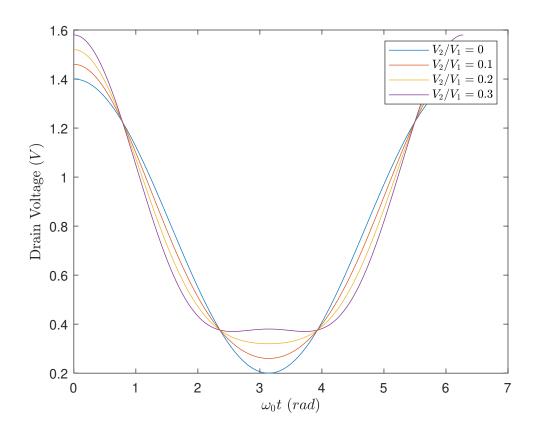

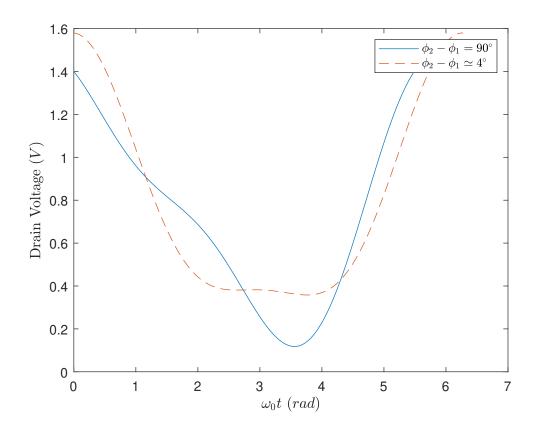

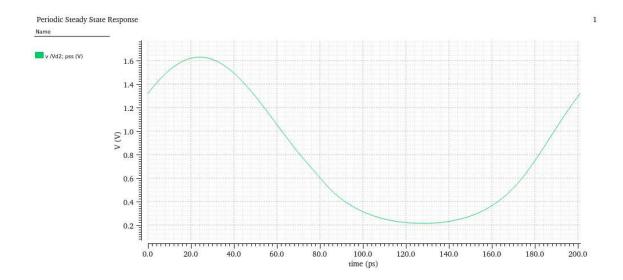

In a class-F2 oscillator, waveform at the drain is no longer sinusoidal. In fact, the presence of the second harmonic resonance gives rise to a voltage at twice the oscillation frequency, which sums with the usual sinusoidal oscillation. For this reason, the drain voltage waveform looks like Figure 3.1. Of course, it depends on the relative amplitude between the first and the second harmonics. Figure 3.5 shows 3 examples of waveform where the amplitude of the second harmonic is changed among different values, keeping the phase shift at the right value, as explained before. Figure 3.6, instead, shows what happens when the phase of the second

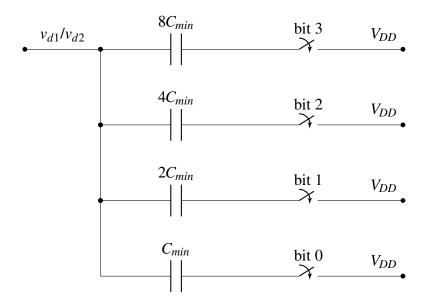

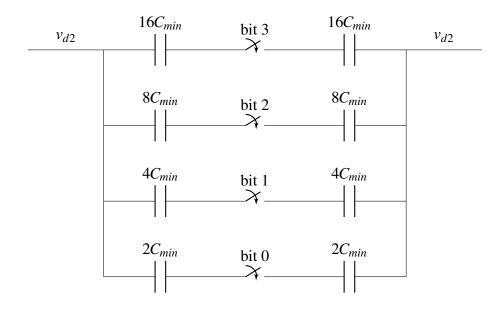

harmonic has not the right value. As it's clear, there's no advantage in this case. Moreover, Figure 3.5 shows that the minimum value of the drain voltage is higher than the case of the simple class-B. This implies that, with the same first harmonic amplitude, namely the same differential output voltage, the drain voltage reaches an higher value. This further implies that the minimum voltage at the common source is higher than the class-B oscillator, with the same output amplitude, namely with the same phase noise. Hence, it's possible to increase the bias current entering the voltage limited regime for higher currents, meaning that it's possible to decrease the phase noise by increasing the oscillation amplitude without changing the size of the tail's transistor. On the contrary, it's possible to keep the bias current at the same value, in this case the form factor of the tail's device can be smaller. This further enables to have a less noisy bias' transistor, or simply a smaller one if the chip area is particularly relevant. Depending on the design's constraints, designers can choose between different views of the same concept.

Figure 3.5: Difference in the waveform changing the ratio between the first and the second harmonic. In this case  $V_{DD} = 0.8V$  and  $V_1 = 600 \, mV$

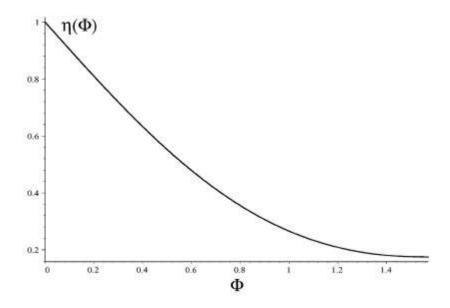

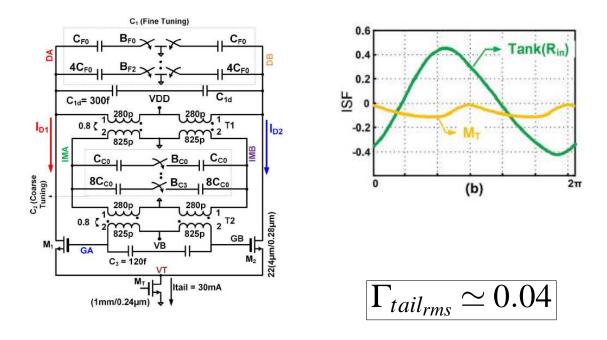

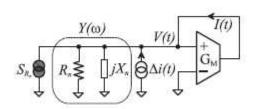

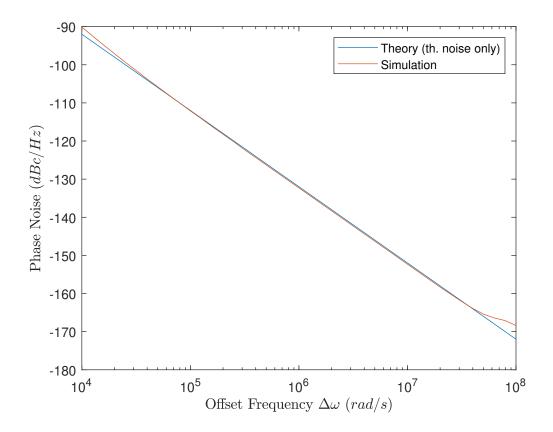

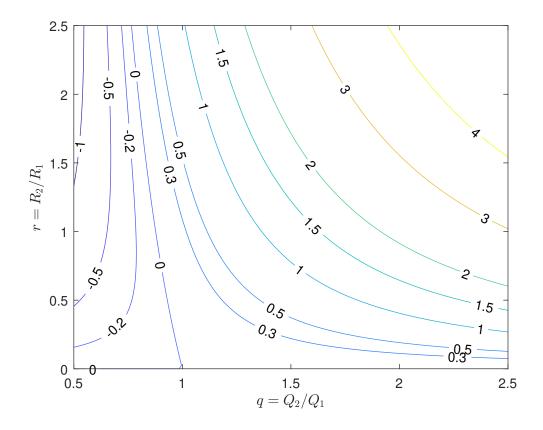

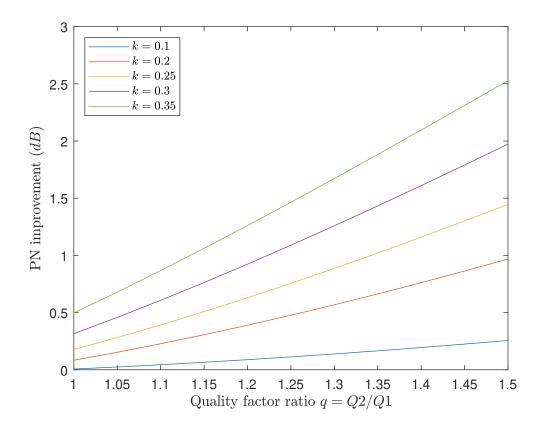

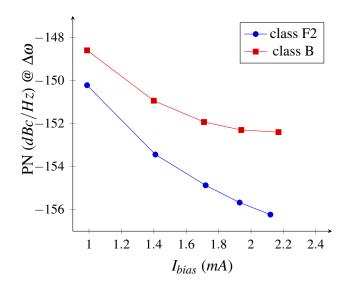

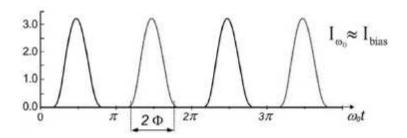

Figure 3.6: Effects of a phase shift between the harmonics different from 180°. Dahsed line, instead, represent the effect of a small error in the phase shift, which causes no significant difference from the ideal case