ROBERTO SARTORI

## Design, analysis and optimization of a dynamically reconfigurable regenerative comparator for ultra-low power 6-bit TC-ADCs in 90nm CMOS technology

# Design, analysis and optimization of a dynamically reconfigurable regenerative comparator for ultra-low power 6-bit TC-ADCs in 90nm CMOS technology

ROBERTO SARTORI

Supervisor Prof.ssa Maria Elena Valcher Assistant Supervisor Dr.D. Juan A. Montiel-Nelson

October 2013

Roberto Sartori: *Design, analysis and optimization of a dynamically reconfigurable regenerative comparator for ultra-low power 6-bit TC-ADCs in 90nm CMOS technology, ,* © October 2013

Università degli Studi di Padova

Escuela de Ingeniería de Telecomunicación y Electrónica Facultad de Ingeniería Universidad de Las Palmas de Gran Canaria Dipartimento di Ingegneria dell'Informazione Facoltà di Ingegneria Università degli Studi di Padova

"While the pessimists complain about the wind, and the optimists expect the wind to change, we adjust the sails." — William Arthur Ward

To my family.

Analog-to-Digital Converters (ADCs) have always been a topic of intense research in electronics since the advances in digital processing and storage technologies enabled for the pre-processing, postprocessing and storage of analog signals as large streams of digital values. Mixed signal integrated circuits, including data acquisition and conversion, experienced a real revolution in terms of the number of emerging applications in electronics and telecommunications.

Powerful processors appeared for mixed signal processing, allowing for longer word-length, higher operation frequencies and larger memory sizes. Research efforts were initially focused on increasing the sampling rate and the resolution of the analog-to-digital and digital-to-analog converters to meet real-time multimedia processing requirements. Several acquisition methodologies and architectures were presented to support a wide range of applications oriented to processing huge volumes of data [1].

However, nowadays there is a high number of emerging applications where it is still necessary to collect and process analog data, but they are subject to strong energy consumption restrictions. Mobile phones containing gyroscopes and accelerometers among other sensor assisted Global Positioning System (GPS) navigation applications, sensor networks supported by small batteries, or medical aids using remote sensing battery-less are typical ultra-low power applications requiring Analog-to-Digital Converter (ADC) subsystems. The conversion rate and resolution specifications are less restrictive than the power consumption restrictions in these applications. Typically, ultra-low power requirements must be met, but just some few samples or kilo-samples per second are needed for 4-8 bit resolutions. Therefore, among all ADC architectures in literature, the Successive Approximation Register (SAR) and  $\Sigma\Delta$  converters are the more suitable architectures [2] for this purpose.

It is well known that SAR architectures are preferable in terms of area and power consumption in comparison with the other topologies [3] at medium and low conversion rates. Furthermore, due to the fact that high performance technologies are mainly focused on reducing the delay while maintaining low power consumption in the digital circuitry, the use of recent technologies in ADC design is more effective as greater is the digital section in comparison with its analog one [4]. In this sense, several approaches have been presented to optimize the digital controller reducing the power and increasing the conversion speed on SAR ADC architectures by using comparator-based binary search [5, 6] and asynchronous controllers [7, 8, 9]. In a Comparator-

based Asynchronous Binary Search (CABS), the need for digital-toanalog conversion and digital controllers is completely removed by using a binary tree of comparators with built-in thresholds which are triggered to run the successive approximation algorithm [5]. But the circuit complexity of this approach follows the same exponential growth than flash ADCs.

Recently, a novel ADC architecture named Threshold-Configuring ADC (TC-ADC) was introduced [10]. TC-ADC is based on a single comparator and a programable array of transistors that allow to implement the ADC and Digital-to-Analog Converter (DAC) functionalities [11]. The TC-ADC authors demonstrate the usefulness of this new architecture when low power consumption is required at medium/low conversion rates.

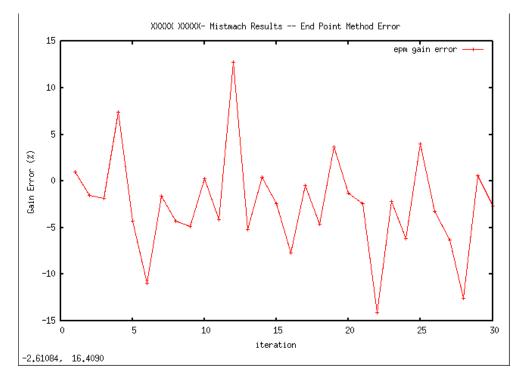

In this work the threshold configurable regenerative comparator on which TC-ADCs are based is optimized to further reduce the power consumption for use in battery-less biomedical sensor applications. Moreover, the effect of device mismatches on the offset, gain and linearity errors of the ADC is analyzed by means of Monte Carlo simulations. This optimized comparator reduces the power consumption from  $13\mu W$  to  $3\mu W$  in the more power hungry section of the TC-ADC (65% of the overall TC-ADC power is dissipated in the regenerative comparator), while maintaining the same full scale range. The optimized comparator achieves also better performance (about 50% improvement) in terms of offset, gain and non-linearity errors when matched devices are given. In the presence of device mismatch just the gain error shows a significative improvement, although nonlinearity error analysis indicates higher simmetry and predictability which can be further exploited to reduce the complexity of nonlinearity cancellation circuits required for higher resolution applications.

## RESUMEN

En este trabajo se optimiza el comparador regenerativo configurable de umbral en lo que el Threshold-Configuring SAR-ADC se basa para reducir aún más el consumo de energía, en aplicaciones de sensores biomédicos sin batería [1]. Por otra parte, el efecto de la dispersión de proceso de los dispositivos en características del conversor como el offset, la ganancia y los errores de linealidad del ADC se han de analizar de forma cualitativa y cuantitativa por medio de simulaciones de Monte Carlo. Resultados previos muestran que estos comparadores

optimizados permiten reducir el consumo de energía de  $13\mu W$  hasta  $3\mu W$  manteniendo constante el mismo fondo de escala.

En presencia de la dispersión de proceso "device mismatch", los mismos resultados previos muestran que sólo el error de ganancia muestra una mejora significativa, aunque el análisis de error de no linealidad indica una mayor simetría y la previsibilidad. Estas dos características pueden aprovecharse más para reducir la complejidad de los circuitos de cancelación de no linealidad requerida para aquellas aplicaciones de mayor resolución [12].

Por todo lo anterior, es objetivo de este trabajo obtener las relaciones cualitativas y cuantitativas entre dimensiones de dispositivos, potencia consumida, fondo de escala, errores de linealidad, offset y ganancia del conversor ADC basado en un comparador de umbral reconfigurable y regenerativo como el referenciado en [13]. Estas relaciones permiten dimensionar el comparador para una aplicacion de ultra bajo consumo de potencia. El proceso tecnologico es de UMC, Complementary Metal-Oxide-Semiconductor (CMOS) 90nm "Standard Process 1.0V CMOS 1P9M".

## COMPENDIO

Il presente studio mira ad ottimizzare il comparatore di soglia di tensione regenerativo riconfigurabile su cui si basa il Threshold-Configuring SAR ADC, al fine di ridurre ulteriormente il consumo di energia in applicazioni quali sensori biomedici senza batteria. Vengono inoltre analizzati in forma qualitativa e quantitativa gli effetti della dispersione di processo dei dispositivi che costituiscono il convertitore, l'offset, il guadagno e gli errori di linearità del ADC, attraverso simulazioni Monte Carlo. Risultati precedenti mostrano come questi comparatori ottimizzati permettano di ridurre il consumo di energia da  $13\mu W$  a  $3\mu W$  mantenendo costante il fondo scala.

L'obiettivo finale è dunque quello di ottenere le relazioni qualitative e quantitative tra le dimensioni dei dispositivi, la potenza dissipata, il fondo di scala, gli errori di linearità, l'offset e il guadagno del ADC basato sul comparatore di soglia di tensione riconfigurabile e rigenerativo presentato in [13]. Tali relazioni permettono di dimensionare il comparatore per applicazioni ad ultra basso consumo di potenza. Il processo tecnologico con cui vengono sviluppate le simulazioni è UMC, CMOS 90nm "Standard Process 1.0V CMOS 1P9M".

## CONTENTS

| Abstract        |      |                                                                |

|-----------------|------|----------------------------------------------------------------|

| List of Figures |      |                                                                |

| List of Tables  |      |                                                                |

| Listings        |      |                                                                |

|                 | 0    |                                                                |

| Ι               | ULTI | RA-LOW POWER ADC ARCHITECTURES 1                               |

| 1               | INT  | RODUCTION                                                      |

|                 | 1.1  | Basic A/D converter function                                   |

|                 |      | 1.1.1 Conversion systems                                       |

|                 | 1.2  | Specifications of converters 4                                 |

|                 |      | 1.2.1         Absolute accuracy         5                      |

|                 |      | 1.2.2         Relative accuracy         5                      |

|                 |      | 1.2.3 Differential nonlinearity 6                              |

|                 |      | 1.2.4 Offset                                                   |

|                 |      | 1.2.5 Signal-to-Noise Ratio                                    |

|                 |      | 1.2.6 Effective Number of Bits                                 |

|                 |      | 1.2.7 Figure of Merit                                          |

| 2               | A/D  | O CONVERTERS 9                                                 |

|                 | 2.1  | Low-power ADC architectures 13                                 |

|                 |      | 2.1.1 Nyquist-rate ADCs                                        |

|                 |      | 2.1.2 Oversampled ADCs                                         |

|                 | 2.2  | Successive Approximation Register ADCs 19                      |

|                 |      | 2.2.1 Low-power SAR ADCs                                       |

|                 | 2.3  | Comparator-Based Binary Search ADCs 22                         |

|                 |      | 2.3.1 SAR ADCs using CC                                        |

|                 | 2.4  | Threshold-Configuring ADCs 25                                  |

|                 |      | 2.4.1 TC-ADC Principle of Operation 25                         |

|                 |      | 2.4.2 Architectural Details                                    |

|                 |      | 2.4.3 Circuit Implementation                                   |

|                 |      |                                                                |

| Π               | AN   | ULTRA-LOW POWER COMPARATOR 31                                  |

| 3               | THR  | ESHOLD-CONFIGURABLE COMPARATOR 33                              |

|                 | 3.1  | Basic Operation                                                |

|                 | 3.2  | Threshold Generation 35                                        |

|                 | 3.3  | Design Methodology                                             |

| 4               | DES  | IGN SPECIFICATION REQUIREMENTS 39                              |

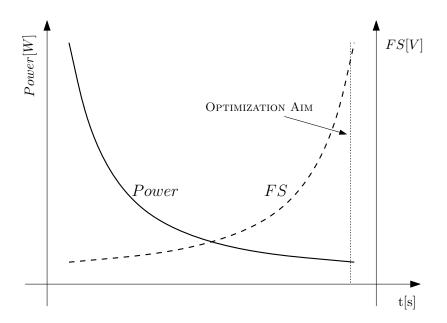

|                 | 4.1  | TC-Comparator <i>power consumption</i> vs <i>full scale</i> 39 |

|                 |      | 4.1.1 Results                                                  |

|                 | 4.2  | RFID Reader <i>radiated power</i> vs <i>distance</i>           |

|                 |      |                                                                |

| III             |      | $\mathbf{XING} \mathbf{AND} \mathbf{OPTIMIZATION}  47$         |

| 5               | SIM  | ULATION ENVIRONMENT SET-UP                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.1             | HSPICE Environment Structure                                                                                           |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 | 5.1.1 Files Hierarchy                                                                                                  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.2             | Simulation Setup                                                                                                       |  |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SIZI            | TNG FOR ULTRA-LOW POWER AND FS OPERATION 55                                                                            |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.1             | Characteristics of CMOS Devices                                                                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 | 6.1.1 Threshold voltage                                                                                                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 | 6.1.2 Maximum drain-source Currents 56                                                                                 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 | 6.1.3 Parasitic Capacitance and on-state Resistance 56                                                                 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 | 6.1.4 Transconductance and gain-bandwidth 57                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.2             | UMC CMOS 90nm Process Characteristics 57                                                                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 | 6.2.1 Electrical parameters                                                                                            |  |

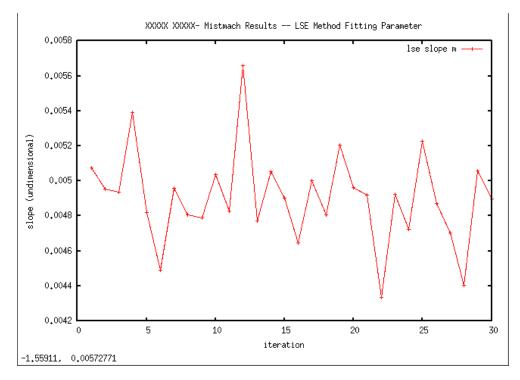

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 | 6.2.2 Model fitting accuracy                                                                                           |  |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ОРТ             | IMIZATION FOR LINEARITY IMPROVEMENT $63$                                                                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7.1             | Analysis Methodology 63                                                                                                |  |

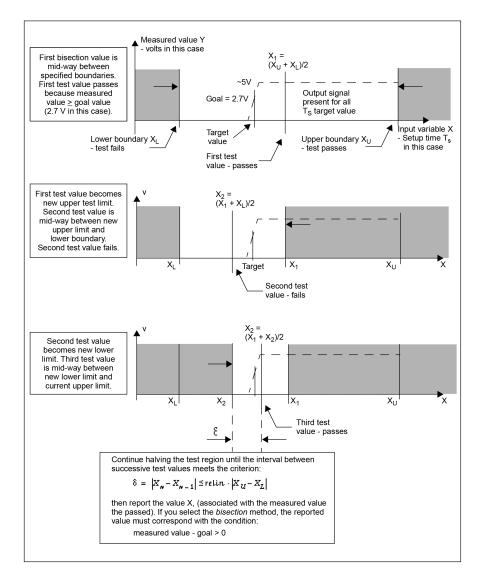

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 | 7.1.1 Optimization analysis by Bisection method 65                                                                     |  |

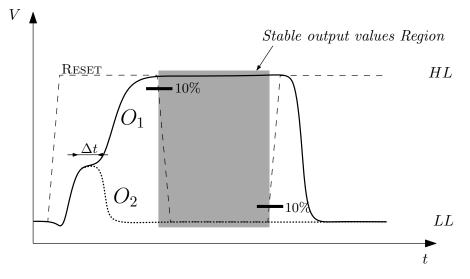

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7.2             | Design restrictions Achievement                                                                                        |  |

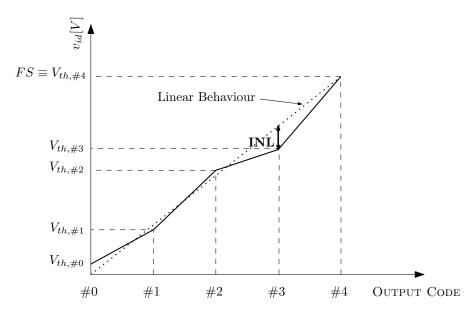

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7.3             | NonLinearity Analysis: DNL and INL errors 67                                                                           |  |

| 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MIS             | MATCH ANALYSIS                                                                                                         |  |

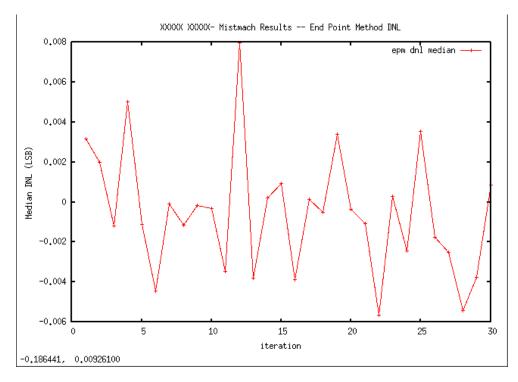

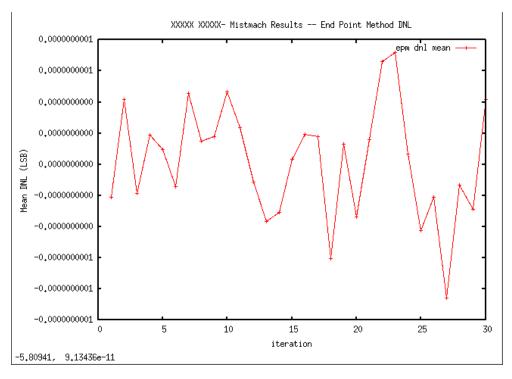

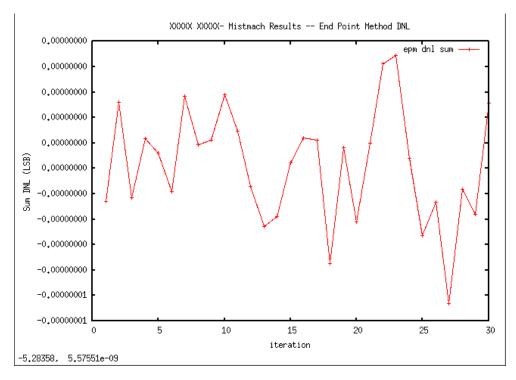

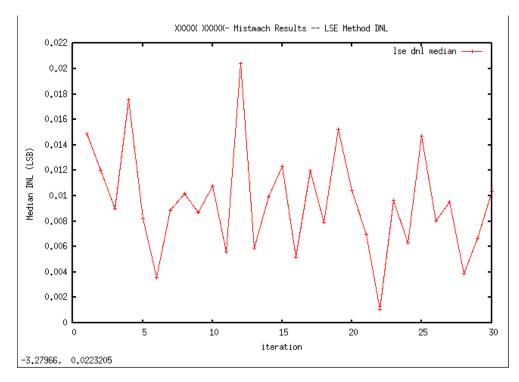

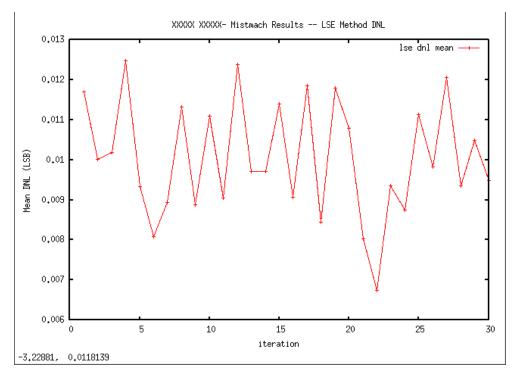

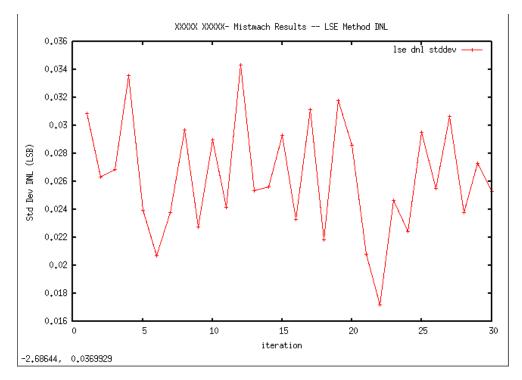

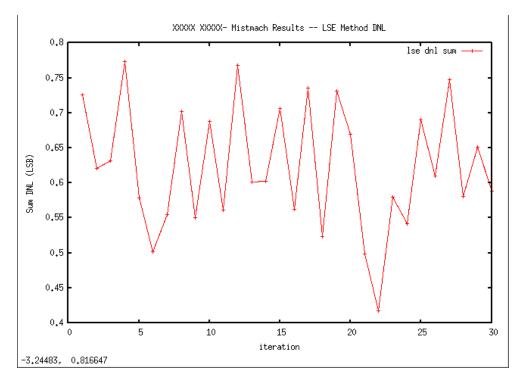

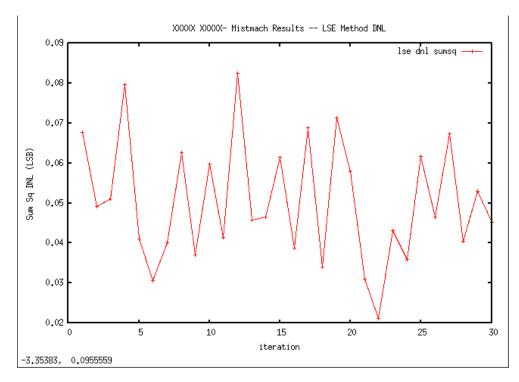

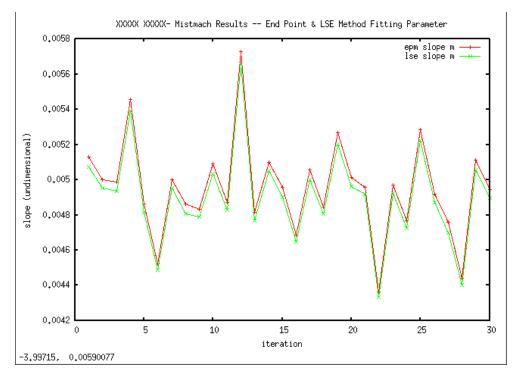

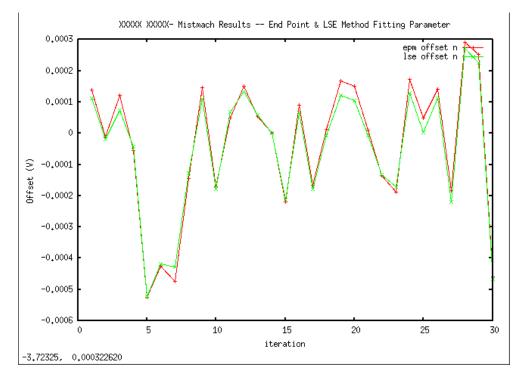

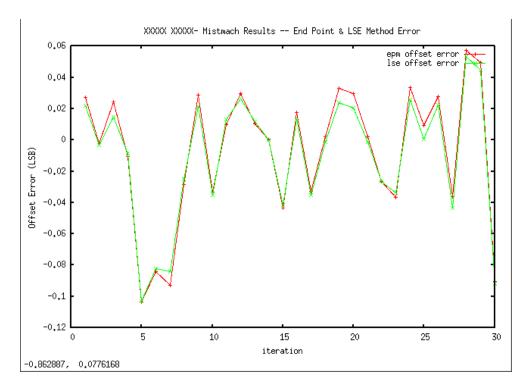

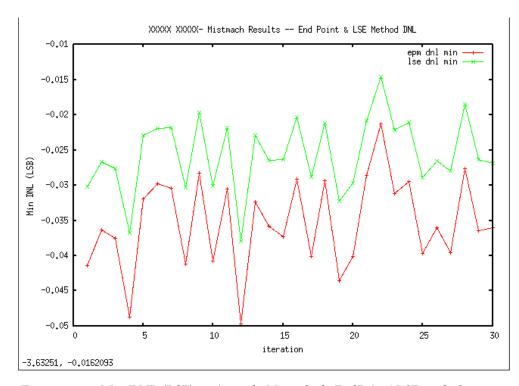

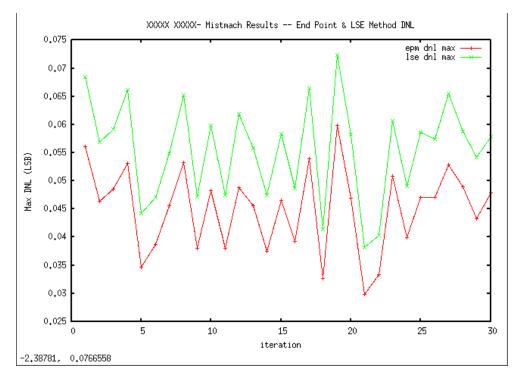

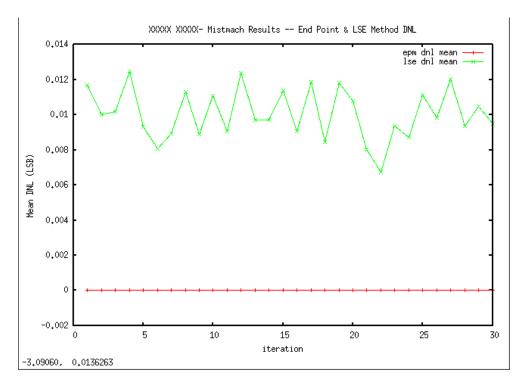

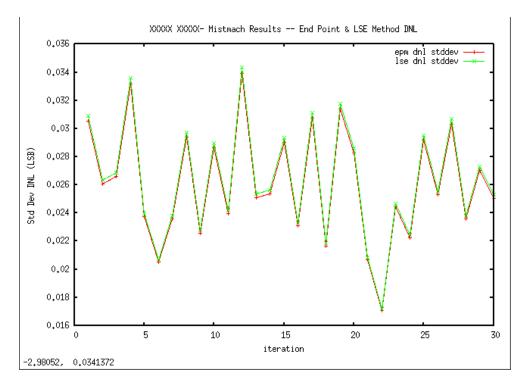

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8.1             | Mismatch optimization through DNL analysis 69                                                                          |  |

| 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RES             | ULTS                                                                                                                   |  |

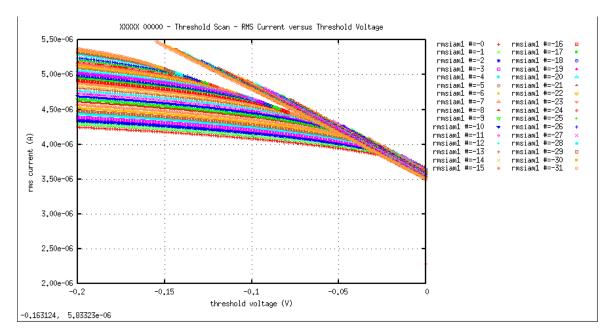

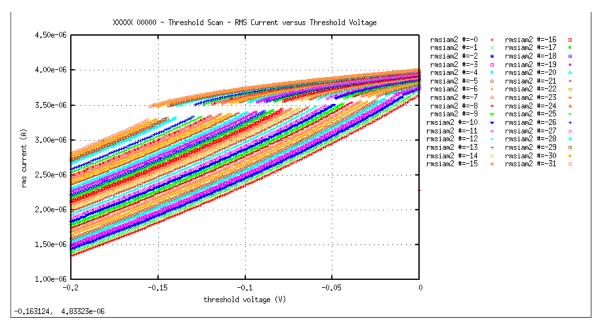

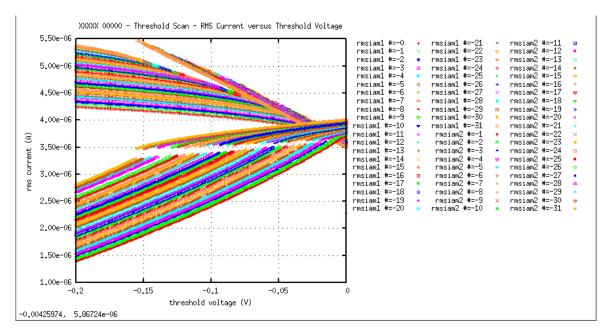

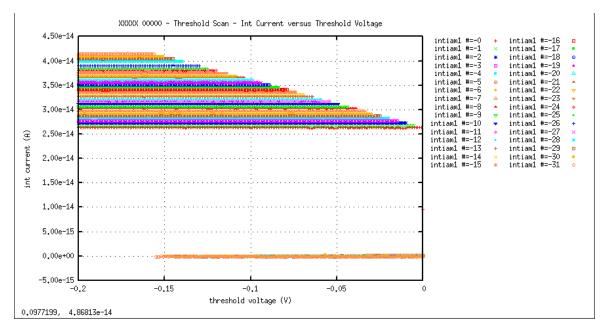

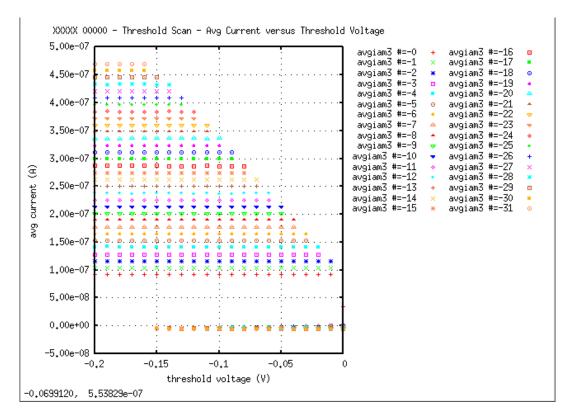

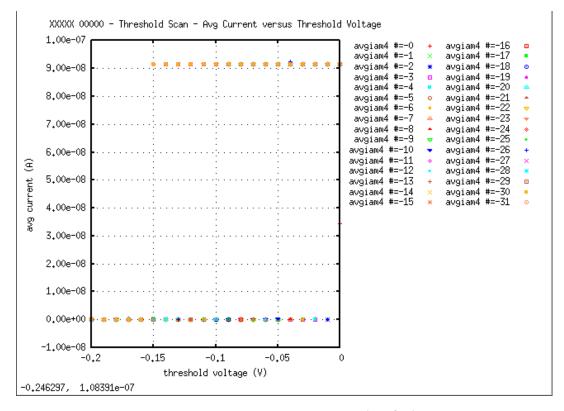

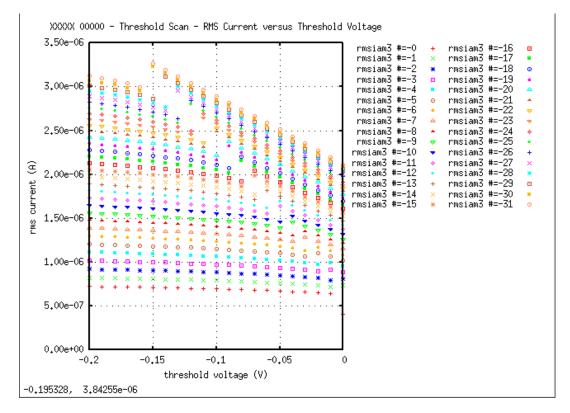

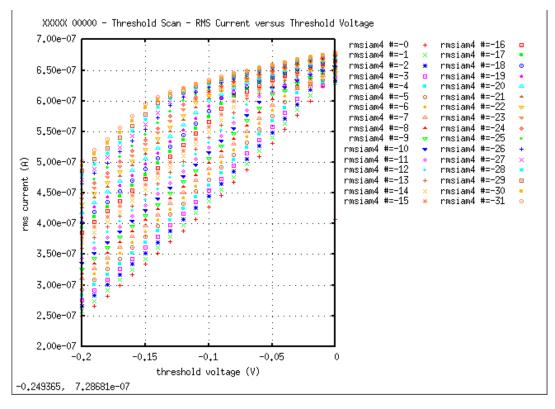

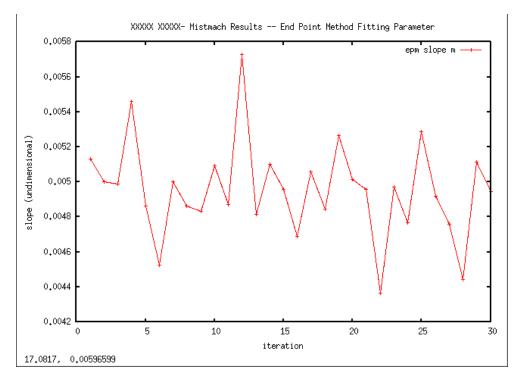

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9.1             | Optimization Results – <i>scanning</i> method 77                                                                       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9.2             | Reference Values – <i>scanning</i> method 92                                                                           |  |

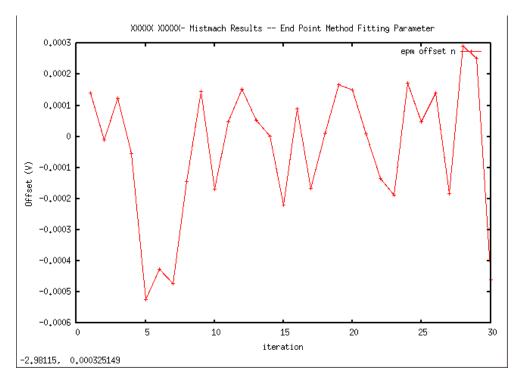

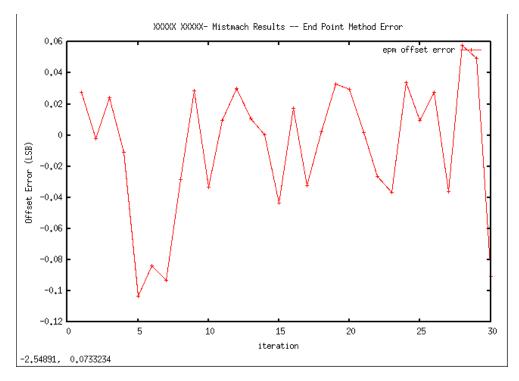

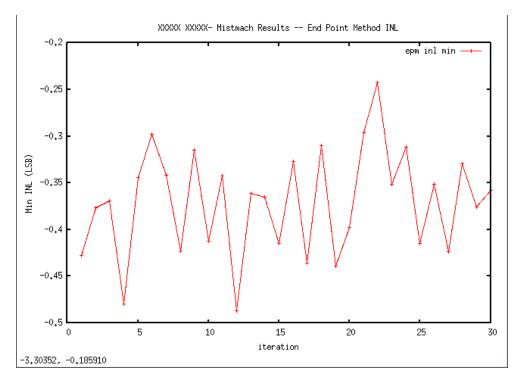

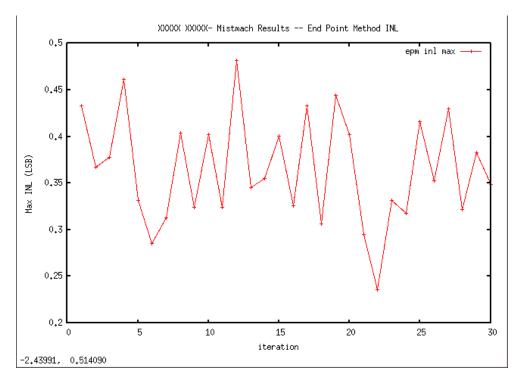

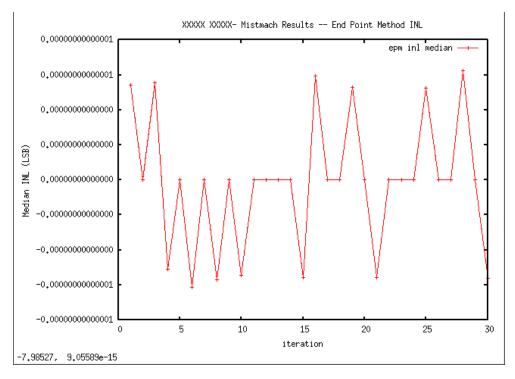

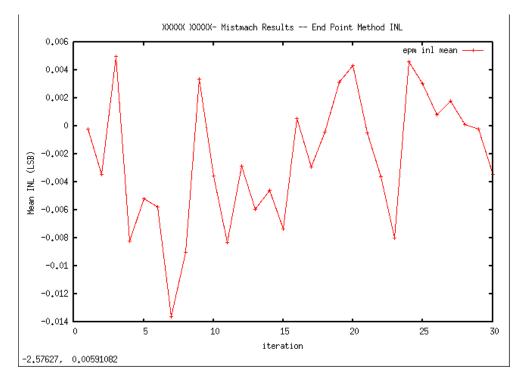

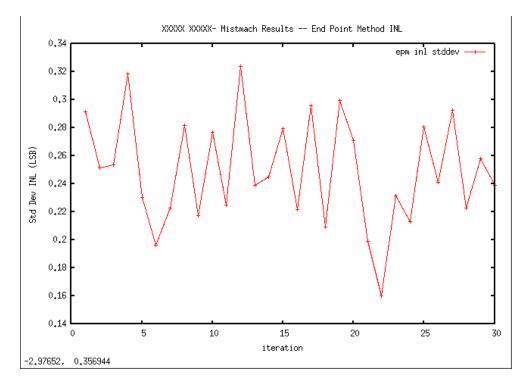

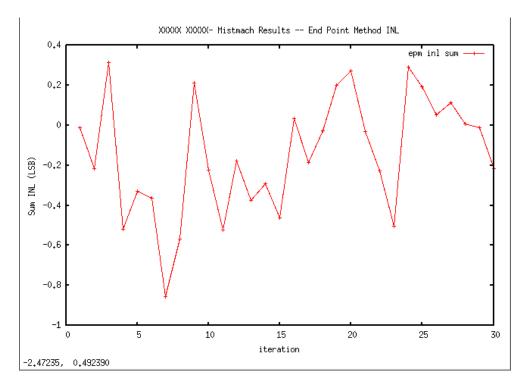

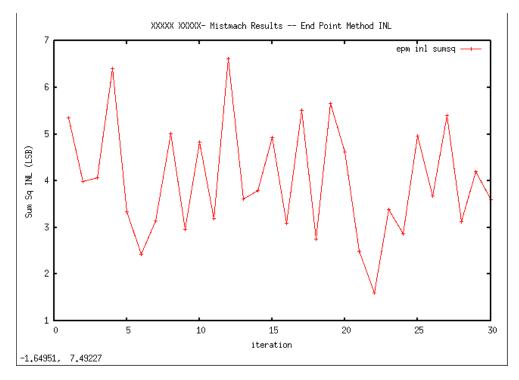

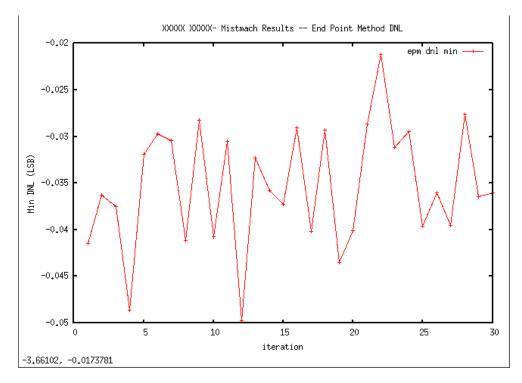

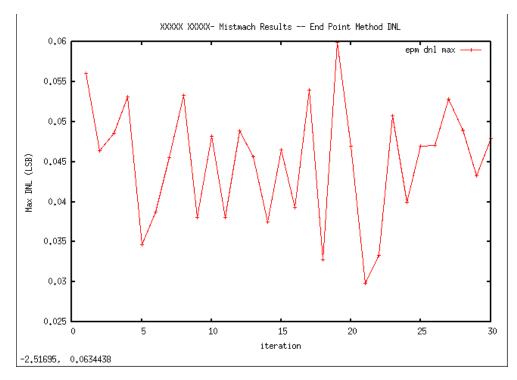

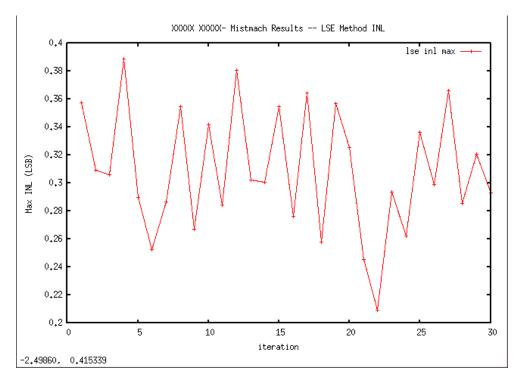

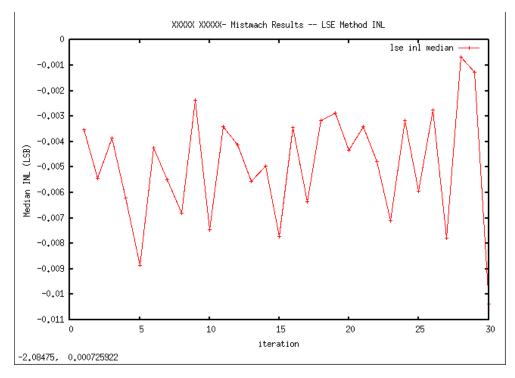

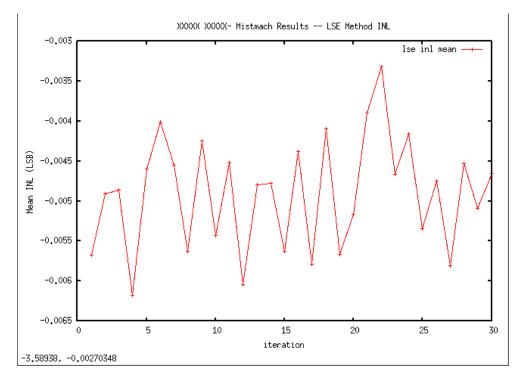

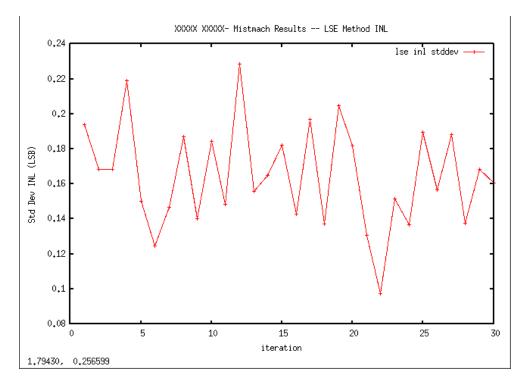

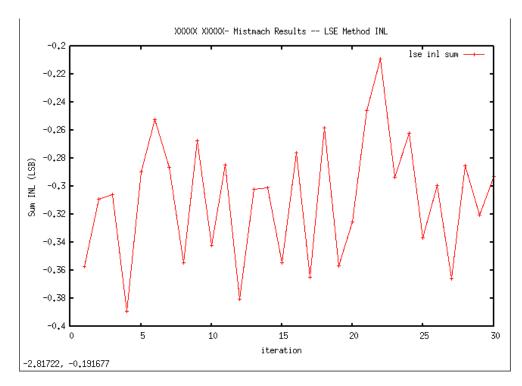

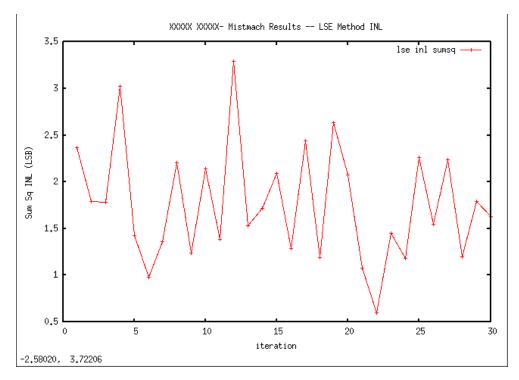

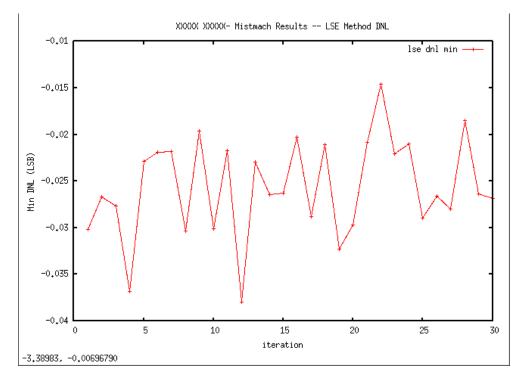

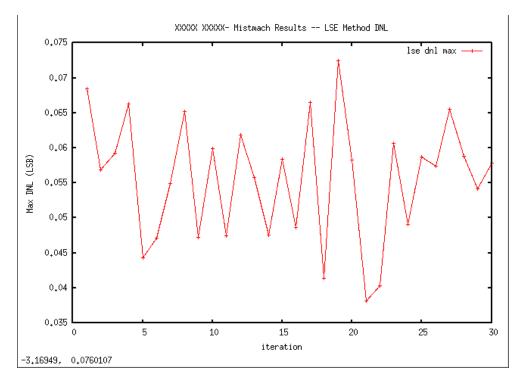

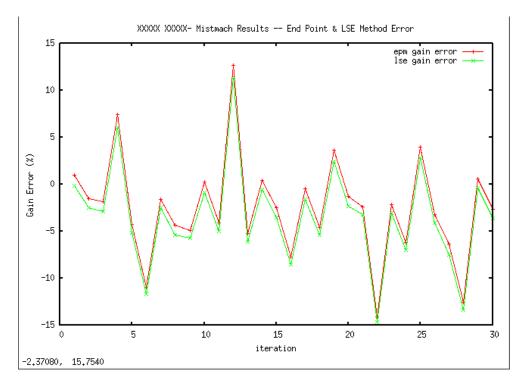

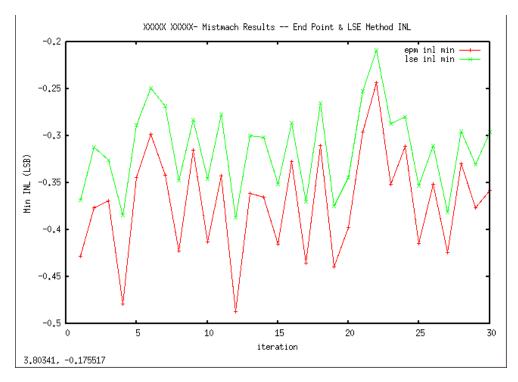

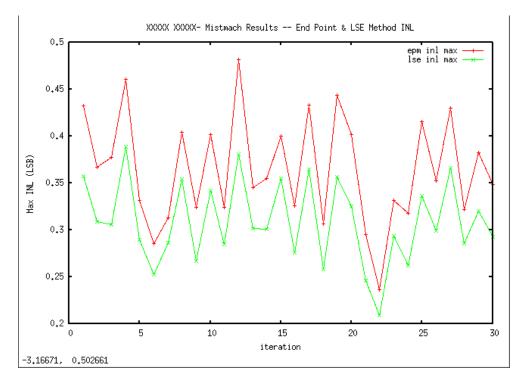

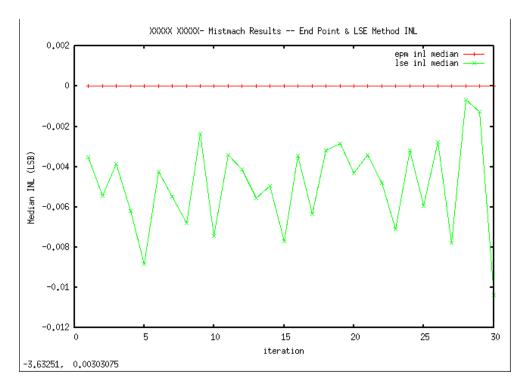

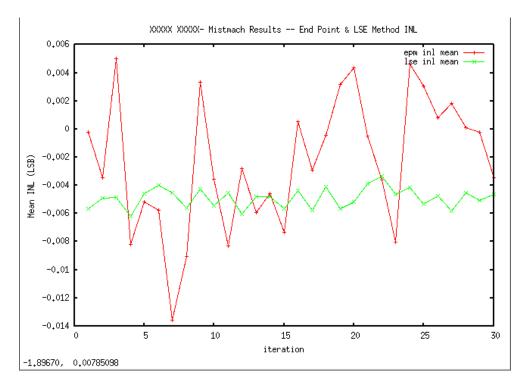

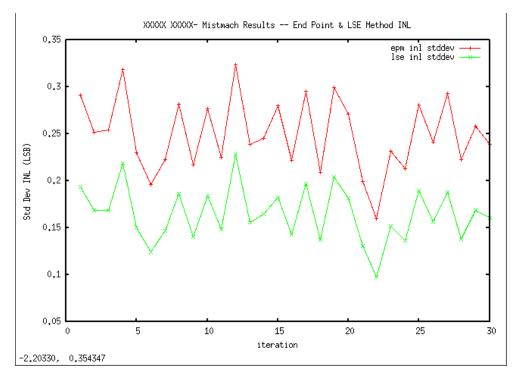

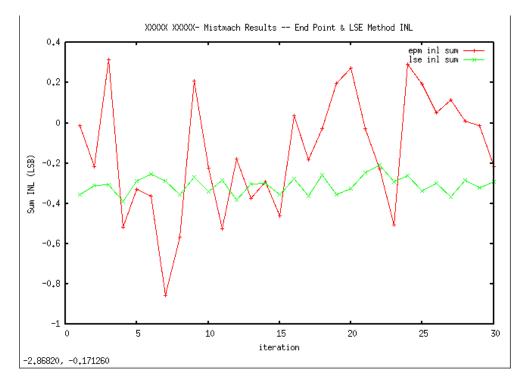

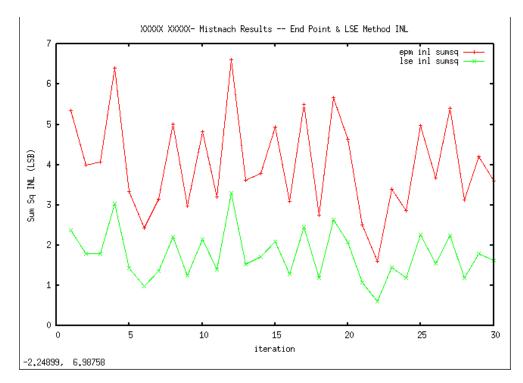

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9.3             | Mismatch Results – <i>Monte Carlo</i> simulation 108                                                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9.4             | Conclusions                                                                                                            |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                                                                                                                        |  |

| IV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 | APPENDIX 13;                                                                                                           |  |

| Α                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 | ENDIX                                                                                                                  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A.1             | The SAR Algorithm                                                                                                      |  |

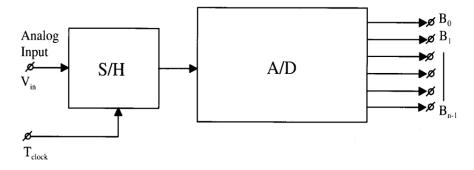

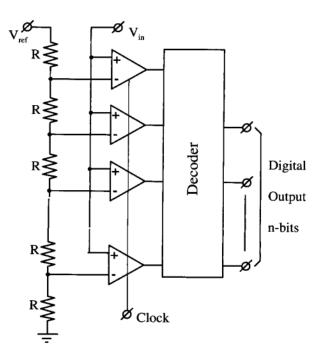

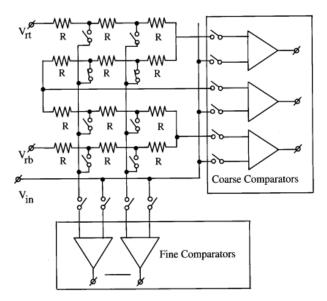

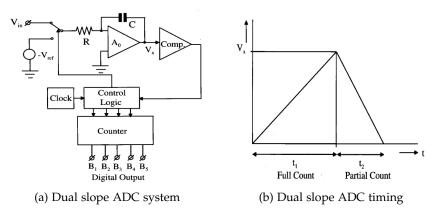

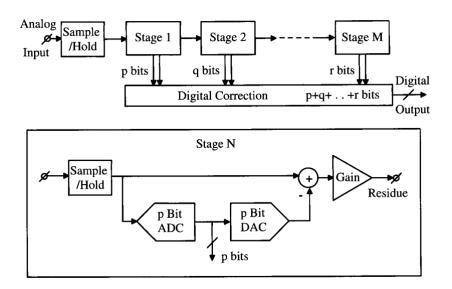

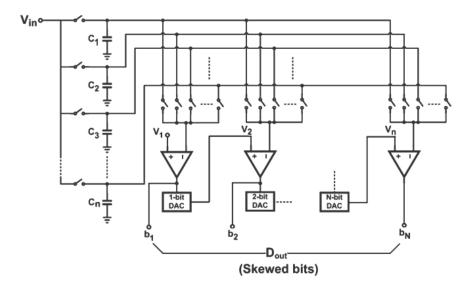

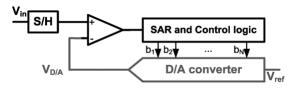

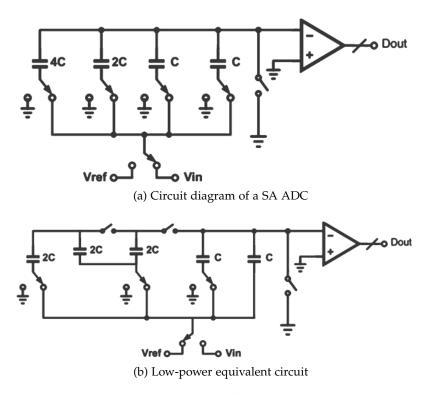

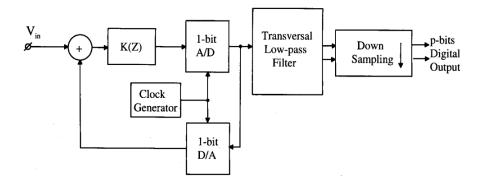

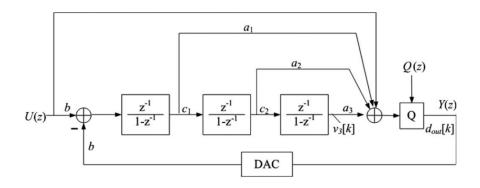

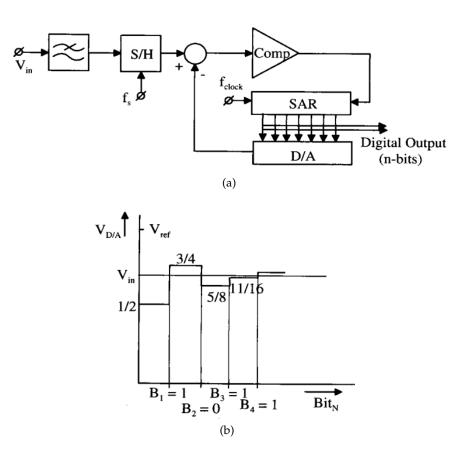

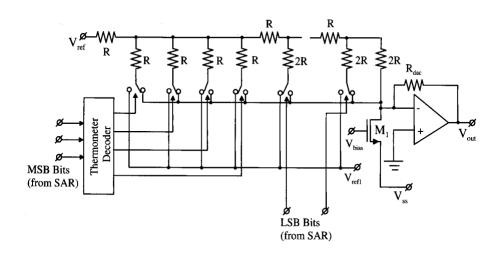

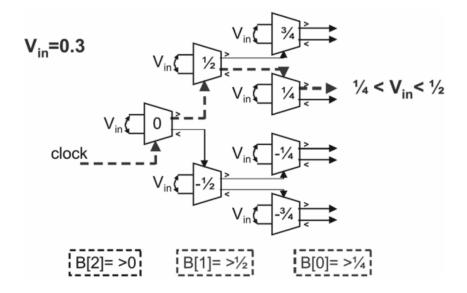

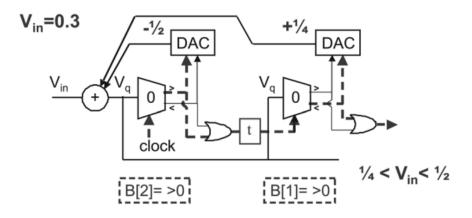

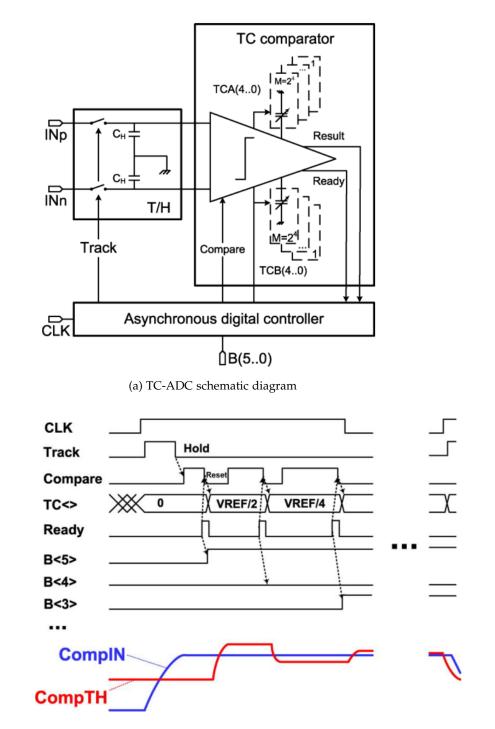

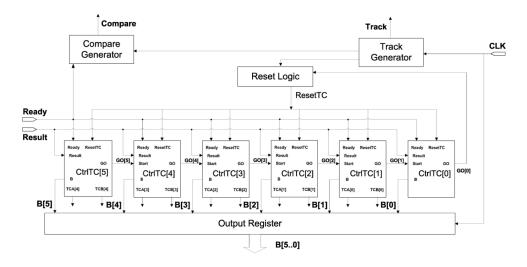

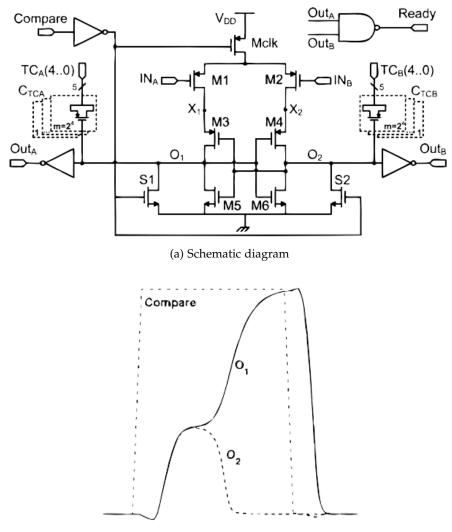

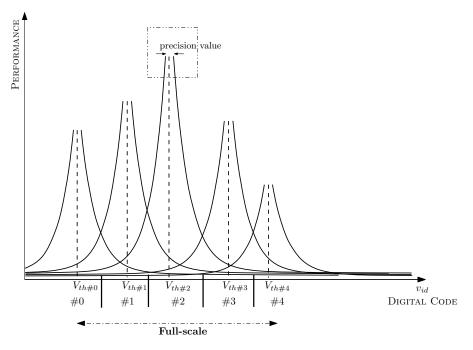

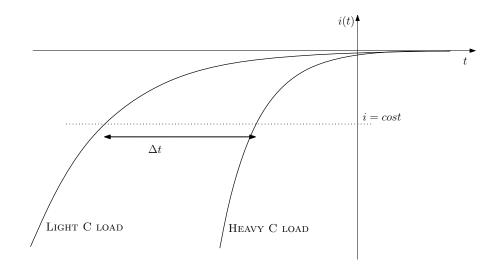

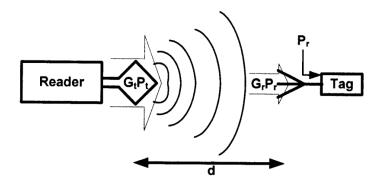

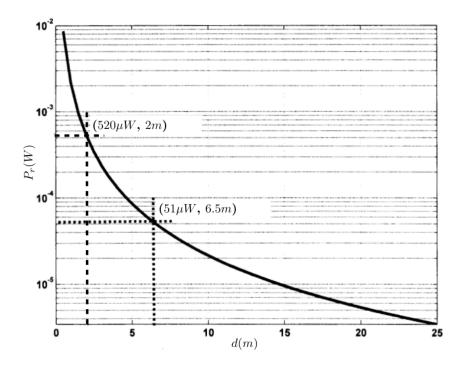

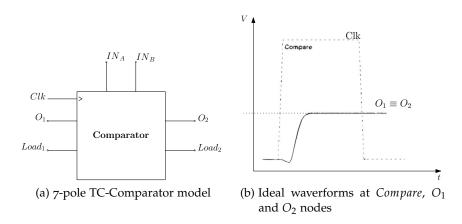

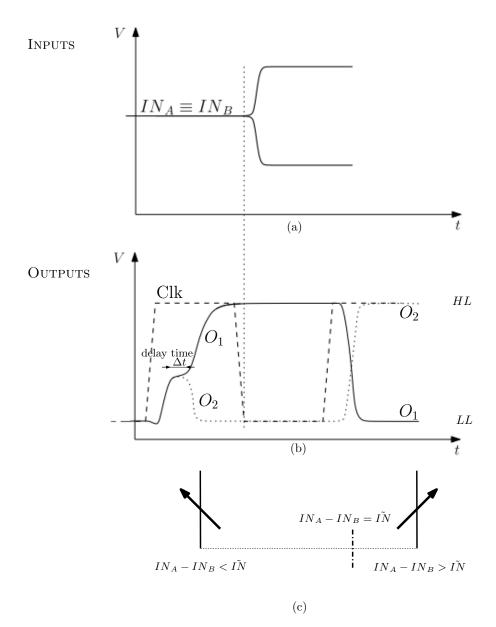

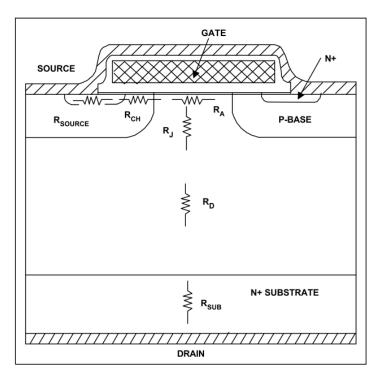

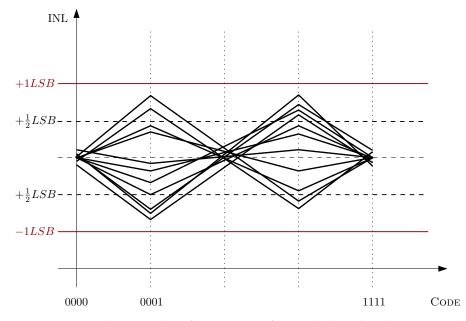

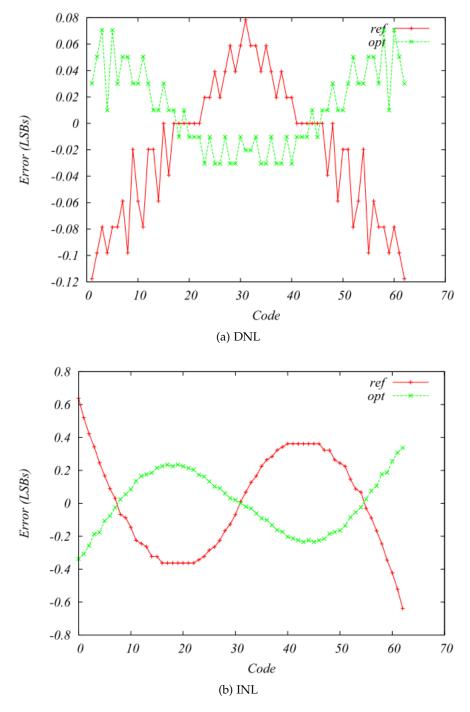

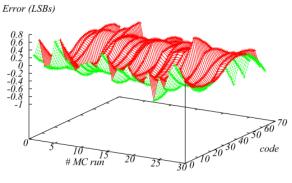

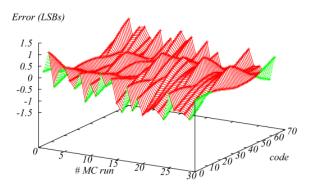

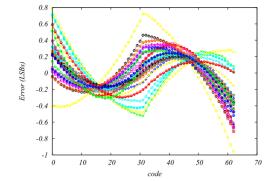

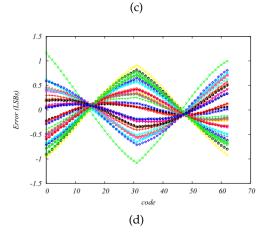

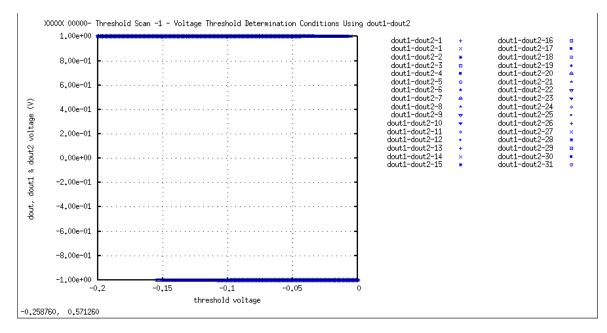

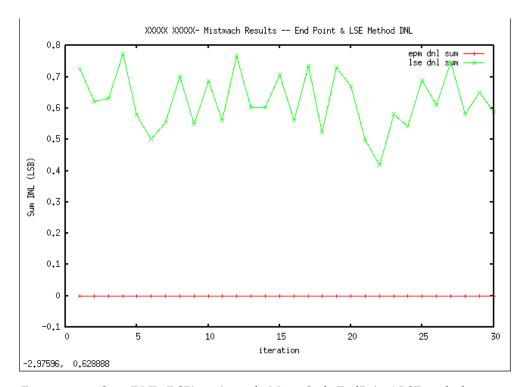

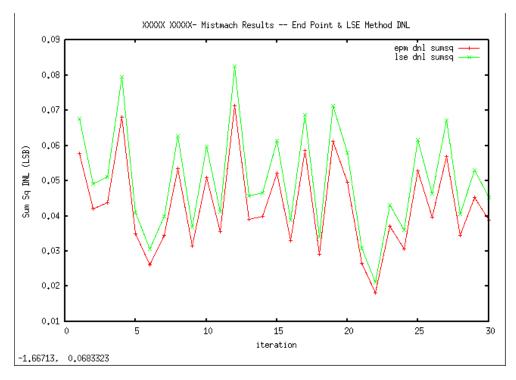

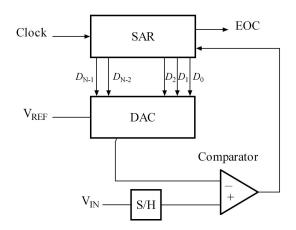

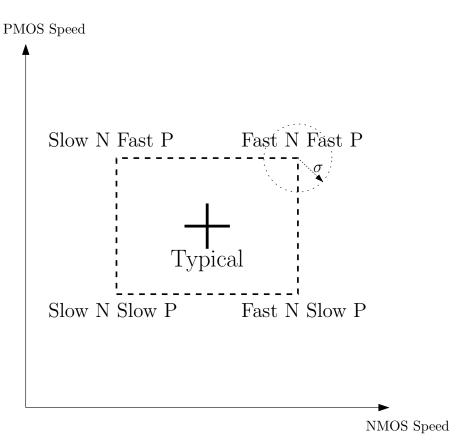

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A.2             | Nyquist sampling condition                                                                                             |  |