## UNIVERSITY OF PADUA

DEPARTMENT OF INFORMATION ENGINEERING

Master's degree in Control Systems Engineering

Power management for controlled power cycles of an integrated computer, environmental and electrical monitoring, and LED signaling: a C implementation for PIC24 microcontrollers

Thesis Supervisor: Prof. Alberto Morato Graduate Student: GIULIA PIZZATO 2089397

Academic Year 2023/2024 4 December 2024

#### Acknowledgements

Ringrazio prima di tutto i miei genitori, che mi sono stati accanto fin dai primi passi. Grazie mamma, grazie papà, non avrei mai potuto arrivare qui da sola, mi avete reso chi sono oggi. Non so esprimere a parole quanto vi voglio bene, il minimo che posso fare è dedicarvi questa laurea. Grazie anche a mio fratello, con cui ho condiviso un'infanzia, e con cui ancora rido alle lacrime.

Grazie alla mia famiglia: agli zii, ai nonni, ed ai cugini, grazie per i Natali, per i compleanni e le uscite, stare assieme è come una coperta calda, in cui mi sento al sicuro. Ringrazio anche la famiglia De Vicari, perché siete praticamente famiglia anche voi.

Ringrazio i miei amici, che so già leggeranno questa parte curiosi di cosa sto scrivendo di loro. Grazie ragazzi, perché mi siete accanto. Grazie a chi è qui da una vita, grazie Marta, Maria Laura, Maria ed Eugenia. Siete la mia base, il mio angolo sicuro. Grazie anche a chi invece ha vissuto al mio fianco questi cinque anni di università. Grazie per tutte le risate, le partite a carte, le gite, e le spiegazioni subito prima degli esami. Grazie a (in ordine alfabetico, non litigate): Ada, Alessia, Ambra, Cesco, Enrico, Giorgio, Grim, Lore, Madda, Marco, e Mina.

Infine voglio ringraziare Mattia, grazie di starmi accanto. Da quando sei entrato nella mia vita la stai riempiendo con tanta di quella pura e semplice gioia, che hai preso metà del mio cuore. Grazie, ti amo.

ii

#### Abstract

The objective of this thesis is to illustrate the development of a C program for a PIC24 microcontroller, installed on a multipurpose control and power supply board. Mounted on a device named ISObox, the aim of the program is to manage a controlled and clean power-up and shutdown cycle of an embedded computer system. ISObox is mounted on machinery, and therefore its power supply is directly provided by the machine's engine. When the machinery is ignited on or turned off, the microcontroller must ensure a clean shutdown of the embedded computer, to prevent sudden power loss that could cause filesystem damages or corruption. Similarly, at startup, the system must manage voltage fluctuations to avoid unintended power-ups or shutdowns. The microcontroller utilizes environmental sensors to monitor voltage, temperature, and humidity, taking appropriate actions to signal anomalies via bicolor LED or to shut down the embedded computer in critical situations. The communication between microcontroller and both sensors and embedded computer system is established through the I2C protocol, one as master and the other as slave. Through this communication continuous monitoring of the system's status is ensured.

iv

## Contents

| 1          | Introduction      |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                                                      |

|------------|-------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|            | 1.1               | The con                                                                                                | mpany and their main product                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                      |

|            | 1.2               | ISO BC                                                                                                 | DX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3                                                                                                                      |

|            | 1.3               | Evoluti                                                                                                | on of ISO BOX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4                                                                                                                      |

|            | 1.4               | The pro                                                                                                | oject                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                                                                                                                      |

|            |                   | 1.4.1                                                                                                  | Thesis structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7                                                                                                                      |

| 2 Hardware |                   |                                                                                                        | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                        |

|            | 2.1               | Mechan                                                                                                 | nics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9                                                                                                                      |

|            | 2.2               | PIC24F                                                                                                 | F MCU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10                                                                                                                     |

|            | 2.3               | Electro                                                                                                | nics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12                                                                                                                     |

|            |                   | 2.3.1                                                                                                  | Front Panel Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12                                                                                                                     |

|            |                   | 2.3.2                                                                                                  | PCIE CAN bus controller board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14                                                                                                                     |

|            |                   | 2.3.3                                                                                                  | PAPBB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 14                                                                                                                     |

|            |                   |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                        |

| 3          | Per               | ipherals                                                                                               | s Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                                                                                     |

| 3          | <b>Per</b><br>3.1 | -                                                                                                      | s Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>17</b><br>17                                                                                                        |

| 3          |                   | I/O cor                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                        |

| 3          |                   | I/O cor<br>3.1.1                                                                                       | mmunication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17                                                                                                                     |

| 3          |                   | I/O cor<br>3.1.1<br>3.1.2                                                                              | mmunication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17<br>18                                                                                                               |

| 3          | 3.1               | I/O cor<br>3.1.1<br>3.1.2<br>I2C cor                                                                   | mmunication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17<br>18<br>19                                                                                                         |

| 3          | 3.1               | I/O cor<br>3.1.1<br>3.1.2<br>I2C cor<br>3.2.1                                                          | mmunication       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . <td< th=""><th>17<br/>18<br/>19<br/>24</th></td<> | 17<br>18<br>19<br>24                                                                                                   |

| 3          | 3.1               | I/O cor<br>3.1.1<br>3.1.2<br>I2C cor<br>3.2.1<br>3.2.2                                                 | mmunication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17<br>18<br>19<br>24<br>24                                                                                             |

| 3          | 3.1<br>3.2        | I/O cor<br>3.1.1<br>3.1.2<br>I2C cor<br>3.2.1<br>3.2.2<br>3.2.3                                        | mmunication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17<br>18<br>19<br>24<br>24<br>27                                                                                       |

|            | 3.1<br>3.2        | I/O cor<br>3.1.1<br>3.1.2<br>I2C cor<br>3.2.1<br>3.2.2<br>3.2.3                                        | mmunication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17<br>18<br>19<br>24<br>24<br>27<br>29                                                                                 |

|            | 3.1<br>3.2<br>Obj | I/O cor<br>3.1.1<br>3.1.2<br>I2C cor<br>3.2.1<br>3.2.2<br>3.2.3<br><b>ective c</b><br>Objecti          | mmunication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ol> <li>17</li> <li>18</li> <li>19</li> <li>24</li> <li>24</li> <li>27</li> <li>29</li> <li>33</li> </ol>             |

|            | 3.1<br>3.2<br>Obj | I/O cor<br>3.1.1<br>3.1.2<br>I2C cor<br>3.2.1<br>3.2.2<br>3.2.3<br><b>ective c</b><br>Objecti<br>4.1.1 | mmunication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ol> <li>17</li> <li>18</li> <li>19</li> <li>24</li> <li>24</li> <li>27</li> <li>29</li> <li>33</li> <li>33</li> </ol> |

|          |              | 4.1.4 Power button actions       | 35 |  |  |  |  |

|----------|--------------|----------------------------------|----|--|--|--|--|

|          | 4.2          | Preconditions                    | 36 |  |  |  |  |

|          | 4.3          | Constraints                      | 37 |  |  |  |  |

| <b>5</b> | Software     |                                  |    |  |  |  |  |

|          | 5.1          | Setup and Diagnostics            | 39 |  |  |  |  |

|          | 5.2          | Logic flow                       | 41 |  |  |  |  |

|          |              | 5.2.1 Isoboard Firmware          | 41 |  |  |  |  |

|          |              | 5.2.2 New ISO BOX firmware       | 45 |  |  |  |  |

|          | 5.3          | Code Schemes                     | 53 |  |  |  |  |

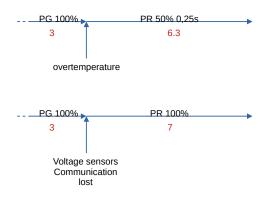

|          | 5.4          | Cranking                         | 61 |  |  |  |  |

|          |              | 5.4.1 What is cranking           | 61 |  |  |  |  |

|          |              | 5.4.2 Cranking problem           | 63 |  |  |  |  |

|          |              | 5.4.3 Code for cranking          | 64 |  |  |  |  |

| 6        | Vali         | dation                           | 71 |  |  |  |  |

|          | 6.1          | Power-On Tests                   | 72 |  |  |  |  |

|          |              | 6.1.1 ISO BOX mode               | 73 |  |  |  |  |

|          |              | 6.1.2 POWER BOX mode             | 74 |  |  |  |  |

|          | 6.2          | Normal Run Tests                 | 74 |  |  |  |  |

|          | 6.3          | Power-off Test                   | 75 |  |  |  |  |

|          | 6.4          | Errors                           | 75 |  |  |  |  |

|          | 6.5          | Registers functionality          | 77 |  |  |  |  |

| 7        | Fut          | ure Developments and Conclusions | 79 |  |  |  |  |

| Bi       | Bibliografia |                                  |    |  |  |  |  |

# **List of Figures**

| 1.1  | ITPhotonics logo $[1]$                                                                                                                | 1  |

|------|---------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Polispec [2] $\ldots \ldots \ldots$ | 2  |

| 1.3  | Original ISO BOX Rendering [3]                                                                                                        | 3  |

| 1.4  | Modernized ISO BOX rendering                                                                                                          | 5  |

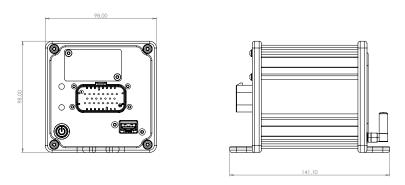

| 2.1  | ISO BOX dimension scheme                                                                                                              | 9  |

| 2.2  | ISO BOX front panel. From Figure 2.2b we can see: A)Green-                                                                            |    |

|      | Red Status LED B)<br>Red-Blue Status LED C)<br>Power button D)I/O $$                                                                  |    |

|      | connector E)USB interface                                                                                                             | 10 |

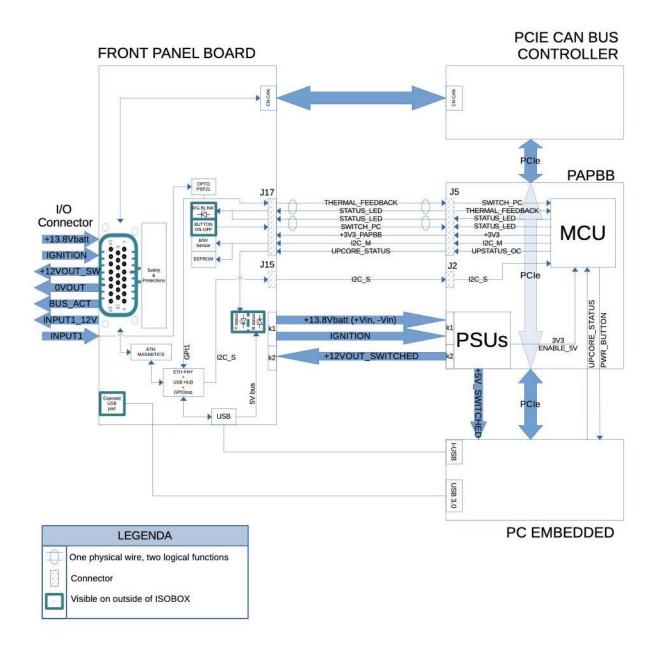

| 2.3  | ISO BOX electronic schematic                                                                                                          | 13 |

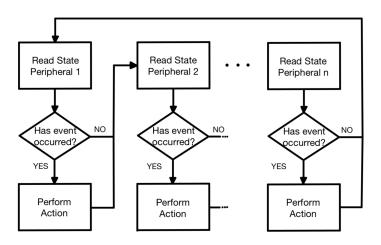

| 3.1  | Polling functioning block scheme                                                                                                      | 18 |

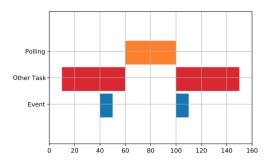

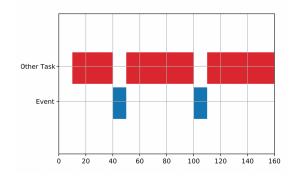

| 3.2  | Example of an event being missed by the processor that utilizes                                                                       |    |

|      | polling [4] $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                          | 18 |

| 3.3  | CPU activity allocation when each event is accompanied by an                                                                          |    |

|      | interrupt $[4]$                                                                                                                       | 19 |

| 3.4  | Interrupt block scheme                                                                                                                | 20 |

| 3.5  | Interrupt nesting $[4]$                                                                                                               | 22 |

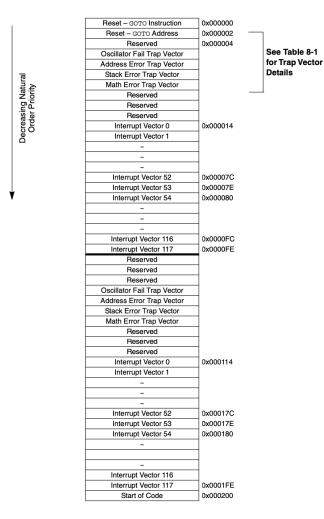

| 3.6  | IVT [10]                                                                                                                              | 23 |

| 3.7  | I2C lines of communication [6]                                                                                                        | 24 |

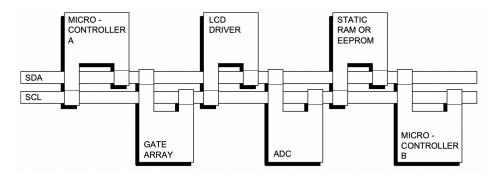

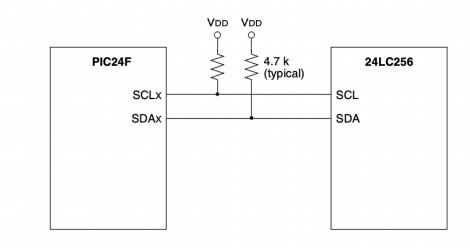

| 3.8  | Typical I2C Interconnection Block Diagram [5]                                                                                         | 25 |

| 3.9  | I2C communication between the MCU and a sensor, read with an                                                                          |    |

|      | oscilloscope                                                                                                                          | 25 |

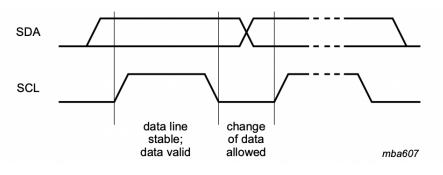

| 3.10 | I2C data recognition [6] $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                        | 26 |

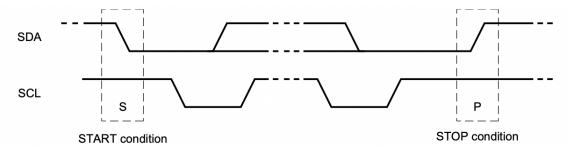

| 3.11 | I2C START and STOP signals [6]                                                                                                        | 27 |

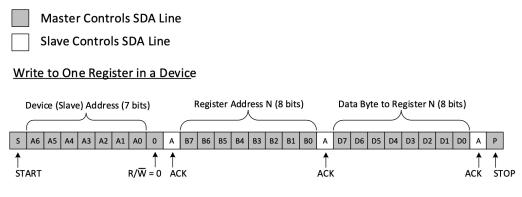

| 3.12 | Example of the writing of a single byte to a slave register $[8]$                                                                     | 28 |

| 3.13 | Example of the reading of a single byte to a slave register $[8]$                                                                     | 29 |

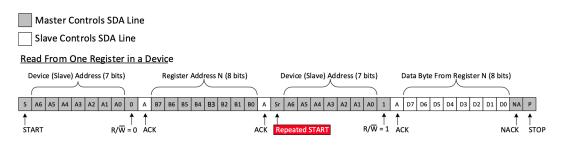

| 3.14 | Example of sequence of events, START case used [5]                                                                                    | 31 |

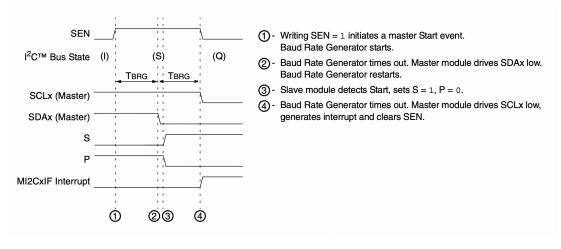

| 3.15 | Example of sequence of events, Master Read Transmission case                                               |    |  |  |

|------|------------------------------------------------------------------------------------------------------------|----|--|--|

|      | used [5] $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                  | 32 |  |  |

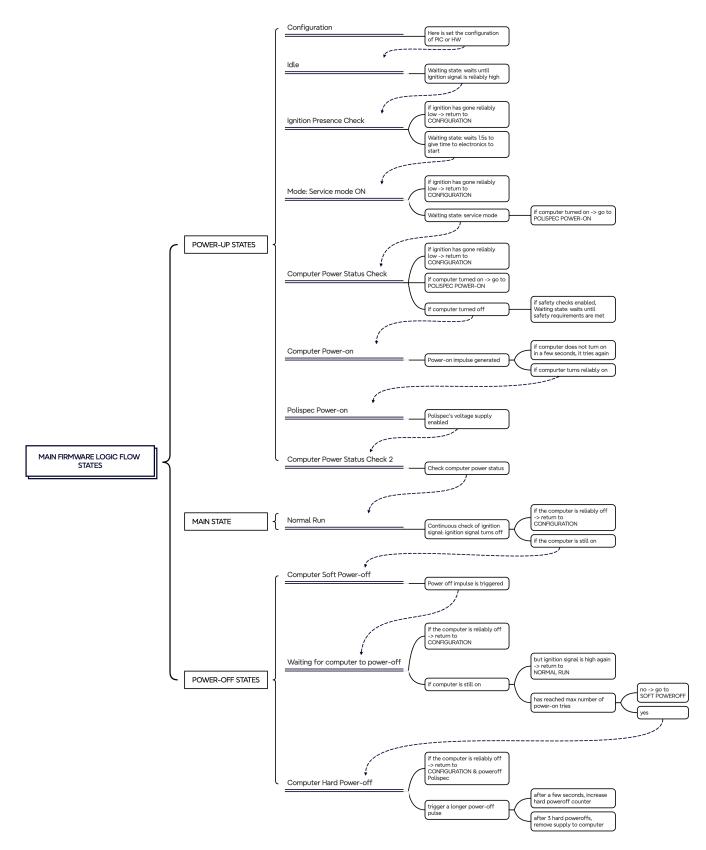

| 5.1  | Old ISO BOX firmware logic flow                                                                            | 42 |  |  |

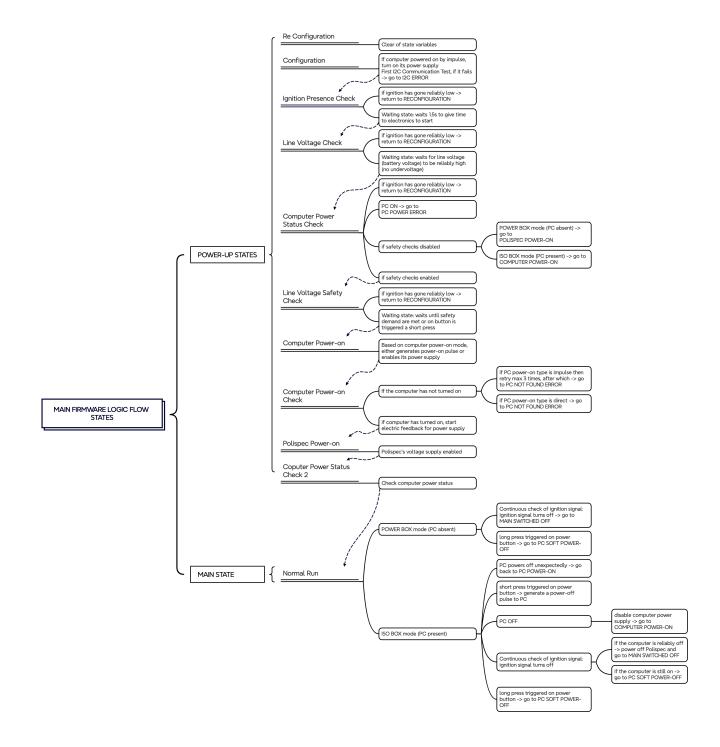

| 5.2  | Current ISO BOX firmware logic flow, part 1                                                                | 46 |  |  |

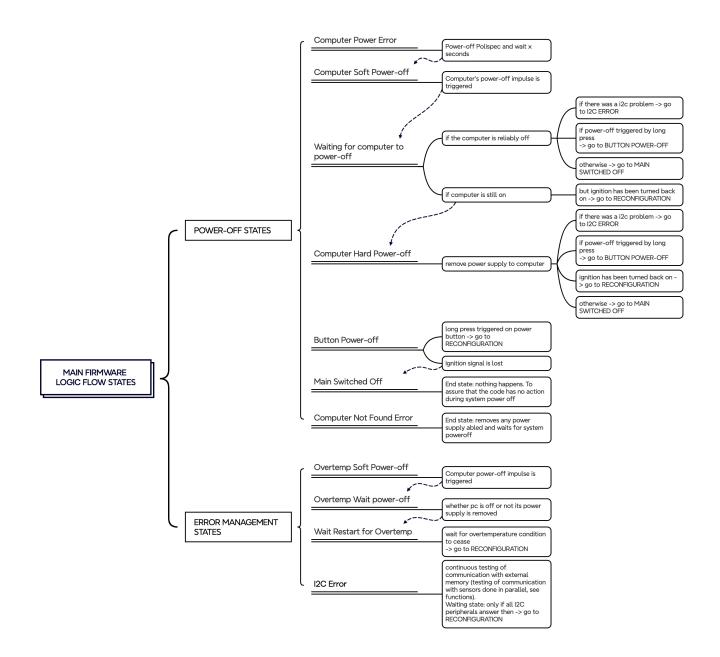

| 5.3  | Current ISO BOX firmware logic flow, part 2                                                                |    |  |  |

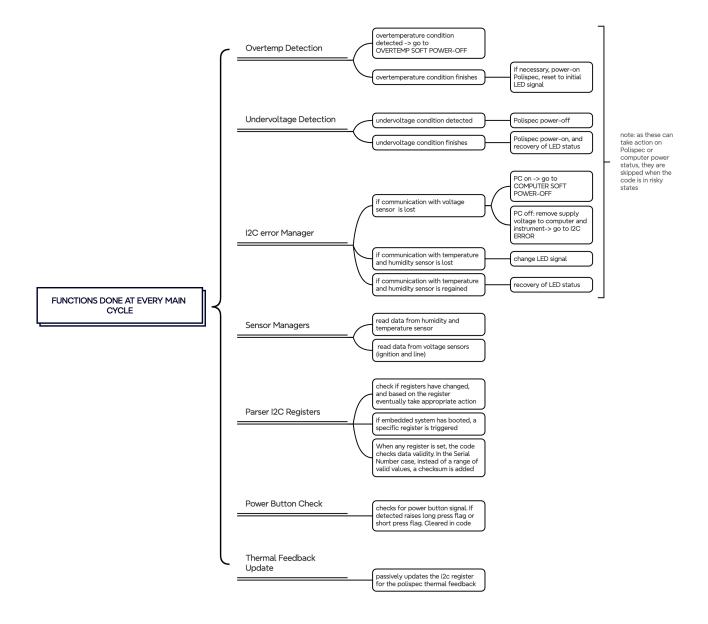

| 5.4  | Functions performed by firmware at every main cycle $\ldots$ .                                             |    |  |  |

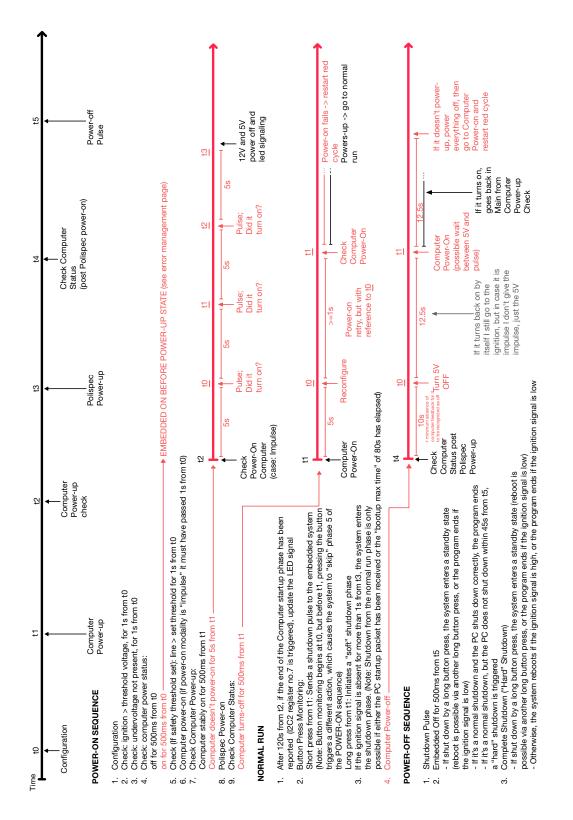

| 5.5  | code evolution scheme with embedded $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                     | 54 |  |  |

| 5.6  | code evolution scheme without embedded                                                                     | 55 |  |  |

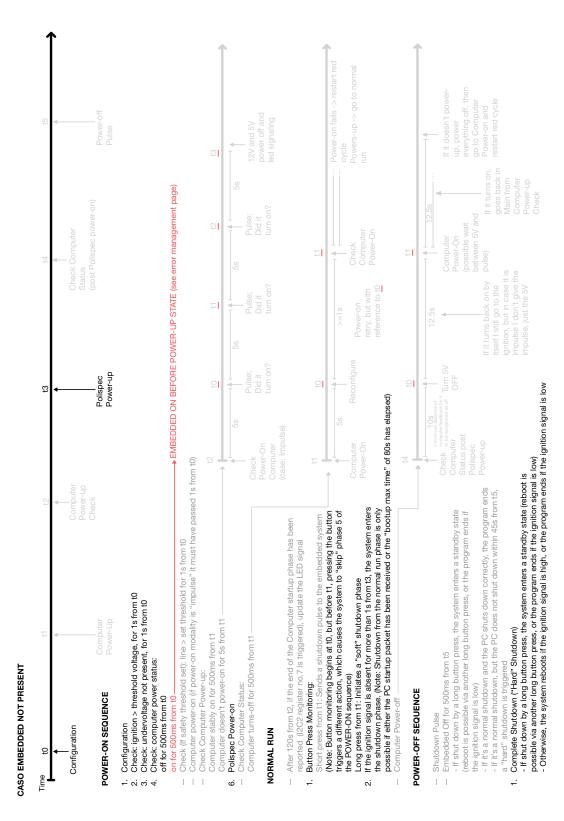

| 5.7  | code error evolution scheme $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 56 |  |  |

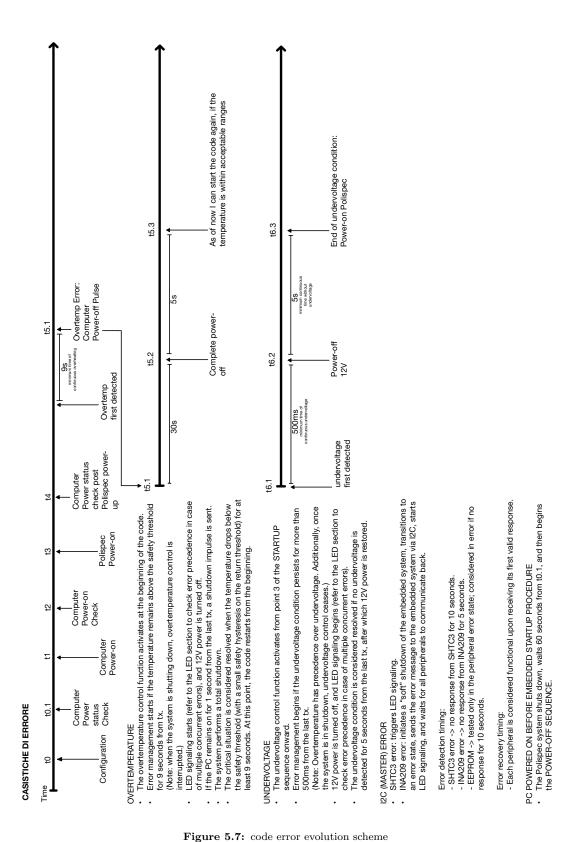

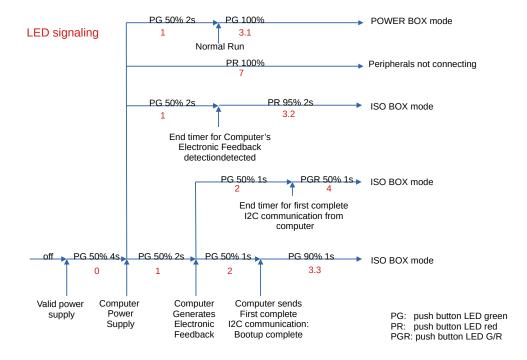

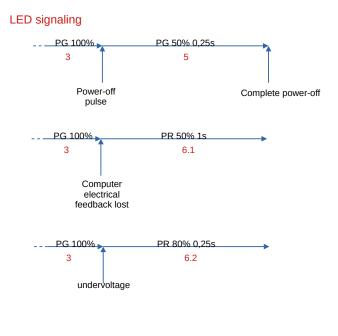

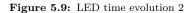

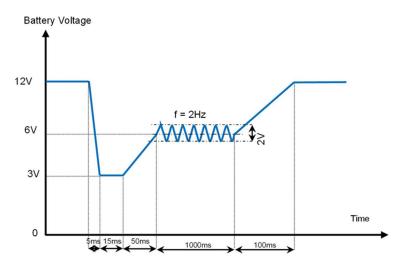

| 5.8  | LED time evolution                                                                                         | 60 |  |  |

| 5.9  | LED time evolution 2                                                                                       | 60 |  |  |

| 5.10 | LED time evolution 3                                                                                       | 61 |  |  |

| 5.11 | cold cranking, diesel engine $[12]$                                                                        | 62 |  |  |

| 5.12 | Real case: voltage cranking, diesel car                                                                    | 63 |  |  |

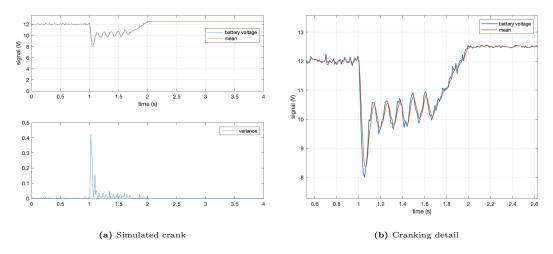

| 5.13 | Example of a simulated crank using the MATLAB code. Together                                               |    |  |  |

|      | are also shown the mean and variance used. On the right a detail                                           |    |  |  |

|      | is shown                                                                                                   | 67 |  |  |

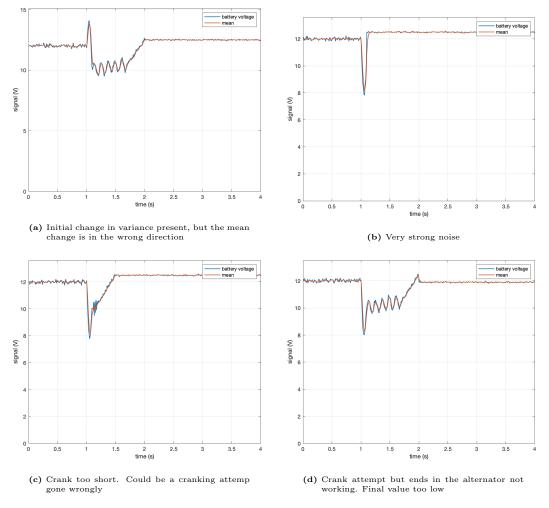

| 5.14 | Example of simulated Figure showing four different plots, each                                             |    |  |  |

|      | representing a signal resembling a cranking waveform but correctly                                         |    |  |  |

|      | identified by the algorithm as not being a cranking event $\ . \ . \ .$                                    | 69 |  |  |

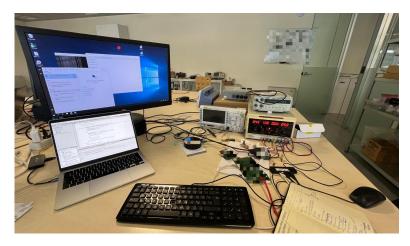

| 6.1  | Setup - sensitive parts are blurred                                                                        | 72 |  |  |

# List of Acronyms

| MCU  | MicroController Unit                  |

|------|---------------------------------------|

| MPU  | MicroProcessors Unit                  |

| PSU  | Power Supply Unit                     |

| CPU  | Central Processing Unit               |

| ALU  | Arithmetic Logic Unit                 |

| IRQ  | Interrupt ReQuest                     |

| IVT  | Interrupt Vector Table                |

| AIVT | Alternate Interrupt Vector Table      |

| ISR  | Interrupt Service Routine             |

| PC   | Program Counter                       |

| SDA  | Serial Data Line                      |

| SCL  | Serial Clock Line                     |

| FSM  | Finite State Machine                  |

| OS   | Operating System                      |

| IDE  | Integrated Development<br>Environment |

## Chapter 1

## Introduction

## 1.1 The company and their main product

This project has been developed in collaboration with ITPhotonics.

ITPhotonics was founded in 2012 by its four current partners, who identified an opportunity for innovation in the market. Since then, they have continued to refine their products.

ITPhotonics is specialized in spectrophotometry and applied electronics [1], in its various forms.

Figure 1.1: ITPhotonics logo [1]

The main line of products of ITPhotonics is Polispec (Portable and On LIne SPECtrophotometer) a line of compact spectrophotometers, which varies in spectrum width, in branch, and in application [2].

It is used to obtain a data matrix from various products, which can come from different sectors. These include the industrial sector (e.g. cataphoresis processes, mashed potato production, wastewater analysis), the chemical sector, and the agri-tech sector. Currently, their strongest focus is in agri-tech (e.g. grains, silage, forage, raw materials), where ITPhotonics' instruments ensure the monitoring of the final product.

The functionality of Polispec is designed to be both simple and effective. It has a

scan window, which must be in contact with the product flow during the process. The obtained data are stored and processed by a computer, which are then visible to the client either on the machinery panel board or on a separate screen, and can be downloaded via cable or Wi-Fi.

Polispec has two operative modes: handheld and online. In handheld mode, the device has an internal battery that makes it portable, and communicates the obtained data to an external computer, either through Wi-Fi or through a cabled communication, depending on the selected configuration. In online mode, the spectrophotometer is stably mounted on machinery that works close to the product, where it acquires data. The computer that then does the elaboration, can be internal to the Polispec or an external one.

Figure 1.2: Polispec [2]

In the online case, the Polispec is powered directly by the machinery, but some Polispec devices may not be equipped with power supply circuitry compatible with automotive voltage and disturbance ranges. However, machinery voltages, especially in automotive applications, can experience significant fluctuations.

To solve this issue, POWER BOX has been introduced, an optional accessory which ensures proper management of the spectrometer power supply.

If the final client does not own a personal external computer, it can be provided by ITPhotonics. The computer can be placed inside Polispec itself, or inside the POWER BOX.

When the computer is inside the POWER BOX, it is renamed ISO BOX. In this setup, the ISO BOX also regulates the power cycles for the computer, protecting it from significant power fluctuations which could potentially lead to hardware

Figure 1.3: Original ISO BOX Rendering [3]

damage from frequent powering on and off, as well as software malfunctions or filesystem corruption.

Sometimes the customer may want to install ISO BOX not for its power management tools, but just to separate the elaboration system from the measuring instrument, obtaining more flexibility in switching Polispec between online mode and handheld mode.

## 1.2 ISO BOX

As the catalogue sais "ISO BOX is an intelligent control unit that, in addition to managing the power supply to the Polispec sensors when installed on selfpropelled or towing machinery, processes the signals it receives from the sensor and integrates sensor operation in the machine ISObus network. The same control unit can be used to integrate systems in proprietary CANbus network" [3].

ISO BOX main tasks are:

- powering on and off the computer in a clean and controlled manner

- continuous monitoring of ISO BOX environmental data via humidity and temperature sensors

- continuous monitoring of the battery and ignition voltage via voltage sensors

- respond to information requests from internal computer, which could ask for diagnostics information or setup data

- power on or power off the spectrometer, based on voltage levels or embedded PC requests

- save setup data changes

- in thresholds setup data changes, check that the chosen values are in valid ranges, and if not set the minimum/maximum value of the range

- signal via LED the working status of ISO BOX, including potential errors

### 1.3 Evolution of ISO BOX

When Polispec is in online mode, it can contain internally the computer, placing it in the slot otherwise occupied by the battery when in handheld mode.

But this option was not always available. Initially, Polispec could not house an internal computer, making the ISO BOX the only solution for power regulation and communication.

Born as just an accessory, it was electronically very different from the Polispec. They used different boards and the code developed was written for an atmega328 MicroController Unit (MCU). Communication between the computer and the MCU was hadled via UART, using a internally developed communication protocol with 19 possible packets and their associated responses. As the design evolved to allow the computer to be housed directly inside the Polispec, a new board, named PAPBB (Powerboard), was developed.

PAPBB was more compact, and had on board a new MCU, specifically a Microchip controller from the PIC24F family. This was chosen for better control of libraries and devices. Additionally, it allowed I2C communication, and since it was already in use within the company, it was well-known to the engineers. This board's MCU, working closely with another board's (called "Supply board") MCU, managed the computer's power cycle, monitored the environment status, and signaled the Polispec status via LED.

Given the similarities between the PAPBB and the old ISO BOX, it was a natural to consider modernizing ISO BOX to work with the new board, improving its functionality and alignment with the updated design. The choice of modernizing the original ISO BOX offers significant economic advantages, as producing a single board instead of two, simplifies manufacturing and allows better agreements with suppliers. Furthermore, the new board is smaller than the previous one, allowing for more compact and cost-effective packaging.

### 1.4 The project

After explaining the context in which this thesis project was developed, we can now look at it in more detail.

The main objective of this project is the development of the firmware for this new version of ISO BOX.

The new code is supposed to be written in the same environment as the one written for Polispec, but using the basic structure of the previous ISO BOX algorithm. So the merging of these two previous works was the first objective. The second was to implement new novelties and improvements that weren't previously present.

Indeed, this modernization allowed to put together some qualities. For example by uniforming the board, it was also possible to electronically make indistinguishable ISO BOX and POWER BOX, making the change between the two easy and efficient. Therefore the code, assuming it has the knowledge via setup data of whether the embedded is present or not, has to be able to handle both the ISO BOX and the POWER BOX cases, since it can be uploaded on both.

Also, as the MCU allowed for I2C communication, the self-developed communication protocol was removed in favour of I2C, which is a wide spread, and secure protocol.

(a) ISO BOX front view

(b) ISO BOX rear view

Figure 1.4: Modernized ISO BOX rendering

The project was carried out in the following order, detailing each step taken throughout the process.

After an introductory study of ANSI C, with a focus on interrupts, the first step was to analyze the structure of the two previous codes. One of the key goals was to establish the main structure of the final code, and the branches it must take in case of errors or changes in the setup. While developing the logical flow, the practical elements have been also studied, such as the the functioning and the features of a MCU from the PIC24F family, and the I2C protocol, needed for communication with both the embedded computer and the peripherals (temperature sensors, voltage sensors and EEPROM).

Once this basis were set the development of the actual code started. Some libraries from the Polispec code were reused, with adaptations made where necessary. Any modifications were carefully documented. Due to the similar environments and overlapping in functioning, the new code was largely based on the Polispec code. A key similarity was in the communication between the MCU and the computer. In the Atmega328 setup, communication was UART-based, whereas in the PIC24F system, it relied on I2C, similar to the Polispec implementation. The PIC MCU has two I2C ports: one configured as a master for communication with peripherals, and the other as a slave for interaction with the computer. Previously developed libraries were utilized for this, but with certain aspects

Previously developed libraries were utilized for this, but with certain aspects revised, such as the slave registers, and improvements introduced.

However, despite these similarities, there are substantial changes. As previously mentioned, in the Polispec electronic system, PAPBB coordinates with the Supply board. In the new context of ISO BOX the relationship between the two is different. For instance, in the previous design the PAPBB was not equipped with an external memory, it relied on its flash memory to store permanent information. In this new setup the PAPBB has an EEPROM, which the PIC MCU can access via I2C.

Another difference is in the access to the LEDs. In Polispec's case, only the Supply had direct access to the external status LEDs. The PAPBB had to communicate its status to the Supply, so that it could then change the LED signals. Now that the LEDs are directly controlled by the PAPBB, the associated code had to be modified to accomodate this necessity. The LEDs access introduced an additional problem. The type of LED used required two pins were to control them, however the pin available on the PIC24 were all utilized. To solve this problem an ingenious solution has been adopted, that allowed two pins to be used both as inputs and as outputs. This will be better explained in Chapter 5.

Great importance has been given to backward compatibility. In some case the reasoning is immediate, for example in the choice of the status LEDs signals. Those were kept as before, with new necessary additions. Backward compatibility is also one of the reasons why already developed library were preferred, even when substantial modifications were required. Libraries from both Supply and PAPBB in Polispec's system were used, with all changes made during the adaptation process documented. This allowed for a more trustworthy validation process, and easier debugging process.

New code setup conditions have been added, allowing the code to be used for both the POWER BOX and ISO BOX systems. A dedicated setup register has been introduced, to indicate the presence or absence of the embedded computer, causing the code to behave accordingly. Additionally, both methods of powering on of the embedded are now considered. To clarify, the computer utilized can be configured to turn on as soon as power is supplied or to wait for a power-up signal, similar to a standard personal PC. Before, it was assumed the computer would always be set on the first configuration. Now, the setup allows the user to specify the power-on mode, to assure a correct power cycle of the computer.

Lastly, two brand new features were added. The first is a safety check for I2C responses. The system now constantly verifies whether the voltage or temperature sensors, stop responding. For each scenario the proper set of action has been set and implemented.

The second feature relates to the front power button. While before its function was limited to the common function, it now recognizes both long and short presses. Depending on the duration of the press and the current section of the code, the system performs different actions.

#### **1.4.1** Thesis structure

To assure that all previously listed elements are covered, but to allow a better flow of explanation, this document will be structured as follows. The document will begin with a quick overview of the hardware relevant components in Chapter 2. Chapter 3 will discuss the necessary theoretical framework, and finally the code and its validation will be thoroughly discussed in Chapter 5 and Chapter 6. Finally, we will conclude with potential future improvements and final remarks.

## Chapter 2

## Hardware

While the design or analysis of the associated hardware is beyond the scope of this project, mechanics and electronics are still described here to provide context for the firmware's operation.

As previously mentioned, the firmware is uploaded on a device called ISO BOX, which works in an environment with two other elements: Polispec and a generator (machinery's battery).

This document will focus exclusively on the latest version of the ISO BOX, which runs the new firmware, and will not cover the previous versions.

### 2.1 Mechanics

Figure 2.1: ISO BOX dimension scheme

ISO BOX is a  $98 \times 98 \times 141.1$  mm aluminum box, with PA12 (nylon) frames. It is designed to withstand harsh environments and is rated IP65 for dust and water resistance. It features mounting support brackets, a heat sink on the back, and a Wi-Fi antenna for remote access to the instrument, facilitating remote troubleshooting and repairs.

As shown in Figure 2.2, ISO BOX features a front panel that connects both to the machinery and the instrument, which will be explained in greater detail when the electronics are introduced. The panel includes two sets of status LEDs, a USB interface, a power button, and a removable plate that conceals configuration options.

(a) ISO BOX front panel with removable plate

(b) ISO BOX front panel without removable plate

Figure 2.2: ISO BOX front panel. From Figure 2.2b we can see: A)Green-Red Status LED B)Red-Blue Status LED C)Power button D)I/O connector E)USB interface

The two sets of LEDs consist of one red and green pair dedicated to indicating the status of the ISO BOX code, and one yellow and blue pair providing information on the embedded power supply and overall power status. The functionality of the first set will be explained in greater detail in Chapter 5.

### 2.2 PIC24F MCU

A MCU is and integrated circuit that, just like MicroProcessors Unit (MPU)s, was introduced to replace antiquated multi-component Central Processing Unit (CPU)s. MCUs "combine all the necessary elements of a microcomputer system onto a single piece of hardware. MCUs do not require additional peripherals or complex operating systems to function" [9], contrary to MPUs.

The MCU used in this project is of the family PIC24F, hereafter also referred to as

PIC for brevity. The PIC Microcontroller, developed by Microchip Technology, "is the world's smallest microcontroller, and it is found frequently in robotics, home and industrial automation and renewable energy systems" [9].

The PIC24 MCU offer many features, however, to avoid giving information of no use or just accessible by the datasheet, only the main features used in the project will be presented.

**Core Features** The MCU used in this project was a PIC24F.

Its CPU features a 16-bit data modified Harvard architecture, which means it feature separate memory spaces and busses for program and data, allowing parallel access and cosequent faster performances.

Key specifications include:

- **Memory**: it has 64k bytes of Program memory and 22k bytes of Program Memory instructions

- **Registers**: the PIC24F devices feature sixteen 16-bit working registers. These registers can act as data registers, address registers, or address offset registers

- For example the CORCON Register (CPU Control Register) is a 16 bit register where each bit is a flag that gives information on one factor of CPU or Arithmetic Logic Unit (ALU)

- **Program Counter**: Program Counter (PC), which tracks the memory address of the next instruction to be executed, is 23 bits wide, allowing it to address up to 4 million instructions in the user program memory space

**Peripherals and Tools** The PIC24F MCU has a couple of useful tools that are worth mentioning.

- **Timers**: Five 16-bit timers were offered, each with its readable/writable registers and its interrupt. There are 3 types of timers A,B and C. The timer used was of Type A, because "the unique features of a Type A timer allow it to be used for timekeeping functions or as a secondary system clock source" [11]

- I2C module: it has two I2C communication ports, in which it can be be set to act as a master, a slave, or a master in a multi master environment. It supports independent master and slave logic, 7-bit and 10-bit device

addresses, general call address, and clock stretching to provide delays for the processor to respond to a slave data request.

## 2.3 Electronics

On the inside ISO BOX contain three main electronic boards, that will be addressed as "Front panel Board", "PCIE Can Bus Controller board" and "PAPBB". For company privacy reasons, the full component numbers of the elements used in the electrical boards will not be mentioned. The key characteristics will be listed instead.

#### 2.3.1 Front Panel Board

The Front Panel Board is directly connected to ISO BOX's front panel, and houses the I/O connector where both the machinery (with its CANbus communication and battery voltage) and the Polispec are connected. Figure 2.3 illustrates all the signals passing through the I/O connector.

The first two signals (+13.8Vbatt and IGNITION) come from the machinery. When both signals are high, the MCU is powered on, initiating firmware execution. +13.8Vbatt is the battery voltage, and since the battery is always connected, it is the ignition signal that dictates when the system is starting, signaling ISO BOX to begin its operations as well. In the case of automotive applications (e.g. agricultural machinery in the field), the ignition is a digital signal that indicates the turning of the physical key, which is followed by cranking. The cranking process and its associated challenges will be presented in Chapter 5.

For control purposes, the MCU can activate a power feedback loop, allowing it to remain powered on even if the ignition signal goes low. This feature was introduced to allow the MCU to have time to safely power off the embedded computer when the key is turned off. It can be activated only by the PIC itself. In Chapter 5 we'll explore the management of this feedback, to assure proper power off of the system, avoiding the error case of the PIC keeping the system powered on when not required.

The I/O connector includes 7 pins dedicated to CAN bus communication: two sets of 3 pins for connecting to two separate CAN buses, and an additional pin for handling changes in communication setup. These signals are utilized, via the PCIE CAN bus controller board (a commercial component), to transmit the computed data from the embedded computer to the machinery's panel board.

Figure 2.3: ISO BOX electronic schematic

The remaining pins on the I/O connector are dedicated to signals used or provided by the Polispec. The Polispec is powered by a 12V supply, which is enabled by the MCU when required, and regulated through the Power Supply Unit (PSU) of the PAPBB.

The two signals INPUT1 and INPUT1\_12V, form a loop that closes when the Polispec is powered and not in overtemperature condition. It is otherwise always open. By monitoring INPUT1 and knowing the power status of the Polispec, we are informed on its overtemperature status. This is achieved through an optoiso-lator: if the optoisolator in the Polispec is open, it indicates that the instrument is either not powered or is in overtemperature.

The BY (Blue and Yellow) LED depends on the PC's power status. The blue LED lights up when the PIC activates the 5V signal to power on the embedded computer, while the yellow LED turns on when the embedded computer sends an electronic feedback signal. When both LEDs are on, the resulting color is green, indicating that the system is functioning properly. The RG (Red and Green) LED is controlled directly by the PIC, and its signals will be detailed later in this thesis.

Lastly, the remaining elements on the Front Panel Board worth mentioning, are the environmental sensors (temperature, humidity, and voltage sensors) used to assure ISO BOX's safety, the EEPROM memory, and the magnetics used to ensure Ethernet signal integrity.

#### 2.3.2 PCIE CAN bus controller board

As already stated the PCIE CAN BUS CONTROLLER board is a commercial board, dedicated to the CAN BUS communication with the panel board of the machinery and the embedded computer.

#### 2.3.3 PAPBB

The final board is the PAPABB, the power and control board. This is where the MCU running our code is located, and where power electronics control takes place. The PSUs make sure that the signals are clean, and DCDC converters generate the 5V (to power on the computer), 3.3V, and 12V (to power on the Polispec) signals from the battery voltage.

From the MCU, which is powered by 3.3V, many signals are visible. It has 2 lines of I2C communication. In our setup it acts as a master on one line, where it communicates with sensors and EEPROM, and as slave in the other, where it

communicates with the computer.

In addition, we can see two I/O lines that are used simultaneously for the GR status LED (output) and to read two inputs: the Polispec thermal feedback and the power button. As previously stated, moving the LED control from the Supply board to the PAPBB board, implied the necessity of utilizing two PIC pins, but all available pins were already in use. To solve this, the decision was made to use two pins as both inputs and outputs.

To obtain this dual functionality, the lines are switched every 10 ms between input and output modes. When set as outputs, they pilot the status LED signaling, when set as inputs they read the two signals. A possible issue could be that the LED turns off in the input state. However, since the switching rate is 100 Hz, it would be difficult for the human eye to perceive any noticeable difference.

Another concern is the correct memorization of the power button signal. Unlike the thermal feedback, that doesn't require memory of its previous state, the power button signal must be tracked over time to determine the duration of the press. This distinction is necessary because the system differentiates between a long button press and a short one. Every 10 ms, the system checks if the button signal has changed (from high to low or vice versa), and based on how long the signal remains low (button pressed), it acts accordingly. How these two signals are distinguished and used is explained better in Chapter 5.

The concern is that during the switching of the LEDs, the MCU might miss a button press. This is prevented in two ways. First, there is an obvious physical limit, as it's unlikely that the client could press the button for less than 10 ms. For additional safety, a lower bound is placed on the duration of the button press. If the button is pressed for less than 500 ms, the signal is not considered. This approach helps prevent both missed signals by the MCU and accidental presses by the user.

The last signal, "UPCORE\_STATUS" is the power status of the embedded computer. It is used in the code to make decisions on the action to take.

## Chapter 3

## **Peripherals Communication**

### 3.1 I/O communication

In this project, we work with various communicating devices, including both external peripherals and internal components of the PIC, such as timers. The communication between the PIC and these, can be implemented both asynchronously or synchronously. In asynchronous communication, unlike synchronous, the data stream is not accompanied by a clock signal that manages coordination. The data are sent when available, with the begin and end of the message signaled via additional data (start and stop bits).

This setup, combined with the fact that the speed of data elaboration of the CPU is usually way higher than the speed of transmission data of the peripherals, can lead to issues in relation to synchronization. The CPU could request data to the peripherals when they are not ready, or the peripherals could send data when the CPU is occupied with other operations. Consequently, various errors could occur, such as data not being read or sent, collisions, or the transmission of erroneous or inconsistent data. Additionally, due to the speed difference, if the CPU were to often wait for peripherals to respond or complete their operations, it would cause a significant waste of efficiency, as the CPU could otherwise carry out other tasks.

So a synchronous communication is preferable. To synchronize these two elements, multiple solutions have been proposed in time. We explain here two main ones: polling and interrupts.

### 3.1.1 Polling

In polling is the CPU that oversees communication.

It periodically inquires each peripherals about its status. If a state change is detected, the CPU starts the appropriate set of actions to handle the event. Once the CPU has finished its operations, it resumes its cycle of peripherals interrogation, eventually checking each one.

This is can be implemented easily, even using basic sequences of if statements.

Figure 3.1: Polling functioning block scheme

This method resolves many synchronization issues, as only one component (the CPU) controls the process. Collisions risks are significantly reduced, and problems such as data not being sent or received are easier to manage. If appropriate protocols are used, control of correct and consistent data can also be assured. However, polling has clear efficiency drawbacks. The CPU uses significant computational power to query the peripherals, and it cannot perform other tasks while waiting for I/O devices computation and response.

Figure 3.2: Example of an event being missed by the processor that utilizes polling [4]

If the polling interval is too long, events may be even missed. So if too many peripherals are connected, or if even one slow peripheral is in the loop, it can cause delays, increase the risk of missed events, and slow down the entire system.

#### 3.1.2 Interrupts

The interrupt mechanism allows the CPU to do operations without periodically poll a device. It is now the external device that, when in need to communicate with the CPU, will send a signal to gain attention.

This signal is known as interrupt.

Figure 3.3: CPU activity allocation when each event is accompanied by an interrupt [4]

Usually CPUs will have one or more pins that can be triggered from the peripherals. There can be many ways to assert a pin, some via software, some via hardware.

For example, hardware triggers can be level-triggered or edge-triggered. An interrupt level-triggered is generated when the value read on the pin corresponds to a set value. An interrupt edge-triggered is started when the line changes logical state. An example of this is the timer interrupt. As the documentation says "A 16-bit timer has the ability to generate an interrupt on a period match or falling edge of the external gate signal, depending on the operating mode" [11].

Interrupts can also be software generated, meaning that is the execution of the code itself that triggers one. These can include both programmed ones, and ones not raised explicitly. In this second subcategory fall all traps, which can be considered error triggered interrupts. They will be better described later.

The signal conveyed by these pins is called Interrupt ReQuest (IRQ), and consequently these pins are often referred to as IRQ pins.

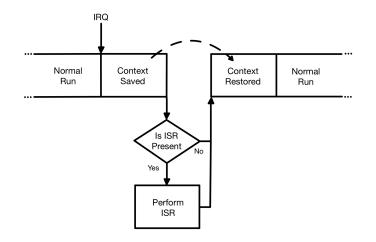

After the IRQ is detected, the program checks whether to that IRQ there's a Interrupt Service Routine (ISR) associated, which is a special block of code. If present, it is run by the CPU when it wants to serve the interrupt request raised by a peripheral, effectively momentarily blocking the normal run of the firmware.

The basic idea of interrupt work is divided in 4 steps:

- 1. CPU completes the current instruction

- 2. Context is saved

- 3. Execution of the ISR, if provided

- 4. Context is restored

Figure 3.4: Interrupt block scheme

We can now see how the PIC24 implements these steps.

#### **PIC24 Interrupts Management**

To manage interrupts, PIC24 uses its registers. Three very important categories are: the IFSx (Interrupt Flag Status), the IECx (Interrupt Enable Control), and the IPCx (Interrupt Priority Control) registers, where x denotes the register number.

Each source of interrupt has an enable bit (one bit of IECx) which, as the name suggests, enables the associated interrupt. The status bit (one bit of IFSx) is set by the corresponding peripheral when the pin is correctly triggered, and must be cleared via software.

All interrupt event flags are checked at each instruction cycle, and if both these bits are set, then the IRQ will cause an interrupt to occur.

The CPU starts now to handle the interrupt received. As confirmed by the documentation, "No instruction will be aborted when the CPU responds to the IRQ." [10]. The instruction will be completed, and the context will be saved. In particular the following information is saved on the software stack:

- the current PC value

- the low byte of the processor ALU STATUS register

- current CPU priority level: the IPL3 status bit (CORCON<3>)

With these information the program is able to correctly return to its previous state at the end of the ISR.

Some questions arise naturally: how does the CPU recognize which peripheral raised the interrupt, and how are simultaneous requests from different peripherals or interrupt request that occur during the ISR of another peripheral handled. Lets see how the PIC24 tackles these problems.

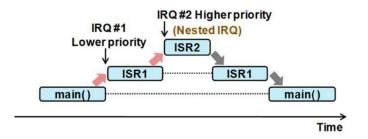

**Priority and Nesting** To handle multiple interrupt requests the concept of priority and nesting are introduced. To each IRQ is associated a priority level. In PIC24 the CPU operates in one of sixteen priority levels, 0-15. To be served, an interrupt or trap must have priority level greater than the CPU current one, so an IRQ with priority level set to 0 is disabled. The CPU priority level is saved in the IPL3 status bit (CORCON<3>), and is set to the value of the ISR currently being served. Priority levels 8-15 are reserved for trap sources, which are interrupts dedicated to safety, and will be later introduced. So peripherals can be programmed on priority levels 0-7.

If two interrupts arrive at the same time, the one with higher priority level is served before. A ISR begin serves is said to be active.

Similarly, if an ISR is active, but an interrupt of higher priority arrives, then context is saved and the new one is served. When the new ISR has been served, then the CPU returns to the previous context, completing the lower priority level interrupt. This is called nesting.