# ROBUSTNESS OF MONOCHROMATIC LED MODULES TOWARDS ELECTROSTATIC DISCHARGE EVENTS

July 3, 2013

# Contents

| 1 | CA  | RRIEI          | RS RECOMBINATION                                                           | 6  |

|---|-----|----------------|----------------------------------------------------------------------------|----|

|   | 1.1 | RADI<br>1.1.1  | ATIVE RECOMBINATION                                                        |    |

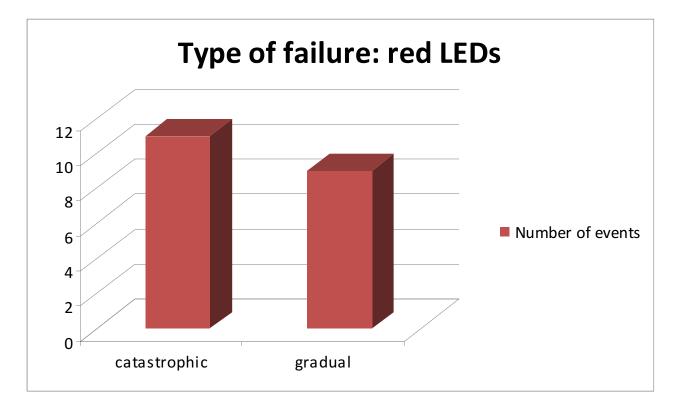

|   |     | 1.1.2          | BIMOLECULAR RECOMBINATION COEFFICIENT ESTIMATION .                         | 14 |

|   | 1.2 | NON-           | RADIATIVE RECOMBINATION                                                    | 14 |

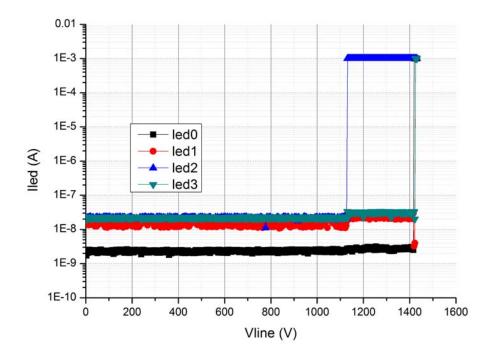

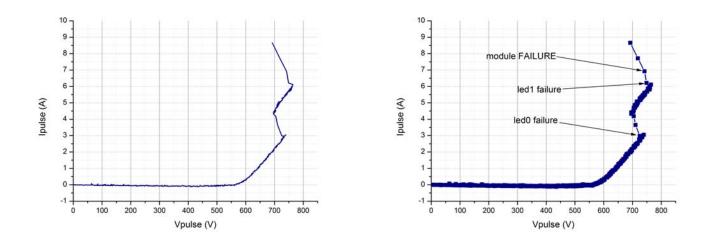

|   |     | 1.2.1          | SHOCKLEY-HALL-READ RECOMBINATION                                           | 16 |

|   |     |                | 1.2.1.1 Excess-Carrier Lifetime                                            | 19 |

|   |     | 1.2.2<br>1.2.3 | AUGER RECOMBINATION                                                        |    |

|   | 1.3 | QUAN           | NTUM EFFICIENCY                                                            | 23 |

| 2 | LEI | ) DEV          | TCES                                                                       | 25 |

|   | 2.1 | LED I          | ELECTRICAL PROPERTIES                                                      | 25 |

|   |     | 2.1.1          | HOMOJUNCTION STRUCTURE AND ELECTRICAL MODEL                                | 25 |

|   |     | 2.1.2          | HETEROJUNCTION STRUCTURE                                                   | 27 |

|   |     | 2.1.3          | QUANTUM WELL                                                               | 28 |

|   |     |                | 2.1.3.1 THE INFINITE SQUARE-SHAPED QUANTUM WELL                            | 28 |

|   |     |                | 2.1.3.2 THE ASYMMETRIC AND SYMMETRIC FINITE SQUARE-<br>SHAPED QUANTUM WELL | 31 |

|   |     | 2.1.4  | OTHER NONIDEALITIES AND CHARACTERISTICS                        | 35 |

|---|-----|--------|----------------------------------------------------------------|----|

|   | 2.2 | LED (  | OPTICAL PROPERTIES                                             | 39 |

|   |     | 2.2.1  | EFFICIENCY                                                     | 39 |

|   |     | 2.2.2  | SPECTRAL CHARACTERISTICS                                       | 40 |

|   |     | 2.2.3  | LIGHT EXTRACTION AND GENERAL EFFICIENCY IMPROVEMENT TECHNIQUES | 44 |

|   |     | 2.2.4  | L-I CHARACTERISTIC                                             | 48 |

| 3 | ELI | ECTRO  | DSTATIC DISCHARGE                                              | 50 |

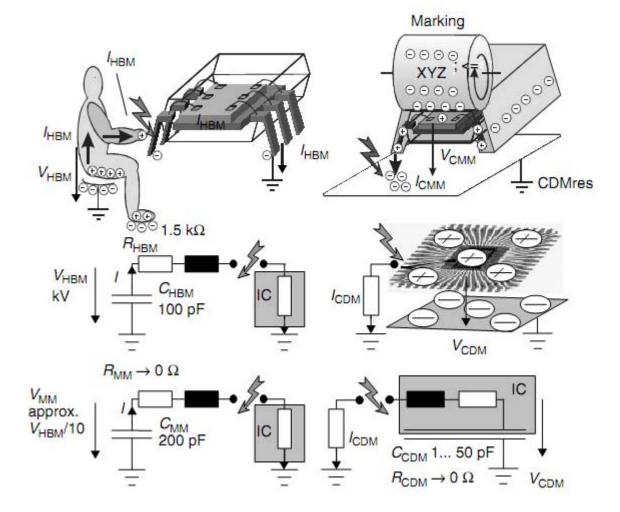

|   | 3.1 | ESD (  | GENERATION MECHANISMS                                          | 50 |

|   |     | 3.1.1  | LOCAL CHARGE GENERATION MECHANISMS                             | 51 |

|   | 3.2 | ESD S  | STRESS MODELS                                                  | 53 |

|   | 3.3 | ESD S  | STRESS METHODS                                                 | 55 |

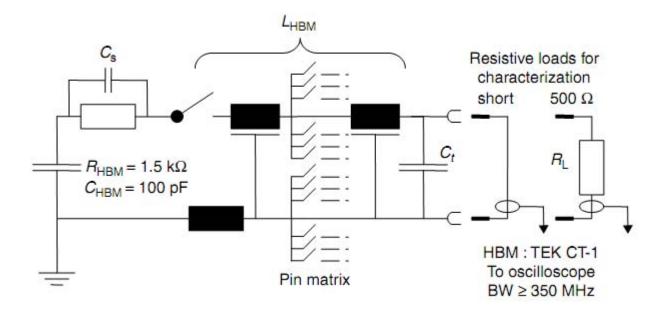

|   |     | 3.3.1  | HUMAN BODY MODEL (HBM)                                         | 56 |

|   |     |        | 3.3.1.1 TEST PROCEDURE                                         | 59 |

|   |     | 3.3.2  | MACHINE MODEL (MM)                                             | 60 |

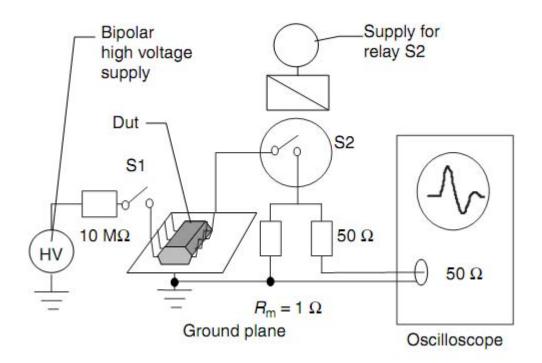

|   |     | 3.3.3  | CHARGED DEVICE MODEL (CDM)                                     | 61 |

|   |     |        | 3.3.3.1 TEST PROCEDURE                                         | 62 |

|   |     | 3.3.4  | OTHER STRESS MODELS                                            | 65 |

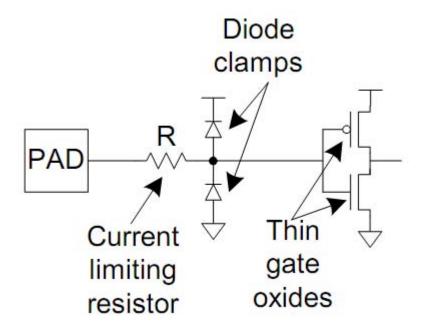

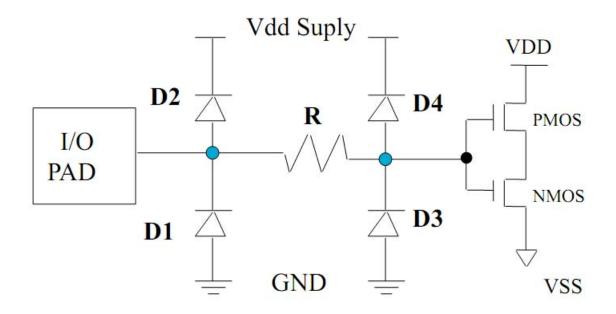

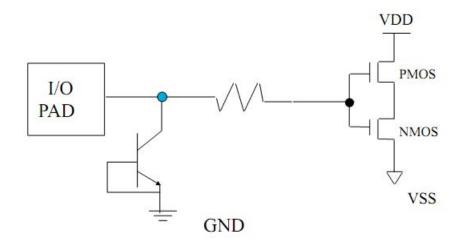

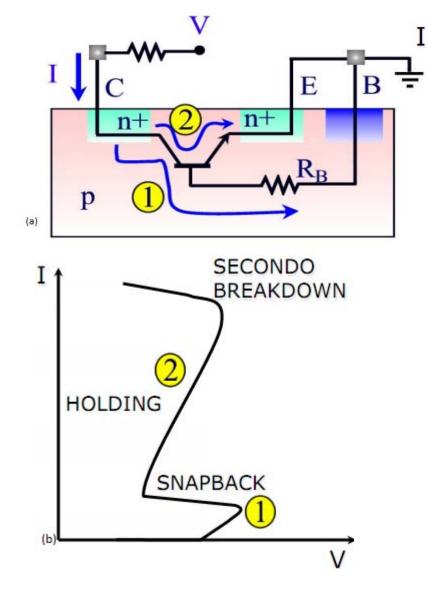

|   | 3.4 | DEVI   | CES PROTECTION STRATEGIES                                      | 65 |

|   |     | 3.4.1  | ESD CONTROL METHODS                                            | 65 |

|   |     | 3.4.2  | ESD PROTECTION DEVICES                                         | 66 |

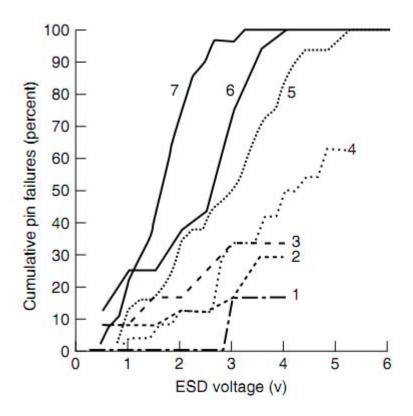

| 4 | ESI | O ON I | LED DEVICES                                                    | 72 |

|   | 4.1 | PREV   | TIOUS WORKS ON ESD EFFECTS ON LED DEVICES                      | 72 |

|   | 4.2 | CONC   | CLUSIONS                                                       | 86 |

| <b>5</b> | MEASUREMENT SETUP AND EXPERIMENTAL DETAILS |                                         |                                                                              |                   |  |  |  |  |

|----------|--------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------|-------------------|--|--|--|--|

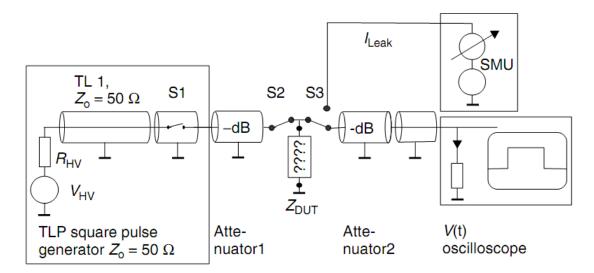

|          | 5.1                                        | TRANSMISSION LINE PULSE (TLP) TECHNIQUE |                                                                              |                   |  |  |  |  |

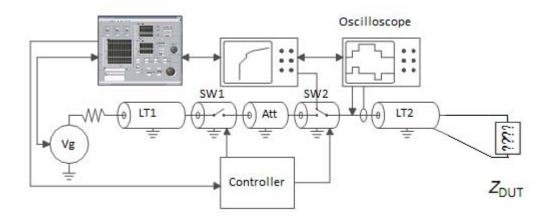

|          |                                            | 5.1.1                                   | FUNDAMENTALS AND IMPLEMENTATIONS                                             | 87                |  |  |  |  |

|          |                                            | 5.1.2                                   | CURRENT SOURCE TLP                                                           | 89                |  |  |  |  |

|          |                                            | 5.1.3                                   | TIME-DOMAIN REFLECTOMETER TLP (TDR-TLP)                                      | 90                |  |  |  |  |

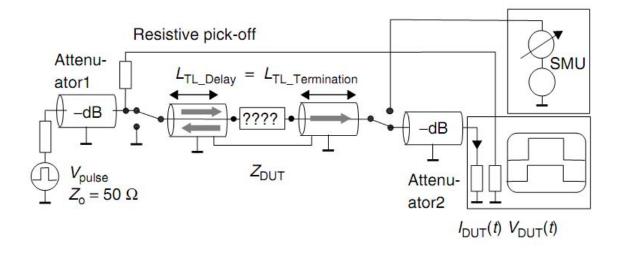

|          |                                            | 5.1.4                                   | TIME DOMAIN TRANSMISSION TLP (TDT-TLP)                                       | 91                |  |  |  |  |

|          |                                            | 5.1.5                                   | TIME-DOMAIN TRANSMISSION REFLECTOMETER TLP (TDTR-<br>TLP)                    | 92                |  |  |  |  |

|          |                                            | 5.1.6                                   | FINAL CONSIDERATIONS ON TLP STRESS-SYSTEMS STANDARD-IZATION AND OPTIMIZATION | 93                |  |  |  |  |

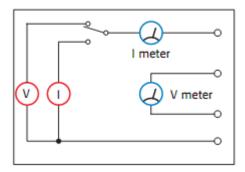

|          | 5.2                                        | MEASUREMENT SETUP                       |                                                                              |                   |  |  |  |  |

|          |                                            | 5.2.1                                   | STANFORD RESEARCH SYSTEMS PS350/5000V HIGH VOLTAGE GENERATOR                 | 94                |  |  |  |  |

|          |                                            | 5.2.2                                   | TEXTRONIK TDS680B OSCILLOSCOPE                                               | 95                |  |  |  |  |

|          |                                            | 5.2.3                                   | KEITHLEY 2612 SOURCE METER                                                   | 95                |  |  |  |  |

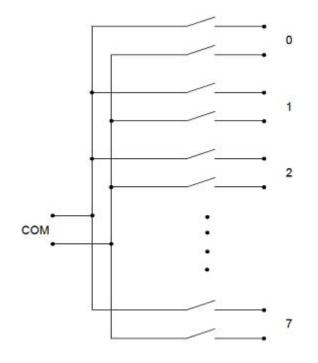

|          |                                            |                                         | 5.2.3.1 HP 3488A SWITCH/CONTROL UNIT                                         | 97                |  |  |  |  |

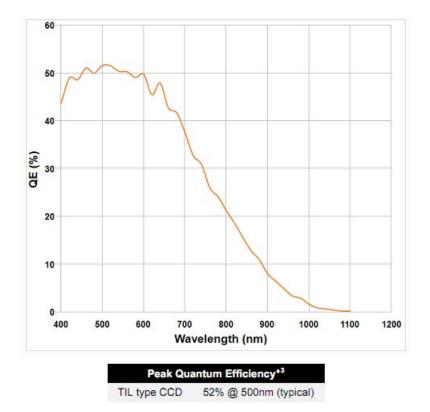

|          |                                            | 5.2.4                                   | ANDOR LUCA                                                                   | 97                |  |  |  |  |

|          |                                            | 5.2.5                                   | OPTIKAM PRO3                                                                 | 99                |  |  |  |  |

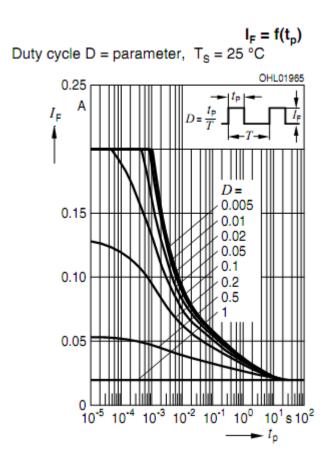

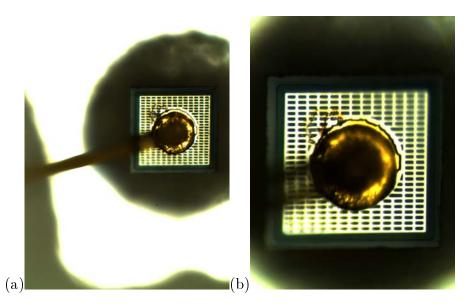

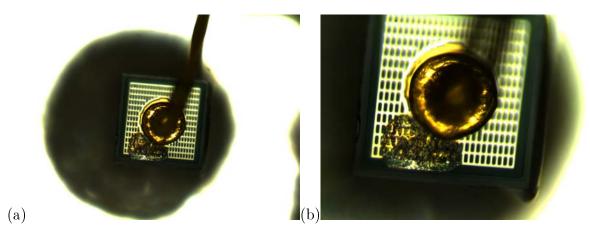

|          | 5.3                                        | .3 ANALYZED DEVICES                     |                                                                              |                   |  |  |  |  |

| 6        | SIN                                        | GLE I                                   | LEDs ANALYSIS                                                                | 105               |  |  |  |  |

|          | 6.1                                        | 1 BLUE SAMPLES                          |                                                                              |                   |  |  |  |  |

|          | 6.2                                        | GREEN SAMPLES 10                        |                                                                              |                   |  |  |  |  |

|          | 6.3                                        | RED SAMPLES 1                           |                                                                              |                   |  |  |  |  |

|          | 6.4                                        | FINA                                    | L CONSIDERATIONS                                                             | 114               |  |  |  |  |

| 7        | SIN                                        | GLE I                                   | LEDS OPTICAL AND ELECTRICAL ANALYSIS                                         | 116               |  |  |  |  |

|          | 7.1                                        | BLUE<br>7.1.1                           | LEDs TESTING       POSITIVE BIAS ESD PULSES                                  | $\frac{116}{116}$ |  |  |  |  |

|          |                                            | 7.1.2                                   | NEGATIVE BIAS ESD-STRESS TESTS                                               | 119               |  |  |  |  |

|          | 7.2                                        | GREE                                    | N LEDs TESTING                                                               | 126               |  |  |  |  |

#### CONTENTS

|   |                   | 7.2.1         | POSITIVE BIAS ESD PULSES       | 127        |

|---|-------------------|---------------|--------------------------------|------------|

|   |                   | 7.2.2         | NEGATIVE BIAS ESD-STRESS TESTS | 128        |

|   | 7.3               | RED I         | LEDs TESTING                   | 138        |

|   |                   | 7.3.1         | POSITIVE BIAS ESD PULSES       | 138        |

|   |                   | 7.3.2         | NEGATIVE BIAS ESD-STRESS TESTS | 139        |

|   |                   |               |                                |            |

| 8 | LEI               | ) MOI         | DULES ANALYSIS                 | 147        |

| 8 | <b>LEI</b><br>8.1 |               | DULES ANALYSIS                 |            |

| 8 |                   | GREE          |                                | 147        |

| 8 | 8.1               | GREE<br>RED I | N LED MODULES ANALYSIS         | 147<br>158 |

# Preface

## ABSTRACT

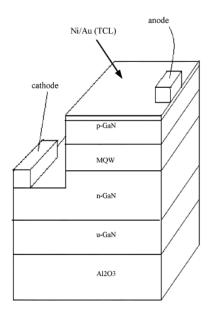

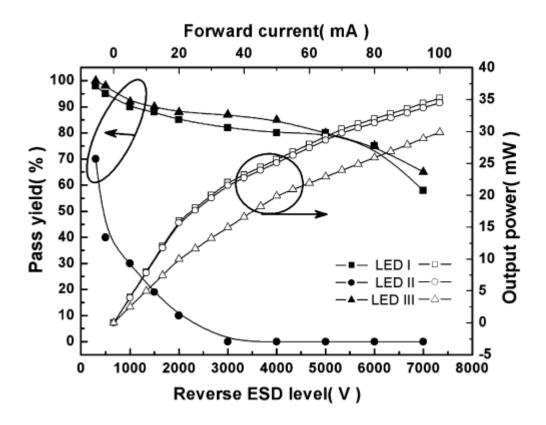

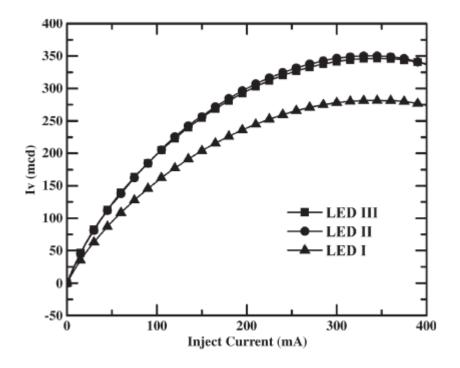

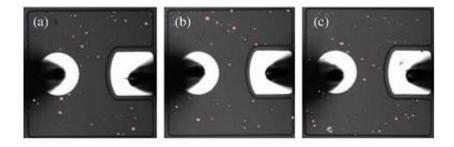

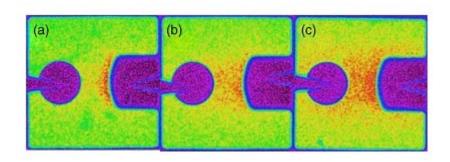

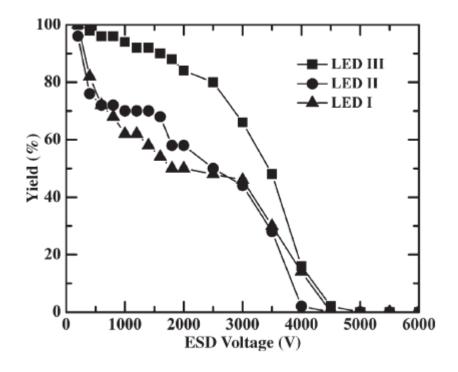

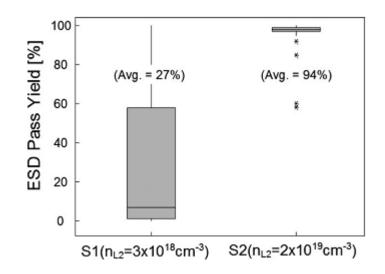

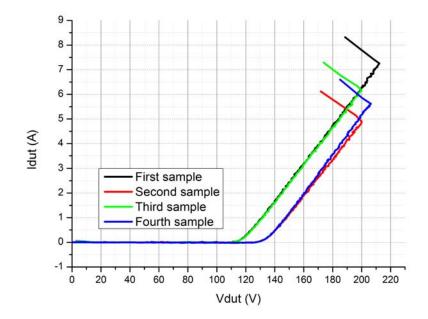

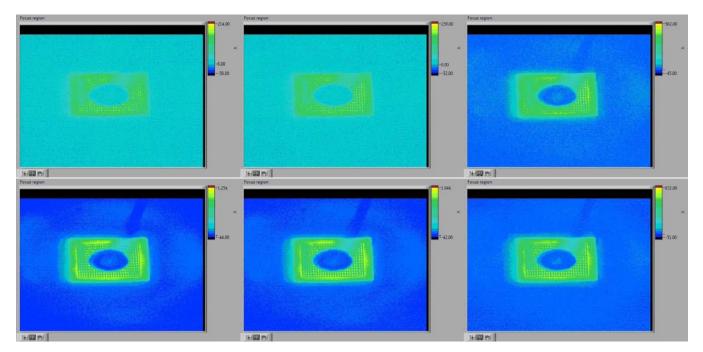

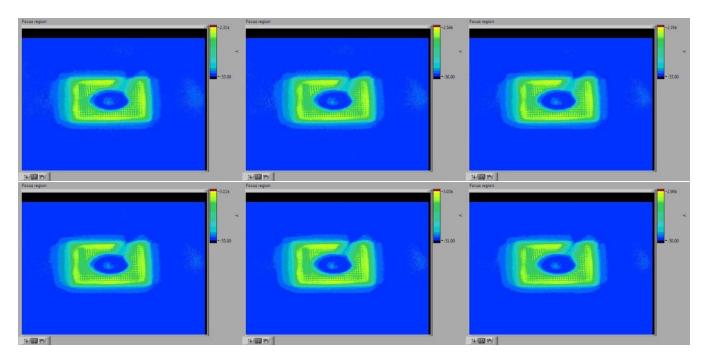

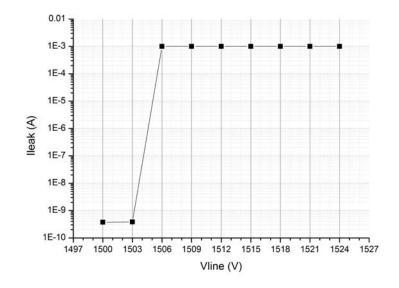

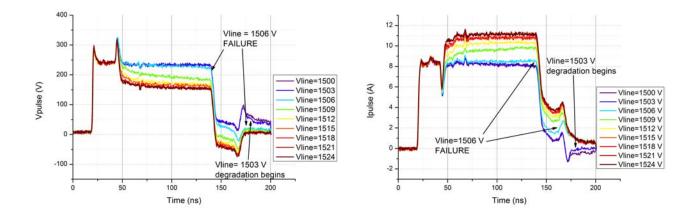

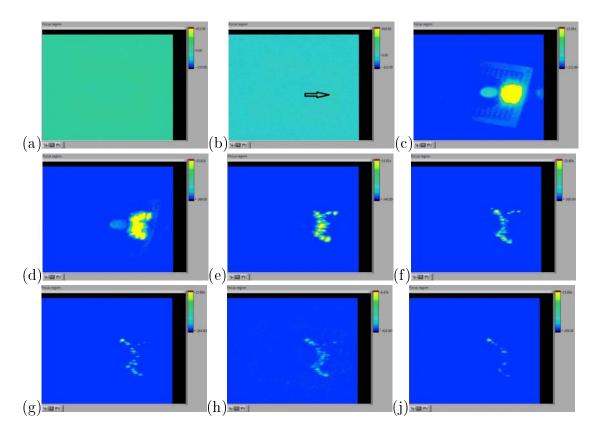

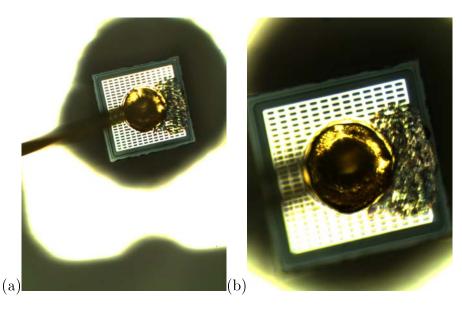

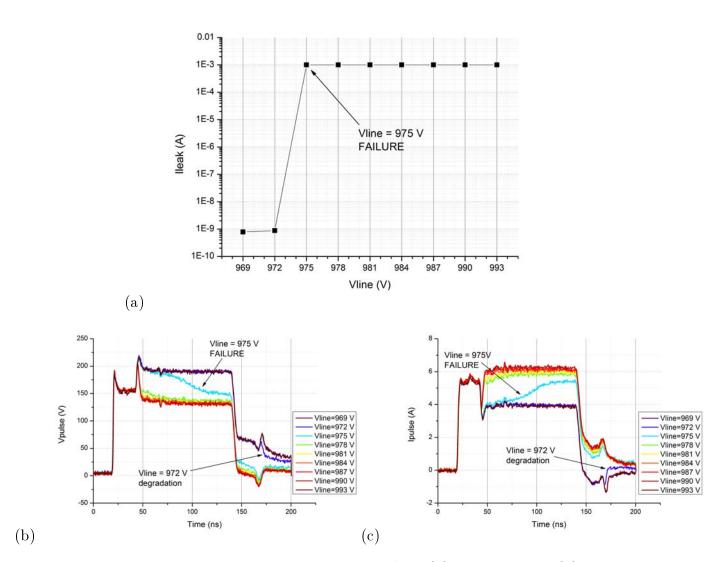

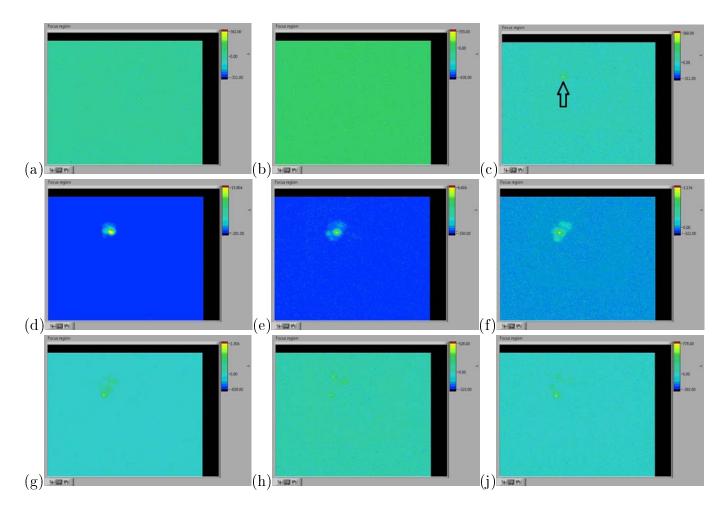

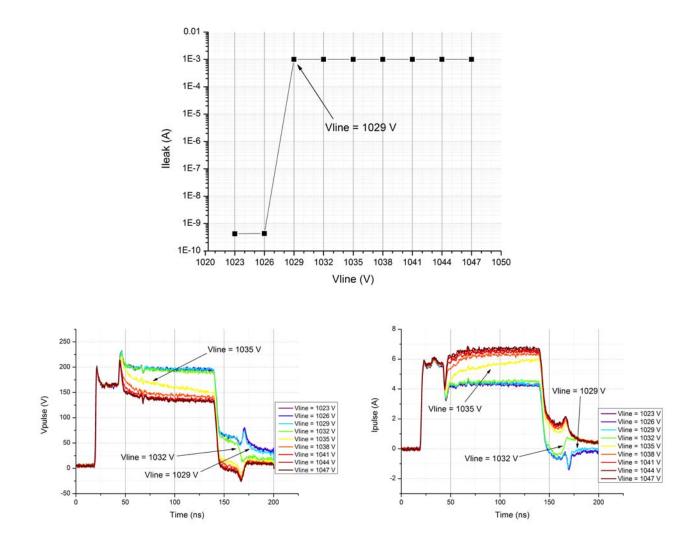

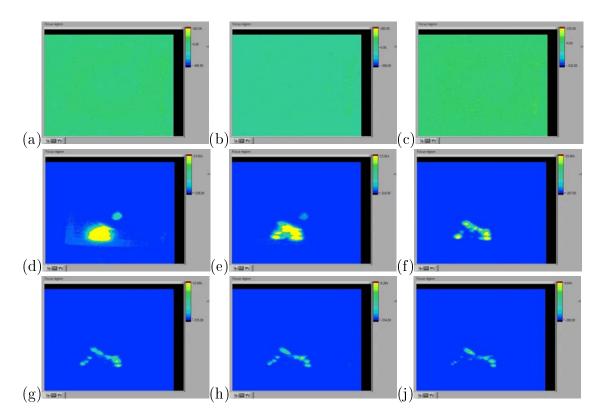

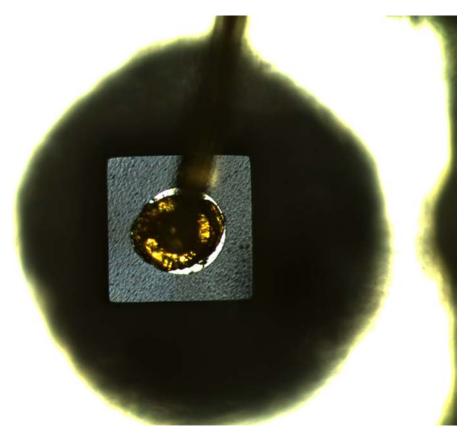

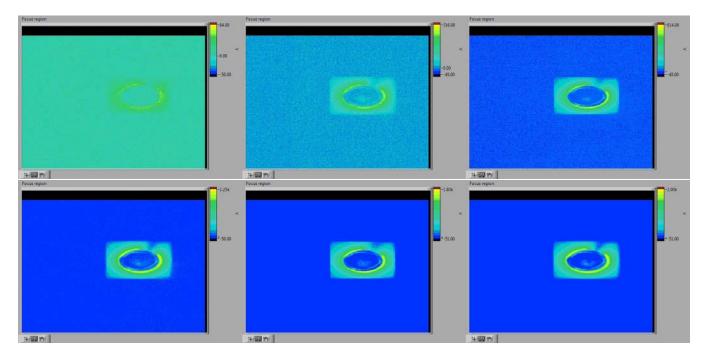

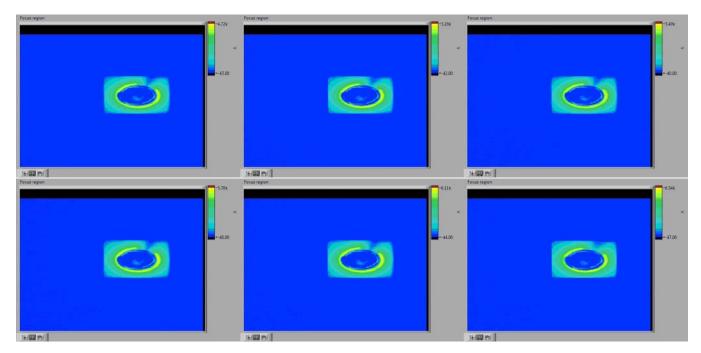

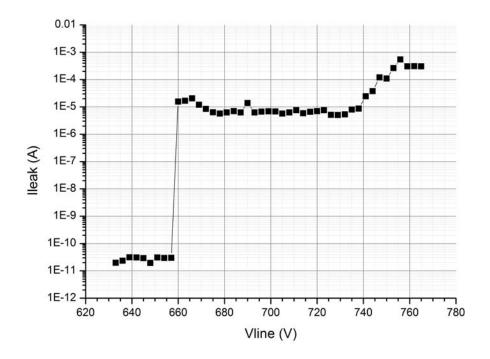

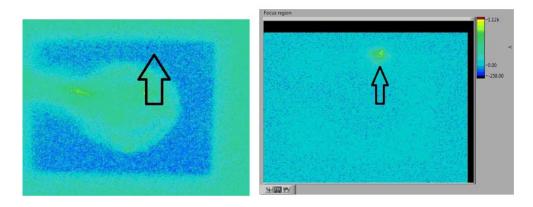

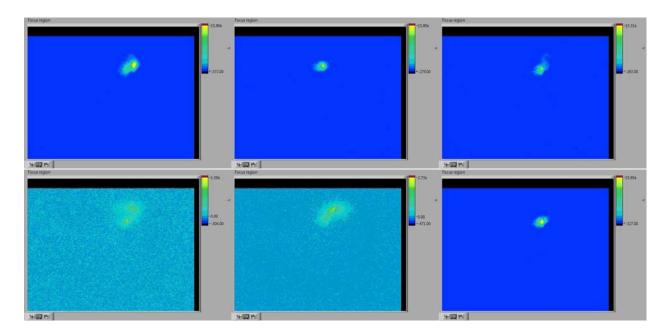

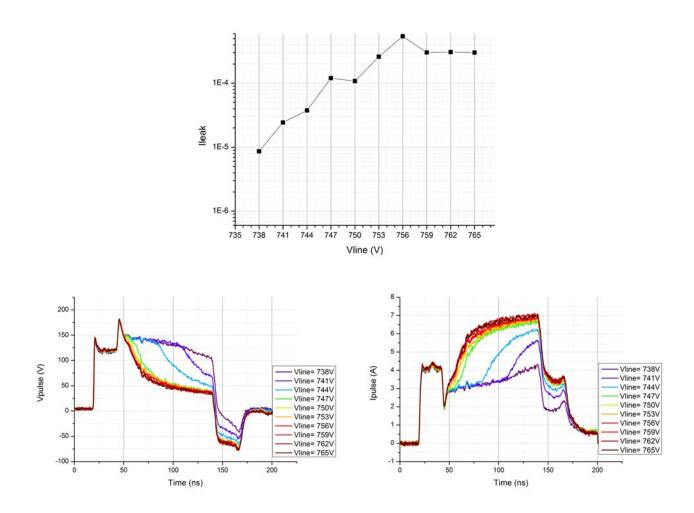

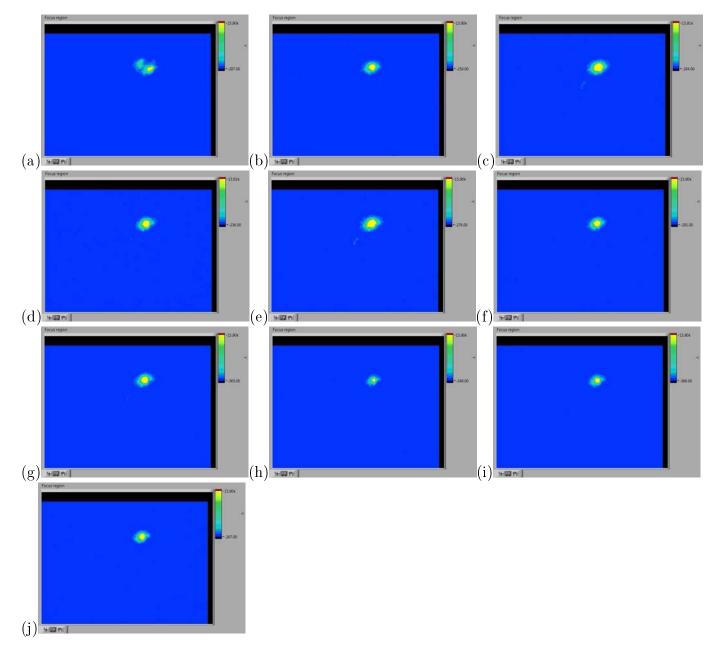

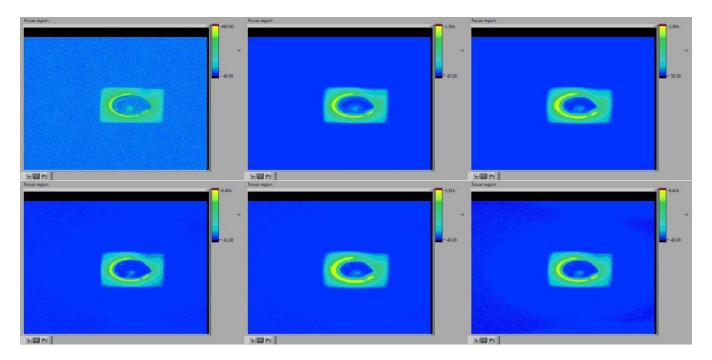

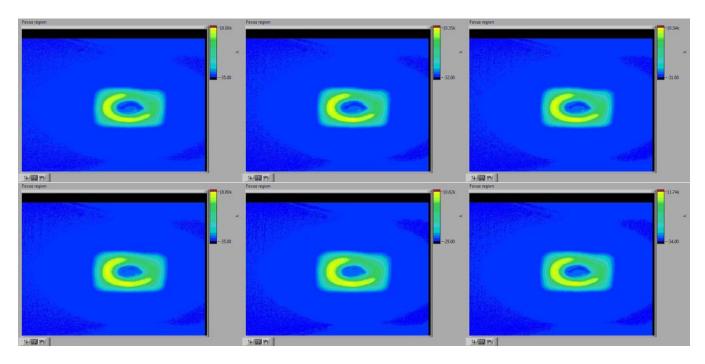

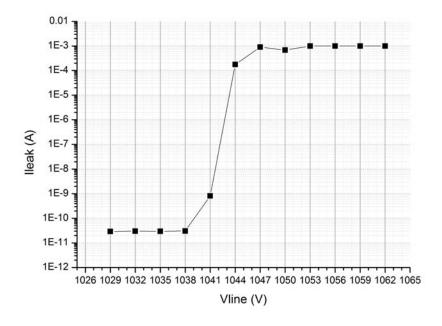

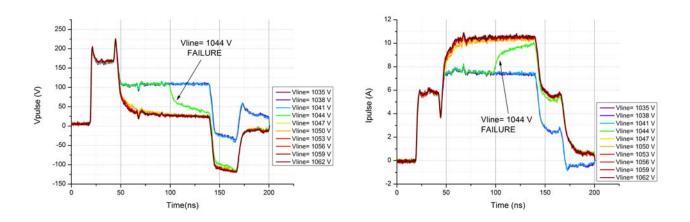

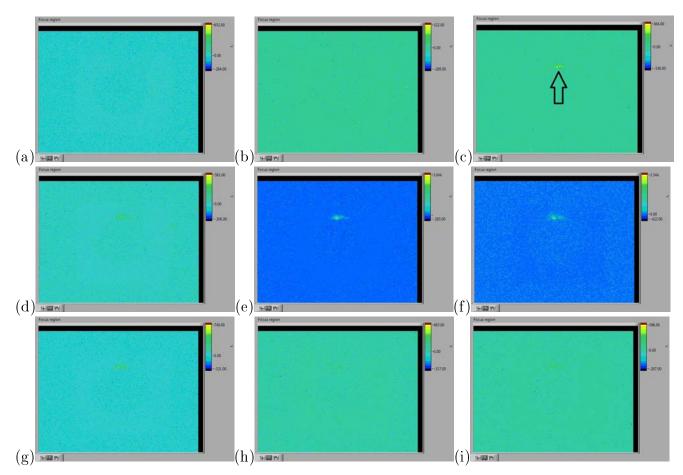

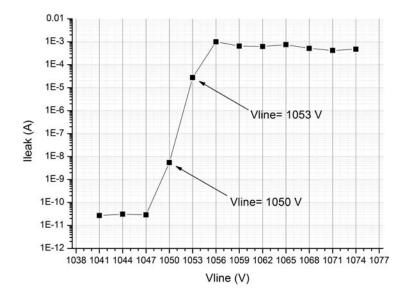

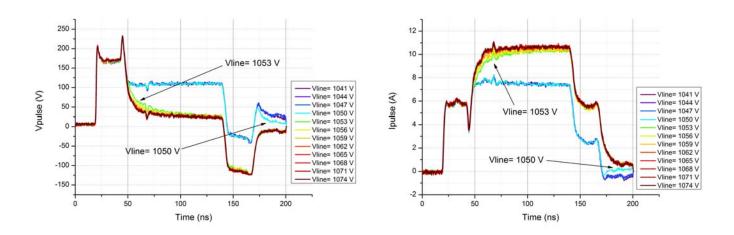

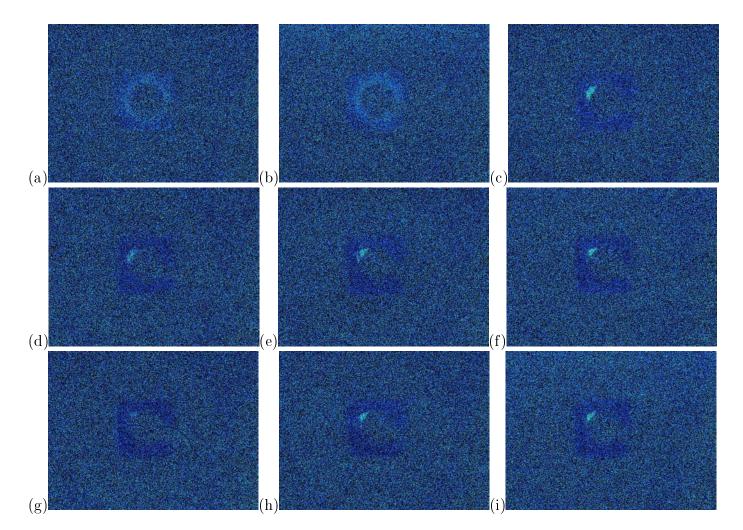

This work was aimed at investigating the robustness of LEDs and LED modules towards ESD events, exploiting a Transmission-Line-Pulser(TLP) system to apply negative bias ESD pulses to the devices. Three different types of LEDs (green, blue and red) were considered. In the first part of the work the devices were tested singularly, both with and without the use of an EMCCD camera to detect light emission during the ESD pulses. After that, monochromatic modules were tested. An analysis of the type of failure of the single LEDs was also carried on. The results showed that the different types of devices have a different behaviour both individually and connected in series. The waveforms analysis during the TLP test allow to identify the electrical degradation of the devices, while the camera images showed the chip areas where the discharge current is concentrated.

# INTRODUCTION

Electrostatic discharges are a very important problem for electronic devices, in fact they can generate unexpected failures everywhere from the production chain to the field. Understanding the robustness of electronic devices towards these events is therefore fundamental. In particular, since LED devices are on the verge of gaining a main role in lighting applications market, it can be interesting to analyze LED module robustness. It is also something that has not been done yet.

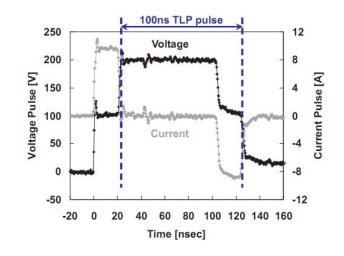

In this thesis work the devices, both singularly and in modules, were tested by using a Transmission Line Pulser. In this system the distributed capacitance of a transmission line is charged using a high voltage generator. After that, the line is closed on a load through a switch and consequently discharges, generating a rectangular pulse with a well defined duration, determined by the line length. Since LEDs are more sensitive to reverse-bias stress, just negative pulses were applied.

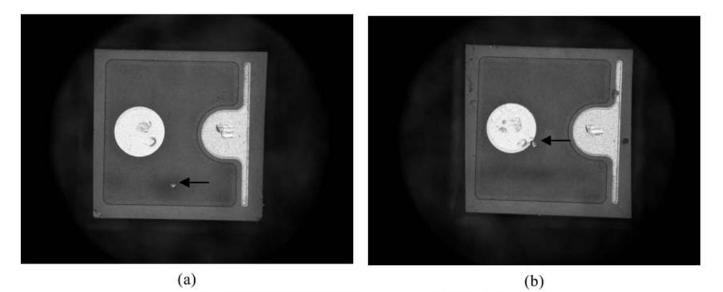

An optical investigation was also carried on in order try to determine whether the ESD pulses gave emission or not, and where this emission was eventually located on the chip.

In the first part of this thesis a brief overview of the optoelectronics and ESDs theoretical principles will be given. The main ESD-stress test systems and models will be also reported. In the second part, the results of the experimental work will be shown and commented.

# Chapter 1 CARRIERS RECOMBINATION

In a semiconductor at thermal equilibrium the concentrations of free carriers obey the law of mass action

$$n_0 p_0 = n_i^2 \tag{1.1}$$

When excess carriers are generated, for example through current injection or light absorption, concentrations are given by

$$n = n_0 + \Delta n \quad p = p_0 + \Delta p \tag{1.2}$$

Excess carriers can recombine in both radiative and non-radiative way.

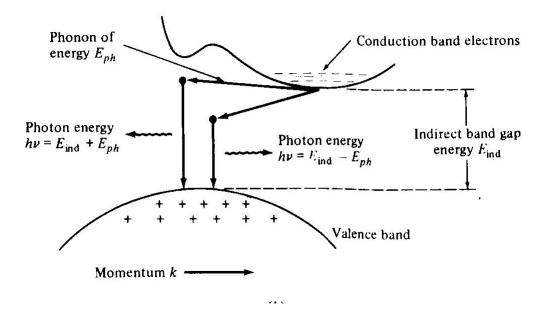

Radiative recombination occurs when an excited electron falls to a lower energy level, recombining with a hole and giving emission of a phonon of energy equal to the one lost by the electron. These direct transitions between the valence band and the conduction band occur in all semiconductors and are the most important generation-recombination mechanisms in many of the compound semiconductors, such as gallium arsenide (GaAs) and indium phosphide (InP), composed of elements from columns III and V of the periodic table. However, in silicon and germanium the details of the crystal structure make direct transitions unlikely except when very high densities of holes and electrons are present. In silicon and germanium in fact, electrons at the lowest energy in the conduction band have nonzero momentum (we say that these materials have indirect energy gap). Because the holes at the valence-band maximum do have zero momentum, a direct transition that conserves it together with energy is impossible without a lattice (phonon) interaction occurring simultaneously. Thus, in silicon or germanium, direct transitions across the forbidden-energy gap require simultaneous interaction of three particles: the electron, the hole and a phonon that represents the lattice interaction. Three particles interactions are far less likely than two-particle interactions, such as those between a free carrier and a phonon, that can take place if there are localized allowed energy states into which electrons or holes can make transitions. In practice, localized states at energies between  $E_C$  and  $E_V$  are always present because of lattice imperfections caused by misplaced atoms or, more usually, because of impurity atoms, thus non-radiative recombination occurs even in direct band gap materials.

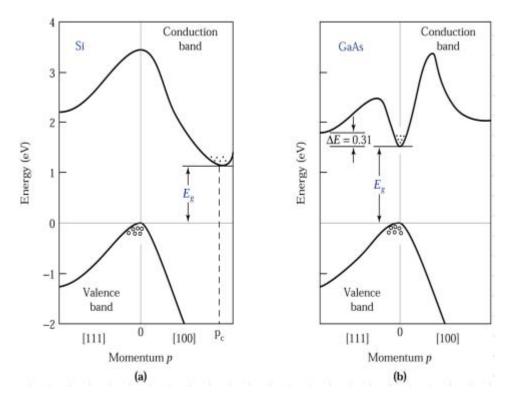

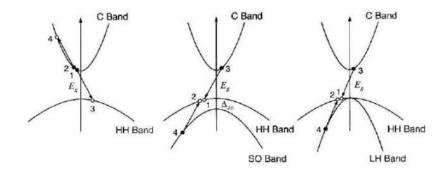

Figure 1.1: Examples of direct (a) and indirect (b) energy gap

These localized states act as stepping stones. In a recombining event, for example an electron falls from the conduction band to a state that we logically call a recombination center, and then it falls further into a vacant state in the valence band, thus recombining with a hole.

In a semiconductor, recombination can occur in both radiative and non radiative way, but in optoelectronic devices non-radiative recombination is an undesired effect that reduces the efficiency, so it should be eliminated. However non-radiative recombination strongly depends on the material quality, and because of the fact that it's impossible to totally eliminate defects and dislocations, it is also not feasible to make this kind of recombination disappear.

## 1.1 RADIATIVE RECOMBINATION

An important thing to notice is that in the recombination process, there must be not only conservation of energy (obtained through the emission of a phonon), but also of the momentum p. This makes radiative recombination much more disadvantaged in semiconductors with an indirect band gap. In fact, while in semiconductors with a direct energy gap the minimum of the conduction and the maximum of the valence band (where the most of the free electrons and holes are distributed) are located at the same value of p, in the other type of semiconductors maximum and minimum of the two bands correspond to different p values. This makes radiative recombination less likely to happen, because it becomes a three bodies process, in fact, in order to recombine with a hole, the electron has to change its momentum through interaction with a phonon (interaction with the crystal lattice).

To analyze radiative recombination in semiconductors, the first step is defining the recombination ratio R. Considering a free electron in the conduction band, the probability that it recombines

Figure 1.2: Example of recombination processes in an indirect energy gap semiconductor.

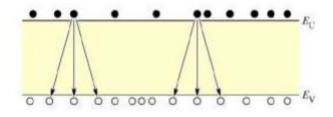

Figure 1.3: Electrons and holes

with a hole is proportional to the holes concentration in the valence band.

$R \propto p$

The number of the total recombination events is proportional to the electrons concentration too

$$R \propto np$$

We can thus define R (the recombination rate per unit volume and time) as

$$R = -\frac{dn}{dt} = -\frac{dp}{dt} = Bnp \tag{1.3}$$

Typical values of B for III-IV compounds are in the order of magnitude of  $10^{-10} \div 10^{-9} cm^{-3} s^{-1}$ .

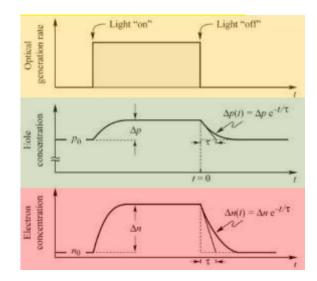

We now consider the recombination dynamics as a function of time for the low-excitation case of a semiconductor exposed to light. Electrons and holes are generated in couples, thus their excess concentrations are equal

$$\Delta n(t)) = \Delta p(t) \tag{1.4}$$

The recombination rate can then be written as

$$R = B \left[ n_0 + \Delta n \left( t \right) \right] \left[ p_0 + \Delta p \left( t \right) \right]$$

(1.5)

For low excitation levels the concentration of the photo-generated carriers is much lower than the majority-carriers concentration,  $\Delta n \ll n_0 + p_0$ , allowing us to neglect the  $\Delta n \Delta p$  term in the recombination rate equation

$$R = B \left[ n_0 p_0 + n_0 \Delta p \left( t \right) + p_0 \Delta n \left( t \right) + \Delta n \left( t \right) \Delta p \left( t \right) \right]$$

(1.6)

$$\approx Bn_i^2 + B\left(n_0 + p_0\right)\Delta n\left(t\right) = R_0 + R_{excess}$$

(1.7)

where  $R_0$  is the recombination rate at the equilibrium and  $R_{excess}$  the recombination rate for excess carriers.

Considering both generation and recombination

$$\frac{dn(t)}{dt} = G - R = (G_0 + G_{excess}) - (R_0 + R_{excess})$$

(1.8)

where  $G_0$  and  $R_0$  are the generation/recombination rate at the equilibrium. Making the hypothesis that the light is turned off at t = 0, because of the fact that  $G_0 = R_0$  for t > 0

$$\frac{d\Delta n\left(t\right)}{dt} = -B\left(n_0 + p_0\right)\Delta n\left(t\right) \tag{1.9}$$

The solution of this differential equation is

$$\Delta n(t) = \Delta n_0 e^{-B(n_0 + p_0)t}$$

(1.10)

with  $\Delta n_0 = \Delta n \ (t = 0)$ . This equation can be written also as

$$\Delta n\left(t\right) = \Delta n_0 e^{-t/\tau} \tag{1.11}$$

We can thus define the carriers recombination time

$$\tau = [B(n_0 + p_0)] \tag{1.12}$$

for extrinsic semiconductors:

Figure 1.4: Excitation level (yellow), holes (green) and electrons (red) concentration in a p-type semiconductor

$$\tau_n = \frac{1}{Bp_0} = \frac{1}{BN_A} \tag{1.13}$$

in the case of p-type materials, and

$$\tau_p = \frac{1}{Bn_0} = \frac{1}{BN_D}$$

(1.14)

for n-type semiconductors.

Inserting these equations in the general case recombination rate formula, we obtain the *monomolec*ular rate equations, valid for p-type material

$$\frac{d}{dt}\Delta n\left(t\right) = -\frac{\Delta n\left(t\right)}{\tau_{n}} \tag{1.15}$$

and n-type semiconductor.

$$\frac{d}{dt}\Delta p\left(t\right) = -\frac{\Delta p\left(t\right)}{\tau_{p}} \tag{1.16}$$

If we consider a high excitation level case, the equations obtained are different. In this situation in fact, the concentration of the photo-generated carriers is much higher than the concentration at the equilibrium,  $\Delta n \gg n_0 + p_0$ , and we can thus write

$$R = -\frac{dn}{dt} = -\frac{dp}{dt} = Bnp \tag{1.17}$$

$$R = B [n_0 + \Delta n (t))] [p_0 + \Delta p (t))]$$

(1.18)

$$R = B [n_0 p_0 + n_0 \Delta p (t) + p_0 \Delta n (t) + \Delta n (t) \Delta p (t)]$$

(1.19)

$$\approx B\Delta n(t) \Delta p(t) = B\Delta n(t) \Delta n(t)$$

(1.20)

Thus, for high injection levels, the bimolecular recombination equation becomes

$$\frac{d}{dt}\Delta n\left(t\right) = G - R = -B\Delta n^2 \tag{1.21}$$

In this case we have a non-exponential solution

$$\Delta n\left(t\right) = \frac{1}{Bt + \Delta n_0^{-1}} \tag{1.22}$$

with  $\Delta n_0 = \Delta n(0)$ .

In exponential processes the time-constant is calculated through the following equation

$$\tau(t) = -\frac{\Delta n(t)}{\frac{d\Delta n(t)}{dt}}$$

(1.23)

Applying this formula to the high injection level case, we obtain

$$\tau\left(t\right) = t + \frac{1}{B\Delta n_0}\tag{1.24}$$

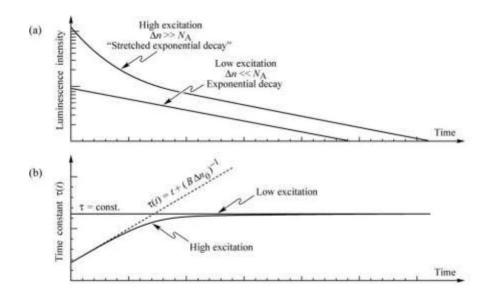

In this case the time constant depends on time itself, in fact the lifetime of minority carriers increases through time, reaching in the end the low excitation value, when the decrease of carriers brings the system in a low-excitation situation.

The decrease in the carriers concentration can be measured evaluating the luminescence decay after a short excitation pulse, in fact the luminescence intensity is proportional to the recombination rate R.

Radiative recombination dynamics are very important in optoelectronic devices, for example they have a strong influence on LEDs turn-on and turn-off time. In fact recombination time is for example the parameter that limits the modulation speed of LEDs in telecommunications applications. There are two different ways to make minority carriers recombination time decrease:

- high doping in the active region

-injecting high concentrations of carriers into the active region

In practice heterojunctions are often use to confine carriers in very small regions, thus obtaining high carriers concentrations and low lifetimes.

Figure 1.5: (a) Luminescence decay for low and high excitation densities. (b) Time constants for low and high excitation densities.

Figure 1.6: Phonon absorption parameters

#### 1.1.1 VAN ROOSBROEK-SHOCKLEY MODEL

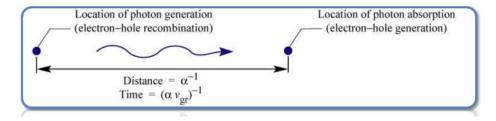

This model allows to calculate the spontaneous recombination rate both at equilibrium or not, needing the knowledge of a very limited set of parameters: the energy gap, the absorption coefficient  $\alpha$  and the refractive index  $\eta$ . We can calculate the time needed for the absorption of a phonon as

$$\tau\left(\nu\right) = \frac{1}{\alpha\left(\nu\right)v_{gr}}\tag{1.25}$$

$V_{gr}$  is the phonon velocity and  $\frac{1}{\alpha(\nu)}$  (*cm*) the average distance traveled by a phonon at frequency  $\nu$  before being absorbed.

Using the following equations

,

$$v_{gr} = \frac{d\omega}{dk} = \frac{d\nu}{d\left(1/\lambda\right)} = c\frac{d\nu}{d(n\nu)}$$

(1.26)

$$k = \frac{2\pi}{\lambda}, \, \omega = 2\pi\nu, \, \lambda = \frac{\lambda_0}{n}, \, \frac{c}{n} = \lambda\nu, \, \frac{1}{\lambda} = \frac{n\nu}{c}$$

(1.27)

where k is the wave vector  $(2\pi n, n$  the number of oscillations of the wave in the space unit  $\frac{1}{\lambda}$ ), we can write the phonon absorption probability per unit time as

$$\frac{1}{\tau(\nu)} = \alpha(\nu) v_{gr} = \alpha(\nu) c \frac{d\nu}{d(n\nu)}$$

(1.28)

Multiplying the phonon absorption probability by the phonon density we get the phonon absorption rate per unit time. At the equilibrium the phonon density per unit volume, is given by Planck's black body radiation formula

$$N(\nu) d\nu = \frac{8\pi}{\lambda^4} \frac{1}{e^{h\nu/kT} - 1} d\lambda$$

(1.29)

Exploiting the relation  $\lambda = \frac{c}{n\nu}$ , we can write

$$d\lambda = -\frac{c}{(n\nu)^2} \frac{d(n\nu)}{d\nu} d\nu$$

(1.30)

and substituting this equation in the previous formula, we find the phonon distribution as a function of frequency

$$N(\nu) d\nu = \frac{8\pi\nu^2 n^2}{c^3} \frac{d(n\nu)}{d\nu} \frac{1}{e^{h\nu/kT} - 1} d\nu$$

(1.31)

The absorption rate per unit volume in the frequency interval  $(\nu; \nu + d\nu)$  is given by the ratio between he phonon density and the average phonon lifetime

$$R_{0}(\nu) = \frac{N(\nu)}{\tau(\nu)} = \frac{8\pi\nu^{2}n^{2}}{c^{3}}\frac{d(n\nu)}{d\nu}\frac{1}{e^{h\nu/kT} - 1}d\nu\alpha(\nu)c\frac{d\nu}{d(n\nu)}$$

(1.32)

Integrating with respect to  $\nu$ , we obtain the absorption rate per unit volume, given by the so called *Van Roosbroeck-Shockley equation*

$$R_0 = \int_0^\infty \frac{8\pi\nu^2 n^2}{c^2} \frac{\alpha(\nu)}{e^{h\nu/kT} - 1} d\nu$$

(1.33)

This equation can be simplified writing the absorption coefficient as

$$\alpha = \alpha_0 \sqrt{\left(E - E_g\right) / E_g} \tag{1.34}$$

the absorption coefficient is proportional to the densities of states, that has a quadratic dependence on energy ( $\alpha_0$  is the absorption coefficient at the energy  $h\nu = 2E_g$ ). We can also neglect the dependence of the refractive index on the frequency, obtaining the simplified form of the Van Roosbroeck-Shockley equation

$$R_0 = 8\pi cn^2 \alpha \sqrt{\frac{kT}{E_g}} \left(\frac{kT}{ch}\right)^3 \int_{x_g}^{\infty} \frac{x^2 \sqrt{x - x_g}}{e^x - 1} dx$$

(1.35)

where we have defined the following variables

$$x = \frac{h\nu}{kT} = \frac{E}{kT}, \ x_g = \frac{E_g}{kT}$$

(1.36)

The exponential function increases rapidly with x, this means that just a small interval of energies near the energy gap contributes to the integral.

| Material | E <sub>g</sub> (eV) | α <sub>0</sub> (cm <sup>-1</sup> ) | n   | R <sub>0</sub> (cm <sup>-3</sup> s <sup>-1</sup> ) | n <sub>i</sub> (cm <sup>-3</sup> ) | B (cm <sup>-3</sup> s <sup>-1</sup> ) | τ <sub>spont</sub> (s) |

|----------|---------------------|------------------------------------|-----|----------------------------------------------------|------------------------------------|---------------------------------------|------------------------|

| GaAs     | 1.42                | 2·10 <sup>4</sup>                  | 3.3 | 7.9·10 <sup>-2</sup>                               | 2·10 <sup>6</sup>                  | 2.10-10                               | 5·10 <sup>-9</sup>     |

| GaN      | 3.4                 | 2·10 <sup>5</sup>                  | 2.5 | 8.9.10-30                                          | 2.10.10                            | 2.2.10-10                             | 4.5·10 <sup>-9</sup>   |

| Si       | 1.12                | 1·10 <sup>3</sup>                  | 3.4 | 3.3·10 <sup>6</sup>                                | 1·10 <sup>10</sup>                 | 3.2.10.14                             | 3.10.2                 |

Figure 1.7: Bimolecular recombination coefficients for some materials

## 1.1.2 BIMOLECULAR RECOMBINATION COEFFICIENT ESTIMA-TION

At the equilibrium, generation and recombination rate are equal and we can use the Van Roosbroeck-Shockley model to estimate it. We know that the bimolecular recombination equation (R = Bnp) gives the number of recombination event per unit volume and time. At the equilibrium  $R = R_0 = Bn_i^2$ , the equilibrium bimolecular recombination rate is then given by

$$B = \frac{R_0}{n_i^2} \tag{1.37}$$

## **1.2 NON-RADIATIVE RECOMBINATION**

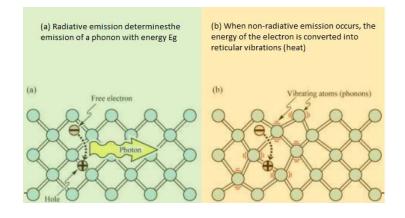

While a radiative event determines the emission of a phonon with an energy equal to the energy gap of the semiconductor, when non-radiative recombination occurs the energy of the electron is transformed into reticular vibration (heat). The presence of defects such as dislocations, impurities and vacancies in the semiconductor structure can be the cause of the generation of energy levels that are localized inside the forbidden-gap thus making non-radiative recombination more likely to happen. These localized states in fact act as "stepping stones" as for example in a recombination event an electron falls from the conduction band to a state that we call a recombination center, and then it falls further into a vacant state in the valence band, thus recombining with a hole.

The recombination through interaction with localized states is described in the so called Shockley-Read-Hall theory.

Figure 1.8: (a) Radiative and (b)non-radiative recombination

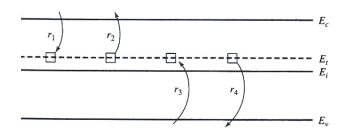

Figure 1.9: Free carriers can interact with localized states by four processes:  $r_1$  electron capture,  $r_2$  electron emission,  $r_3$  hole capture, and  $r_4$  hole emission. The localized state shown shown is acceptor type and at energy  $E_t$  within the forbidden energy gap.

#### 1.2.1 SHOCKLEY-HALL-READ RECOMBINATION

In the following picture we can see the four processes through which free carriers can interact with localized states

The illustration shows a density  $N_t$  of states at an energy  $E_t$  within the forbidden gap. The states shown are acceptor type that is, neutral when empty, negative when full, but the processes described apply also to donor-type states. In the first process, electron capture, an electron falls from the conduction band into an empty localized state. The rate at which the process occurs is proportional to the density of electrons in the conduction band, the density of empty localized states and the probability that an electron passes near a state and is captured by it. The density of empty localized state is given by the total density  $N_t$ , times one minus the probability f(Et) that they are occupied. When thermal equilibrium applies, f is just  $f_D$ , the Fermi function

$$f_D(E) = \frac{1}{1 + \exp\left[\left(E - E_f\right)/kT\right]}$$

(1.38)

The probability per unit time that an electron is captured by a localized state is given by the product of the electron thermal velocity  $v_{th}$  and a parameter  $\sigma_n$  called the *capture cross section*, that is generally determined experimentally for a given type of localized space (the product  $v_{th}\sigma$  can be visualized as the volume swept per unit time by a particle with cross section  $\sigma_n$ ). We can then write the total rate of capture of electrons by the localized states as

$$r_{1} = n \{ N_{t} [1 - f(E_{t})] \} v_{th} \sigma_{n}$$

(1.39)

The second process is the inverse of electron capture: that is, electron emission. The emission of an electron from a localized state into the conduction band occurs at a rate given by the product of the density of states occupied by electrons  $N_t f(E_t)$  times the probability  $e_n$  that the electron makes this jump.

$$r_2 = [N_t f(E_t)] e_n \tag{1.40}$$

The emission probability can be expressed in terms of the quantities already defined in the previous equations by considering the capture and emission rates in the limiting case of thermal equilibrium. At thermal equilibrium the rates of capture and emission of carriers must be equal, thus we can write

$$r_{1} = r_{2} = nN_{t} \left[ 1 - f_{D} \left( E_{t} \right) \right] v_{th} \sigma_{n} = N_{t} f_{D} \left( E_{t} \right) e_{n}$$

(1.41)

and

$$e_n = v_{th}\sigma_n n_i \exp\left(\frac{E_t - E_i}{kT}\right) \tag{1.42}$$

From these equations we can observe that the electron emission from the localized states becomes more probable when its energy is closer to the conduction band because  $E_t - E_i$  is greater. Corresponding relationships describe the interaction between localized states and the valence band. For example, the process of hole capture is proportional to the density of localized states occupied by electrons  $N_t f(E_t)$ , the density of holes and a transition probability. This probability can then be described by the product of the thermal velocity  $v_{th}$  and the capture cross section  $\sigma_p$  of the hole by the localized state. Thus

$$r_3 = [N_t f(E_t)] p v_{th} \sigma_p \tag{1.43}$$

The fourth process, the hole emission, describes the excitation of an electron from the valence band into an empty localized state. By arguments similar to those for electron emission, hole emission is given by

$$e_p = v_{th}\sigma_p n_i \exp\left(\frac{E_i - E_t}{kT}\right) \tag{1.44}$$

Analogously to the electron case, the probability of emission of a hole from a localized state into the valence band becomes much greater as the energy of the state approaches the valence band edge. Observing the equations previously obtained, it's interesting to consider qualitatively the physics that they represent. First we recognize that at thermal equilibrium  $r_1 = r_2$  and  $r_3 = r_4$ . When we have non-equilibrium situation,  $r_1 \neq r_2$  and  $r_3 \neq r_4$ . Imagine that the number of holes in a n-type semiconductor is suddenly increased above its thermal equilibrium value. This causes  $r_3$  to increase. The effect of this is the increase of  $r_4$  and  $r_1$  (both of which eliminate holes at  $E_t$ ). If most of the holes disappear from  $E_t$  via  $r_1$ , they remove electrons from the conduction band, and the localized states are effective recombination centers. If the holes are removed from the level at  $E_t$  predominantly by an increase in  $r_4$ , they return to the valence band, and the sites are effective as hole traps. A given localized state is generally effective in only one way: either as a trap or as a recombination center; if it's closer to a band edge, it is likely to be a carrier trap rather than a recombination center. The equations describing generation and recombination through localized states or recombination centers were originally derived by Shockley, Read and Hall and the process is frequently called the Shockley-Hall-Read recombination. According to the SHR model, when non-equilibrium occurs in a semiconductor, the overall population of electrons and holes in the recombination centers is not greatly affected. The reason for this nearly constant population is that the recombination centers quickly capture majority carriers but have to wait for the arrival of a minority carrier. Thus, the states are nearly always full of carriers, whether under thermal-equilibrium conditions or in non-equilibrium.

To illustrate this behaviour, consider a typical example: acceptor-like recombination centers in an n-type semiconductor. At thermal equilibrium the Fermi level is near  $E_c$  and, therefore, above the energy of the recombination centers. Hence, they are virtually all filled with electrons and  $r_1$  and  $r_2$  are both much greater than  $r_3$  and  $r_4$ . When equilibrium is disturbed by low-level excitation, which increases the number of holes and electrons by the same amount, the electron concentration changes only by a small fraction, while the hole concentration changes by a large fraction. In this case,  $r_1$  has to exceed  $r_2$  by only a very slight amount to accommodate the increased rate of hole capture represented by  $r_3$ . Thus, the population of the localized states remains nearly constant, and the net rate of electron capture  $r_1 - r_2$  equals the net rate of hole capture by the states. These net rates are just the net rate of recombination that we define by symbol U.

$$U = R_{sp} - G_{sp} = r_1 - r_2 = r_3 - r_4 \tag{1.45}$$

where the subscript sp stands for spontaneous, that is, generation and recombination that respond only to deviation from the thermal equilibrium (in contrast to the spontaneous recombination and generation transitions are those caused by stimulation, for example, by a radiative source). Inserting the expression fro  $r_1$  through  $r_4$  into the expression for U, we can eliminate fand obtain

$$U = \frac{N_t v_{th} \sigma_n \sigma_p \left(pn - n_i^2\right)}{\sigma_p \left[p + n_i \exp\left(\frac{E_i - E_t}{kT}\right)\right] + \sigma_n \left[n + n_i \exp\left(\frac{E_t - E_i}{kT}\right)\right]}$$

(1.46)

$$=\frac{(pn-n_i^2)}{\tau_{no}\left[p+n_i\exp\left(\frac{E_i-E_t}{kT}\right)\right]+\tau_{po}\left[n+n_i\exp\left(\frac{E_t-E_i}{kT}\right)\right]}$$

(1.47)

where  $\tau_{no} = (N_t v_{th} \sigma_n)^{-1}$  and  $\tau_{po} = (N_t v_{th} \sigma_p)^{-1}$ .

From these expressions we can observe that U is positive and there is net recombination if the pn product exceeds  $n_i^2$ . The sign changes and there is net generation if the pn product is less than  $n_i^2$ .

The dependence of U on the energy level of the recombination centers can be more easily grasped by considering the case of equal electron and hole capture cross sections. For  $\sigma_p = \sigma_n \equiv \sigma_0$ , we can define  $\tau_0 \equiv (N_t v_{th} \sigma_0)^{-1}$  and, therefore,

$$U = \frac{(pn - n_i^2)}{\left[p + n + 2n_i \cosh\left(\frac{E_t - E_i}{kT}\right)\right] \tau_0}$$

(1.48)

The dependence on the energy level of the recombination center is contained in the hyperbolic cosine term, that is symmetric around  $E_t = E_i$ , reflecting a symmetry in the capture of holes and electrons by the center. The denominator has a minimum value at  $E_t = E_i$ , so that the recombination U is maximum for recombination centers having energies near the middle of the gap, in both generation and recombination. As practical examples, gold and copper give rise to two effective recombination centers, with  $(E_t - E_i)$  in silicon equal to 0.03 and 0.01 eV respectively.

#### 1.2.1.1 Excess-Carrier Lifetime

To understand the physical significance of the net recombination rate U, we consider a semiconductor with no current flow, in which thermal equilibrium is disturbed by the sudden creation of equal number of excess electrons and holes. These excess carriers then decay spontaneously as the semiconductor returns to thermal equilibrium. Solutions of the continuity equation for this case give the excess electron density as a function of time. We consider this problem under the assumption that the disturbance of equilibrium corresponds to *low-level injection*. If we call the extra injected electron density n' and the extra hole density p', then low level injection implies that n' and p' are both much less than  $(n_o + p_o)$ , where  $n_o$  and  $p_o$  represent the thermalequilibrium densities of carriers in the semiconductor. From these definitions,  $n' = n - n_o$  and  $p' = p - p_o$ , with n' = p'.

If  $\sigma_n = \sigma_p$  then the continuity equation can be written

$$\frac{dn'}{dt} = G - R = -U = -\frac{(n_o + p_o)n'}{\left(n_o + p_o + 2n_i \cosh\left[\frac{E_t - E_i}{kT}\right]\right)}$$

(1.49)

Solving for n', we find that the excess carrier density decays exponentially with time

$$n'(t) = n'(0) \exp\left(-t/\tau_n\right)$$

(1.50)

where the lifetime  $\tau_n$  is given by

$$\tau_n = \left[\frac{n_o + p_o + 2n_i \cosh\left(\frac{E_t - E_i}{kT}\right)}{(n_o + p_o)}\right] \tau_o \tag{1.51}$$

For recombination centers to be effective, the term  $E_t - E_i$  is relatively small, and, therefore, the third term in the numerator is negligible compared to the sum of the first two. The equation then reduces to

$$\tau_n = \tau_o = \frac{1}{N_t v_{th} \sigma_o} \tag{1.52}$$

and

$$U = \frac{n'}{\tau_n} \tag{1.53}$$

We can observe that the excess-carrier lifetime is independent of the majority carrier concentration for recombination through recombination centers under low level injection. This behaviour can be understood physically by considering the kinetics of the recombination process. For example, in a p-type semiconductor, assuming traps near mid gap, most of the recombination centers are empty of electrons because  $E_f < E_t$ . The recombination process is therefore limited by the capture of electrons from the conduction band. Once an electron is captured by a recombination center, one of the many holes in the valence band is quickly captured. Thus, the rate-limiting step in the recombination process is the capture of a minority carrier by the recombination center; this is insensitive to majority-carrier population.

Minority-carrier lifetimes can vary widely, depending on the density and type of recombination centers in the semiconductor.

#### 1.2.2 AUGER RECOMBINATION

In the SHR recombination, an excess carrier is trapped in an intermediate center until a carrier of the opposite type interacts with the center itself and the two carriers recombine. This kind of recombination dominates at low-to-moderate carrier concentrations because electrons and holes are more likely to interact with the intermediate centers than with the low concentrations of mobile carriers However, at high concentrations, direct interaction of electrons and holes can lead to Auger recombination. In this process, an electron in the conduction band falls into an empty state (hole) in the valence band. The energy emitted by this transition is absorbed by another carrier, which also helps conserve the momentum. Auger recombination is the inverse of the avalanche pair-production process, in which the energy and momentum of an incoming carrier create a hole and an electron. The fact that this process requires three carriers, makes it likely to happen just in highly doped materials or when a large number of excess carrier is present. In n-type materials, two electrons and one hole interact, in p-type materials, two holes and one electron interact. Because two majority carriers are involved, the recombination rate U is proportional to the square of the majority carrier concentration. The Auger recombination rate  $U_A$  is given by the expression

$$U_A = R_A - G_A = c_n n \left( pn - n_i^2 \right) + c_p p \left( pn - n_i^2 \right)$$

(1.54)

where  $c_n$  and  $c_p$  are the Auger recombination coefficients. The reciprocal of the Auger lifetime can be written as

$$\frac{1}{\tau} = c_n N_a^2 \tag{1.55}$$

for electron recombination in heavily doped p-type material. The coefficient  $c_n$  for electrons in silicon is approximately  $1 \times 10^{-31} cm^{-6} s^{-1}$ . The Auger lifetime for holes in n-type material is about one-half to one-third that for electrons in a p-type. The effective lifetime, which considers

Figure 1.10: Auger recombination

both SHR and Auger recombination, is the sum of the recombination rates of the two processes so that

$$\frac{1}{\tau} = \frac{1}{\tau_{SHR}} + \frac{1}{\tau_A} \tag{1.56}$$

#### 1.2.3 SURFACE RECOMBINATION

Thus far, we have considered generation/recombination centers that are uniformly distributed throughout the bulk of the semiconductor material. In practical cases the surface can be the location of an abundance of extra localized states having energies within the forbidden gap. The presence of a passivating layer of silicon dioxide over the semiconductor surface, as is usual in devices made by the planar process, ties up many of the bonds that would otherwise contribute to surface states and protects the surface from foreign atoms. A passivating oxide can reduce the density of surface states from about  $10^{-15} cm^{-2}$  to less than  $10^{11}cm^{-2}$ . Even with passivated surface, however, surface states provide generation-recombination centers in addition to those present in the bulk.

The kinetics of generation-recombination at the surface are similar to those considered for bulk centers with one significant exception. While we considered the volume density  $N_t(cm^{-3})$  of bulk centers, we must discuss the area density  $N_{st}(cm^{-2})$  of surface centers. Although the  $N_{st}(cm^{-2})$  surface centers can be distributed over a thickness of several atomic layers, the poorly defined atomic structure near the semiconductor surface makes useful a description in terms of an equivalent number of states located at the surface. We can write an expression for the recombination rate U per unit area at the surface analogous to the Schockley-Hall-Read case.

$$U_s = \frac{N_{st}v_{th}\sigma_n\sigma_p(p_sn_s - n_i^2)}{\sigma_p[p_s + n_i\exp(\frac{E_i - E_s}{kT})] + \sigma_n[n_s + n_i\exp(\frac{E_{st} - E_i}{kT})]}$$

(1.57)

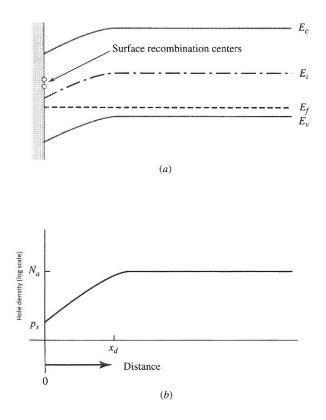

Figure 1.11: (a) Sketch of the energy-band diagram near the surface of p-type silicon covered with a passivating oxide. (b) Hole density near the surface

where the subscript s denotes concentrations and conditions near the surface and  $E_{st}$  is the energy of the surface generation/recombination centers. To stress the physical significance of surface recombination, we simplify the mathematics by considering the most efficient centers, which are located near mid gap, and equal capture cross sections for electrons and holes. With these assumptions the recombination rate equation reduces to

$$U_s = N_{st} v_{th} \sigma \frac{(p_s n_s - n_i^2)}{p_s + n_s + 2n_i \cosh\left(\frac{E_{st} - E_i}{kT}\right)}$$

(1.58)

The surface of a semiconductor is often at a different potential than the bulk so that surface carriers concentrations can differ from their values in the neutral bulk region. Even in the case of oxide-passivated surfaces, a space-charge region generally forms near the surface of the semiconductor. Dopant segregation at the oxide-silicon interface causes silicon surfaces to be less strongly p-type or more strongly n-type than the bulk. If we assume that the pn product remains constant throughout the space-charge region, the product at the surface  $p_s n_s$  can be expressed in terms of quantities at the neutral edge of the space-charge region:

$$p_s n_s = p_p(x_d) n_p(x_d) \cong N_a n_p(x_d) \tag{1.59}$$

in a p-type semiconductor. The recombination rate equation can then be written

$$U_{s} = N_{st}v_{th}\sigma \frac{N_{a}[n_{p}(x_{d}) - n_{p0}]}{(p_{s} + n_{s} + 2n_{i})} = N_{st}v_{th}\sigma \frac{N_{a}}{(p_{s} + n_{s} + 2n_{i})}n_{p}'(x_{d})$$

(1.60)

where we have assumed  $E_{st} \cong E_i$ . In this equation we have expressed the surface recombination rate  $U_s$  in terms of of the deviation  $n'_p$  of the minority carrier (electron) concentration from its equilibrium value at the interior boundary of the surface space charge region.

The coefficient of  $n'_p$  on the right of the equation is usually defined as a parameter s, which describes the characteristics of the surface recombination process:

$$s = N_{st}v_{th}\sigma \frac{Na}{(p_s + n_s + 2n_i)} \tag{1.61}$$

The value of s depends on the physical nature and density of the surface generation/recombination centers as well as on the potential at the surface. If the surface region is depleted of mobile carriers,  $n_s$  and  $p_s$  are small and s is large. If the surface is neutral,  $p \approx N_a$ ; s is small and is given by

$$s = s_o = N_{st} v_{th} \sigma \tag{1.62}$$

where the subscript o denotes that the surface and the bulk are at the same potential; that is, the surface region is neutral. The dependence of s on surface potential is important in silicon integrated circuits.

The dimensions of s are  $cm s^{-1}$ , and s is consequently called the surface combination velocity, although it is not directly related to an actual velocity. A physical interpretation of scan be obtained comparing the previous equation with the one that gives the minority-carriers lifetime; s is related to the rate at which excess carriers recombine at the surface, just as  $\frac{1}{\tau}$  is related to the rate at which they recombine at the bulk.

## **1.3 QUANTUM EFFICIENCY**

Radiative and non-radiative recombination processes are in competition one with the other, especially in optoelectronic devices, where we an increase in the second makes the efficiency of the device decrease. In a semiconductor with non-radiative recombination centers, the total recombination probability is given by

$$\frac{1}{\tau} = \frac{1}{\tau_r} + \frac{1}{\tau_{nr}} \tag{1.63}$$

thus the probability of having radiative emission is defined as

$$\eta_{int} = \frac{\frac{1}{\tau_r}}{\frac{1}{\tau_r} + \frac{1}{\tau_{nr}}} \tag{1.64}$$

The parameter  $\eta_{int}$  is called *internal quantum efficiency*, and is the ratio between the number

of phonons emitted and the total number of carriers that recombine. It's important to notice that, in a real device, not all the phonons emitted will be able to exit the material, come of them will be in fact refracted and re-absorbed.

We have seen that non-radiative recombination is a big problem in optoelectronic devices and it is not possible to avoid it, but even if it is not possible to make it completely disappear, there are some ways to reduce it, increasing the internal quantum efficiency. In general, because of the fact that non-radiative recombination is strongly connected to the material quality, we should increase it, reducing the defects densities, but we could also use some tricks to reduce surface recombination, like designing the device with the active region far enough from the surface and we could also increase the volume of the recombination region to decrease carriers densities and thus Auger recombination. Despite the fact that it's not possible to produce pure materials (in fact the impurities concentration is always higher than  $10^{12}cm^{-3}$ ) in the last fifty years things have greatly improved and through the optimization of fabrication and growth processes, the internal quantum efficiency has gone from 1% to 90/95%.

# Chapter 2

# LED DEVICES

# 2.1 LED ELECTRICAL PROPERTIES

#### 2.1.1 HOMOJUNCTION STRUCTURE AND ELECTRICAL MODEL

To understand the LEDs properties, we can start analyzing the pn homojunction, in fact LED devices are diodes, even if with some particular characteristics.

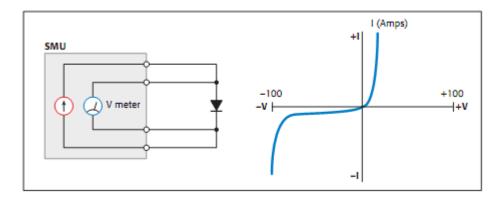

The I-V law of a LED device is the same of a pn junction

$$I = I_s \left( e^{qV/kT} - 1 \right) \tag{2.1}$$

with

$$I_s = qA\left(\sqrt{\frac{D_p}{\tau_p}}\frac{n_i^2}{N_D} + \sqrt{\frac{D_n}{\tau_n}}\frac{n_i^2}{N_A}\right)$$

(2.2)

As usual if  $V \gg \frac{kT}{q}$  we can simplify the I-V relation and write

$$I_s = qA\left(\sqrt{\frac{D_p}{\tau_p}}N_A + \sqrt{\frac{D_n}{\tau_n}}N_D\right)e^{q(V-V_D)/kT}$$

(2.3)

We know that

$$V_D = \frac{kT}{q} \ln\left(\frac{N_A N_D}{n_i^2}\right) \tag{2.4}$$

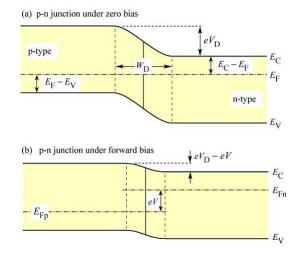

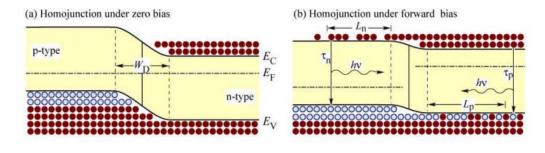

Figure 2.1: P-n junction under (a)zero bias and (b)forward bias

$$qV_D - E_G + (E_F - E_V) + (E_C - E_F) = 0 (2.5)$$

In a highly doped semiconductor  $E_C - E_F \ll E_G$ ,  $E_F - E_V \ll E_G$ , furthermore  $E_C - E_F$  and  $E_F - E_V$  weakly depend on the doping level. We can thus write

$$V_{th} \approx V_D \approx E_G/q \tag{2.6}$$

Under direct polarization conditions, the Shockley diode equation is usually simplified in the following way

$$I = I_s e^{qV/(\eta_{ideal}kT)} \tag{2.7}$$

where  $\eta_{ideal}$  is the diode ideality factor. For an ideal diode, this parameter value is one, while

for real devices it's higher. In a homojunction diode this parameter is higher than one, but normally lower than than tow, in heterojunctions (that as we will see later are very important for LED devices) instead, it can be even higher, in fact in these cases the externally measured ideality factor, is the sum of the ideality factors of the individual rectifying junctions, changing the I-V of the LEDs with respect to the ideal diode.

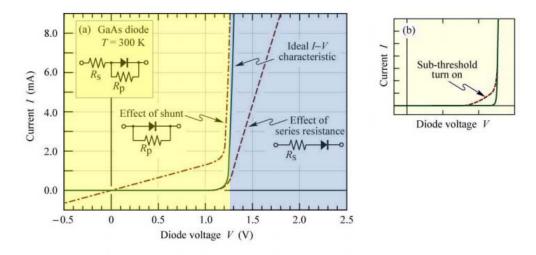

Another important parameter that influences the real device I-V, is the parasitic resistance. The effects of this resistance can be modeled through two circuital elements, a series resistance and a shunt resistance in parallel to the ideal diode. These two parameters strongly affect the real device characteristics, and an example of their effects can be seen in the following image. In figure (a) we can see the effects of the shunt and the series resistances, while in figure (b) we see the sub-threshold turn-on caused bu the shunt resistance only.

Figure 2.2: (a) Effect of series and parallel resistance (shunt) on I-V characteristic. (b) I.V with clearly discernible sub-threshold turn-on caused by defects or surface states

#### 2.1.2 HETEROJUNCTION STRUCTURE

We have seen that the radiative recombination rate is proportional to the product of the electrons and holes concentration, it is therefore important to observe the distribution of carriers under direct polarization conditions, to understand if the homojunction structure is suitable for LEDs fabrication.

A useful parameter to analyze this situation is the diffusion length, that we can evaluate using the following equations

$$L_n = \sqrt{D_n \tau_n} , \quad L_p = \sqrt{D_p \tau_p} , \qquad (2.8)$$

knowing that

$$D_n = \frac{kT}{q}\mu_n , \quad D_p = \frac{kT}{q}\mu_p \tag{2.9}$$

In a LED based on a homojunction structure, carriers recombine in a region with a length of about 3/4 times the diffusion length  $L_{p,n}$  (carriers diffuse on average over the diffusion lengths before recombining).

This is a problem for a LED, in fact it reduces radiative efficiency because it doesn't allow to have high concentrations of both holes and electrons in the same region (R = Bnp). To increase the device efficiency, it's useful to reduce the width recombination region, and to make this, double heterostructures are used. When this solution is employed, the dimension of the active region is determined by the geometry of the device, and not by the diffusion length anymore, we have in fact built a so called *quantum well*. Suppose that the active region were about 10 - 100 nm long, this shows clearly the improvement in the efficiency over the homojunction case, in which carriers can diffuse for several  $\mu m$ .

Figure 2.3: Carriers diffusion and recombination in an homojunction LED under (a)zero bias and (b)forward bias.

Figure 2.4: P-n heterojunction under forward bias. Carriers are confined by the barriers.

## 2.1.3 QUANTUM WELL

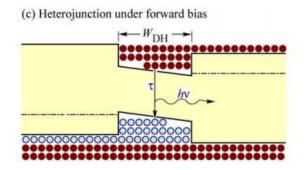

#### 2.1.3.1 THE INFINITE SQUARE-SHAPED QUANTUM WELL

The infinite.square shaped well potential is the simplest of all possible potential wells, and is defined as

$$U(x) = 0 \qquad \left(-\frac{1}{2}L \le x \le \frac{1}{2}L\right) \qquad (2.10)$$

$$U(x) = \infty \qquad \left( |x| > \frac{1}{2}L \right) \tag{2.11}$$

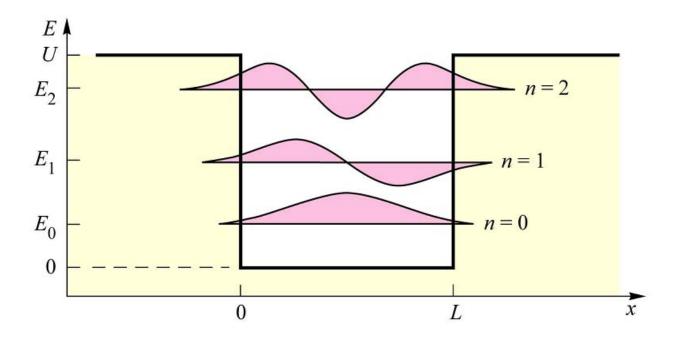

Figure 2.5: (a) Schematic illustration of the infinite square well potential. The solutions of this potential well are shown in terms of (b) eigenfunctions  $\psi_n(x)$ , (b) eigenstate energies  $E_n$ , and (c) probability densities  $\psi_n^* \psi_n$ .

To find the stationary solutions for  $\psi_n(x)$  and  $E_n we$  must find functions for  $\psi_n(x)$ , which satisfy the Schrödinger equation. The time-independent The time-independent Schrödinger equation contains only the differential operator d/dx, whose eigenfunctions are exponential or sinusoidal functions. Since the Schrödinger equation has the form of an eigenvalue equation, it is reasonable to try only eigenfunctions of the differential operator. Furthermore, we assume that  $\psi_n(x) = 0$ for |x| > L/2, because the potential energy is infinitely high in the barrier regions. Since the 3rd Postulate of quantum mechanics requires that the wave function be continuous, the wave function must have zero amplitude at the two potential discontinuities, that is  $\psi_n(x = \pm L/2) = 0$ . We therefore employ sinusoidal functions and differentiate between states of even and odd symmetry. We write for even-symmetry states

$$\psi_n(x) = A \cos\left[\frac{(n+1)\pi x}{L}\right] \quad \left(n = 0, 2, 4...and |x| \le \frac{L}{2}\right)$$

(2.12)

and for odd symmetry states

CHAPTER 2. LED DEVICES

$$\psi_n(x) = A \sin\left[\frac{(n+1)\pi x}{L}\right] \quad \left(n = 1, 3, 5...and |x| \le \frac{L}{2}\right) \tag{2.13}$$

Both functions have a finite amplitude in the well-region  $(|x| \leq L/2)$  and they have zero amplitude in the barriers, that is

$$\psi_n(x) = 0 \quad \left(n = 0, 1, 2...and |x| > \frac{L}{2}\right)$$

(2.14)

The shapes of the three lowest wave functions (n = 0, 1, 2...) are shown in Figure 2.5. In order to normalize the wave functions, the constant A must be determined. The condition  $\langle \psi | \psi \rangle = 1$  yields

$$a = \sqrt{2/L} \tag{2.15}$$

One can verify that the previous sinusoidal equations are solutions of the infinite square well by inserting the normalized wave functions into the Schrödinger equation. Insertion of the ground-state wave function (n = 0) into the Schrödinger equation yields

$$-\frac{\hbar^2}{2m}\frac{d^2}{dx^2}\sqrt{\frac{2}{L}}\cos\left(\frac{\pi x}{L}\right) = E_0\sqrt{\frac{2}{L}}\cos\left(\frac{\pi x}{L}\right)$$

(2.16)

Calculating the derivative on the left-hand side of the equation yields the ground state energy of the infinite square well

$$E_0 = \frac{\hbar^2}{2m} \left(\frac{\pi}{L}\right)^2 \tag{2.17}$$

The excited state energies (n = 1, 2, 3...) can be evaluated analogously. One obtains the eigenstate energies in the infinite square well as

$$E_n = \frac{\hbar^2}{2m} \left[ \frac{(n+1)\pi}{L} \right] \quad (n = 0, 1, 2...)$$

(2.18)

The spacing between two adjacent energy levels, that is  $E_n - E_{n-1}$ , is proportional to n. Thus, the energetic spacing between states increases with energy.

The probability density of a particle described by the wave function  $\psi$  is given by  $\psi \times \psi$  (2nd Postulate). The eigenstate energies are, as already mentioned, expectation values of the total energy of the respective state. It is therefore interesting to know if the eigenstate energies are purely kinetic, purely potential, or a mixture of both. The expectation value of the kinetic energy of the ground state is calculated according to the 5th Postulate:

$$\langle E_{Kin,0} \rangle = \langle \psi_0 | \frac{p^2}{2m} | \psi_0 \rangle$$

(2.19)

Using the momentum operator  $p = \left(\frac{\hbar}{i}\right) \left(\frac{d}{dx}\right)$  one obtains the expectation value of the kinetic

Figure 2.6: Asymmetric square well potential with well width L and barrier heights  $U_I$  and  $U_{III}$ . energy of the ground state

$$\langle E_{kin,0} \rangle = \frac{\hbar^2}{2m} \left(\frac{\pi}{L}\right)^2$$

(2.20)

which is identical to the total energy given in Eq. (2.17). Evaluation of kinetic energies of all other states yields

$$\langle E_{kin,0} \rangle = \frac{\hbar^2}{2m} \left[ \frac{(n+1)\pi}{L} \right]^2$$

$$(2.21)$$

The kinetic energy coincides with the total energy given in Eq. (2.18). Thus, the energy of a particle in an infinite square well is purely kinetic. The particle has no potential energy.

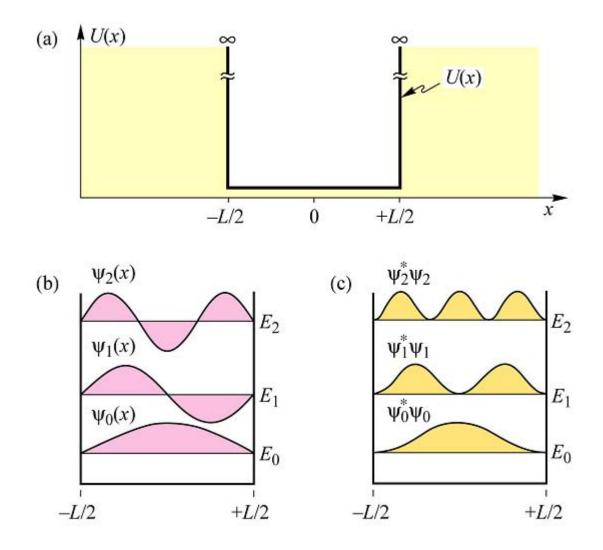

#### 2.1.3.2 THE ASYMMETRIC AND SYMMETRIC FINITE SQUARE-SHAPED QUANTUM WELL

In contrast to the infinite square well, the finite square well has barriers of finite height and considering the asymmetric well, the two barriers have a different height.

The potential energy is constant within the three regions I, II, and III, as shown in Figure 2.6. In order to obtain the solutions to the Schrödinger equation for the square well potential, the solutions in a constant potential will be considered first. Assume that a particle with energy E is in a constant potential U. Then two cases can be distinguished, namely E > U and E < U. In the first case (E > U) the general solution to the time- independent one-dimensional Schrödinger equation is given by

$$\psi(x) = A\cos(kx) + B\sin(kx) \tag{2.22}$$

where A and B are constants and

$$k = \sqrt{2mE/\hbar^2} \tag{2.23}$$

Insertion of the solution into the Schrödinger equation proves that it is indeed a correct solution. Thus the wave function is an oscillatory sinusoidal function in a constant potential with E > U. In the second case (E < U), the solution of the time-independent one-dimensional Schrödinger equation is given by

$$\psi\left(x\right) = Ce^{\kappa x} + De^{\kappa x} \tag{2.24}$$

where C and D are constants and

$$\kappa = \sqrt{\frac{2m\left(U-E\right)}{\hbar^2}} = \sqrt{\frac{2mU}{\hbar^2} - k^2} \tag{2.25}$$

Again, the insertion of the solution into the Schrödinger equation proves that it is indeed a correct solution. Thus the wave function is an exponentially growing or decaying function in a constant potential with E < U. Next, the solutions of an asymmetric and symmetric square well will be calculated. The potential energy of the well is piecewise constant, as shown in *Figure 2.6*. Having shown that the wave functions in a constant potential are either sinusoidal or exponential, the wave functions in the three regions I ( $x \le 0$ ), II (0 < x < L), and III ( $x \ge L$ ), can be written as

$$\psi_I(x) = A e^{\kappa_I x} \tag{2.26}$$

$$\psi_{II}(x) = A\cos(kx) + B\sin(kx) \tag{2.27}$$

$$\psi_{III}(x) = [A\cos(kL) + B\sin(kL)] e^{-\kappa_{III}(x-L)}$$

(2.28)

where A and B are unknown normalization constants. In this solution, the first boundary condition of the 3rd Postulate, i. e.  $\psi_I(0) = \psi_{II}(0)$  and  $\psi_{II}(L) = \psi_{III}(L)$ , is already satisfied. From the second boundary condition of the 3rd Postulate, i. e.  $\psi'_I(0) = \psi'_{II}(0)$  and  $\psi'_{II}(L) = \psi'_{III}(0)$ , the following two equations are obtained

$$A\kappa_I - Bk = 0 \tag{2.29}$$

$$A\left[\kappa_{III}\cos\left(kL\right) - k\sin\left(kL\right) +\right] + B\left[\kappa_{III}\sin\left(kL\right) + k\cos\left(kL\right)\right]$$

(2.30)

This homogeneous system of equations has solutions, only if the determinant of the system vanishes. From this condition, one obtains

$$\tan kL = \frac{kL\left(\kappa_I L + \kappa_{III} L\right)}{k^2 L^2 - \kappa_I L \kappa_{III} L}$$

(2.31)

which is the eigenvalue equation of the finite asymmetric square well. For the finite symmetric square well, which is of great practical relevance, the eigenvalue equation is given by

$$\tan kL = \frac{2kL\kappa L}{k^2L^2 - \kappa L^2} \tag{2.32}$$

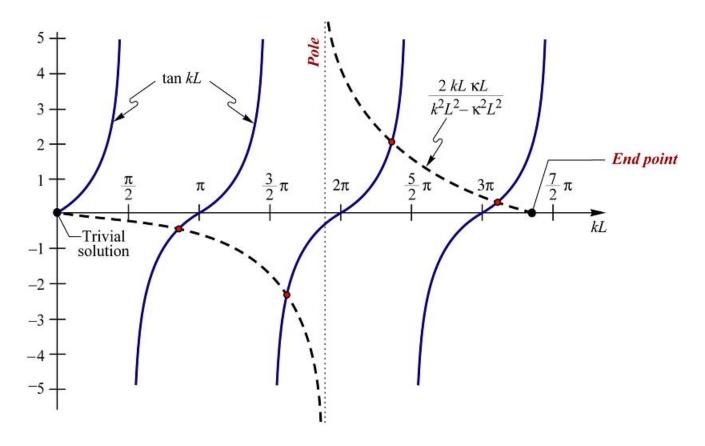

where  $\kappa = \kappa_{II} = \kappa_{III}$ . If  $\kappa$  is expressed as a function of k, then Eq. (2.32) depends only on a single variable, i. e., k. Solving the eigenvalue equation yields the eigenvalues of k and, by using Eqs. (2.23) and (2.25), the allowed energies E and decay constants  $\kappa$ , respectively. The allowed energies are also called the eigenstate energies of the potential. Inspection of Eq. (2.32) yields that the eigenvalue equation has a trivial solution kL = 0 (and thus E = 0) which possesses no practical relevance. Non-trivial solutions of the eigenvalue equation can be obtained by a graphical method. Figure 2.7 shows the graph of the left-hand and right-hand side of the eigenvalue equation. The dashed curve represents the right-hand side of the eigenvalue equation. The intersections of the dashed curve with the periodic tangent function are the solutions of the eigenvalue equation. The quantum state with the lowest non-trivial solution is called the ground state of the well. States of higher energy are referred to as excited states.

The dashed curve shown in Figure 2.7 has two significant points, namely a pole and an end point. The dashed curve has a pole when the denominator of the right-hand side of the eigenvalue equation vanishes, i. e., when  $kL = \kappa L$ . Using Eq (2.25), it is given by

Pole:

$$kL_{|Pole} = \sqrt{mU/\hbar^2}L\tag{2.33}$$

The dashed curve ends when  $k = (2mU/\hbar^2)^{\frac{1}{2}}$ . If k exceeds this value, the square root in Eq (2.25) becomes imaginary. The end point of the dashed curve is thus given by *End Point*:

$$kL_{|EndPoint} = \sqrt{2mU/\hbar^2}L \tag{2.34}$$

There are no further bound state solutions to the eigenvalue equation beyond the end point.

Now that the eigenvalues of k and  $\kappa$  are known, they are inserted into Eqs. (2.29) and (2.30); this allows for the determination of the constants A and B and the wave functions. Thus the allowed energies and the wave functions of the square well have been determined. It is possible to show that all states with even quantum numbers (n = 0, 1, 2...) are of even symmetry with respect to the center of the well, i. e.  $\psi(x) = \psi(-x)$ . All states with odd quantum numbers

Figure 2.7: Graphical solution of the eigenvalue equation for a symmetric quantum well. The function  $2kL\kappa L/(k^2L^2 - \kappa^2L^2)$  is the right-hand side of the eigenvalue equation. The crossing points of the tangent function and the dashed curve are solutions of the eigenvalue equation. The solution at kL = 0 is a trivial solution having no practical relevance.

(n = 1, 3, 5...) are of odd symmetry with respect to the center of the well, i. e.  $\psi(x) = -\psi(-x)$ . The even and odd state wave functions in the well are thus of the form

$$\psi_{II}(x) = A_{11} \cos\left[k_n\left(x - \frac{L}{2}\right)\right] \quad (for \ n = 0, 2, 4...)$$

(2.35)

$\quad \text{and} \quad$

$$\psi_{II}(x) = A_{11} \sin\left[k_n\left(x - \frac{L}{2}\right)\right] \quad (for \ n = 1, 3, 5...)$$

(2.36)

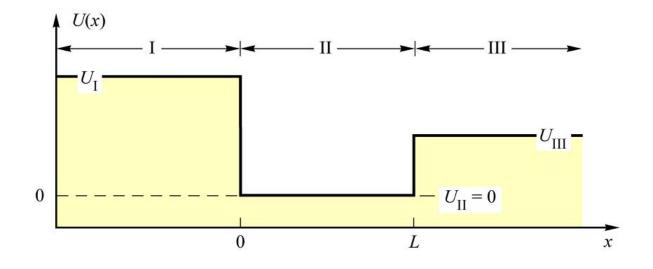

The three lowest wave functions of a symmetric square well are shown in

Figure 2.8: Schematic illustration of the three lowest wave functions of the symmetric quantum well.

#### 2.1.4 OTHER NONIDEALITIES AND CHARACTERISTICS

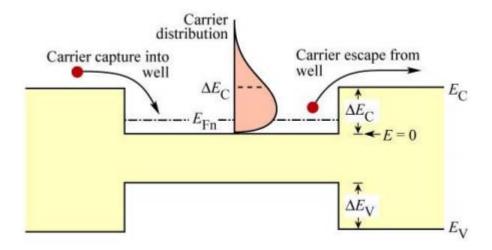

In practice, active region are not infinite-square shaped quantum wells, and even though barriers are usually higher than  $\frac{kT}{q}$ , some of the carriers can have enough energy to escape the well. This phenomenon is called *carrier escape*.

$$n_B = \int_{E_B}^{\infty} \rho_{dos} f_{FD} \left( E \right) dE \tag{2.37}$$

Another important leakage mechanism is the so called *carrier overflow*. When current becomes higher, the carriers concentration and Fermi energy increase, thus carriers can travel the quantum well without being captured, and radiative efficiency decreases.

Figure 2.9: Carrier capture and escape in a double heterostructure. Also shown is the carrier distribution in the active layer.

Considering a double heterostructure LED, with an active region with width  $W_{DH}$ , the continuity equation is

$$\frac{dn}{dt} = \frac{J}{qW_{DH}} - Bnp \tag{2.38}$$

In stationary condition  $\left(\frac{dn}{dt}=0\right)$  and high injection hypothesis (n=p) we can write

$$n = \sqrt{\frac{J}{qBW_{DH}}} \tag{2.39}$$

In these conditions it can be demonstrated that the following equation is also valid

$$\frac{E_F - E_C}{kT} = \left(\frac{3\sqrt{\pi}}{4}\frac{n}{N_C}\right)^{\frac{2}{3}}$$

(2.40)

In high injection conditions the Fermi energy increases and can reach the barrier value  $(E_F - E_C = \Delta E_C)$ . Carrier overflow takes place when

$$\frac{\Delta E_C}{kT} = \left(\frac{3\sqrt{\pi}}{4}\frac{n}{N_C}\right)^{\frac{2}{3}} \Longrightarrow \left(\frac{\Delta E_C}{kT}\right)^{\frac{3}{2}} = \frac{3\sqrt{\pi}}{4}\frac{n}{N_C} \Longrightarrow n^2 = \left(\frac{\Delta E_C}{kT}\right)^3 \left(\frac{4N_C}{3\sqrt{\pi}}\right)^2 \tag{2.41}$$

We can exploit this result and write

$$J = qW_{DH}Bn^2 = \left(\frac{\Delta E_C}{kT}\right)^3 \left(\frac{4N_C}{3\sqrt{\pi}}\right)^2 qBW_{DH}$$

(2.42)

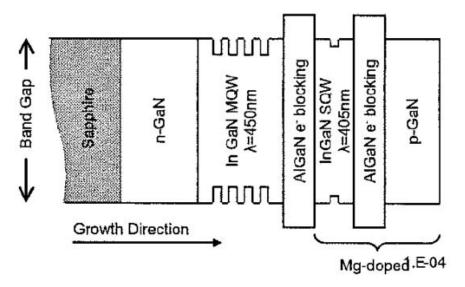

To reduce the influence of this undesired phenomenon multiple quantum-wells structures have been developed together with the introduction of electron blocking layers, pieces of different materials that change the band-diagram and prevent the carriers from flowing away from the wells.

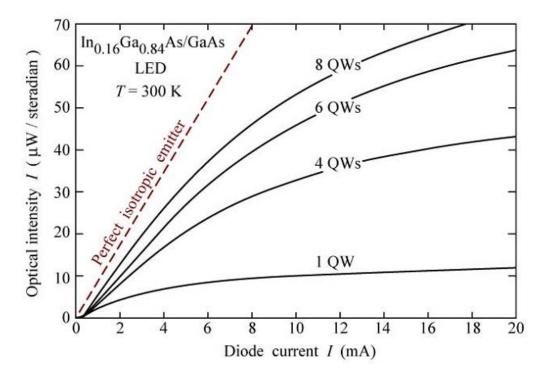

Figure 2.10: Optical intensity emitted by  $In_{0.16}Ga_{0.84}As/GaAs$  LEDs with active regions consisting of one, four, six and eight quantum wells and theoretical intensity of a perfect isotropic emitter (dashed line).

Figure 2.11: An example of multi-quantum well with electron blocking layer structure.

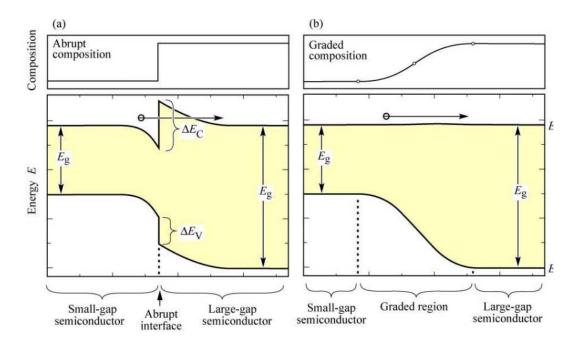

There's also another problem in the heterostructures, the parasitic resistance, due to the parabolic shape of the band diagram. This problem can be solved using a graded change in the composition of the material.

Figure 2.12: (a) Band diagram of an abrupt n-type - n-type heterojunction and (b) a graded heterojunction of two semiconductors with different band gap energy. The abrupt junction is more resistive than the graded junction due to the electron barrier forming at the abrupt junctions.

# 2.2 LED OPTICAL PROPERTIES

## 2.2.1 EFFICIENCY

The efficiency of a LED device is a complex parameter, that can be defined and calculated in different ways. In fact, the overall efficiency can be written as

$$\eta_0 = \eta_{inj} \eta_r \eta_{extraction} \tag{2.43}$$

where  $\eta_{inj}$  is the *injection efficiency*,  $\eta_r$  the radiative efficiency and  $\eta_{extraction}$  is the extraction efficiency.

The injection efficiency takes into account the fact that not all of the carriers injected reach the active region to give recombination, and is given by

$$\eta_{inj} = \left(1 + \frac{\mu_h N_A L_e}{\mu_e N_D L_h}\right)^{-1} \tag{2.44}$$

The second parameter on which the overall efficiency depends, the radiative efficiency  $\eta_r$ , is calculated through the following equation

$$\eta_r = \frac{1}{1 + \tau_r / \tau_{NR}} \tag{2.45}$$

and describes how many of the carriers that recombine, do it in a radiative way. As we already explained in chapter 1, this quantity strongly depends on the material quality.

The product  $\eta_{inj}\eta_r$  gives the so called *internal quantum efficiency*, that is defined as the ratio between the number of phonons emitted from the active region per second, and the number of electrons injected into the LED per second

$$\eta_{int} = \frac{(P_{int}/h\nu)}{(I/q)} \tag{2.46}$$

where  $P_{int}$  is the optical power emitted from the active region, and I the injected current. In an ideal LED this efficiency is one, because in it each charge quantum-particle (electron) produces one light quantum-particle (photon).

The last parameter in Eq. (2.43) is the extraction efficiency  $\eta_{extraction}$ . This is defined as the ration between the number of photons emitted from the LED's package per second, and the number of phonons emitted from the active region per second. It can be calculated also as

$$\frac{(P/h\nu)}{(P_{int}/h\nu)} \tag{2.47}$$

where P is the optical power emitted from the LED (package included). The extraction efficiency

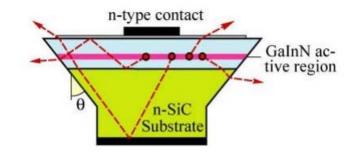

Figure 2.13: Phonons emission and reflection in a GaInN LED.

is usually less than 100% because not all of the photons emitted can escape from the LED; in fact these photons can be trapped inside the semiconductor because of what we call "total internal reflection", that is a multiple reflections phenomenon, and they can be absorbed by the metal contacts or the semiconductor itself, if they have higher energy than the band-gap  $E_g$ .

We can finally define the *external quantum efficiency*  $\eta_{ext}$  as the ratio between the number of phonons emitted outside the package per second, and the number of electrons injected into the LED per second

$$\frac{(P/h\nu)}{(I/q)} = \eta_{int}\eta_{extraction} \tag{2.48}$$

where P is the optical power emitted outside the package and I the injected current.

# 2.2.2 SPECTRAL CHARACTERISTICS

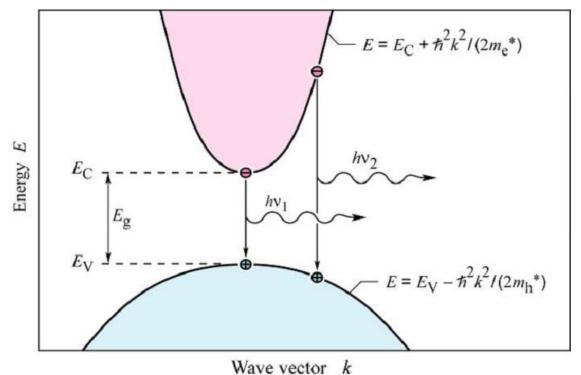

A LED device operates through spontaneous radiative emission, with the recombination of an electron-hole couple and transfer of the resulting energy to a phonon. The carriers distribution is described by the Fermi statistics, and at a temperature higher than zero they occupy a certain number of states with energy higher than the minimum. We know that

$$E_{kin} = \frac{p^2}{2m^*}$$

(2.49)

where

$$p = \frac{hk}{2\pi} \tag{2.50}$$

Therefore, if the valence and conduction bands have a parabolic shape, the carriers energies are

$$E = E_C + \frac{\left(\hbar k\right)^2}{2m_e^*} \tag{2.51}$$

for the electrons, and

$$E = E_C - \frac{\left(\hbar k\right)^2}{2m_h^*} \tag{2.52}$$

for the holes ( $m_e^*$  and  $m_h^*$  are the effective masses).

that's restor h

Figure 2.14: Parabolic electron and hole dispersion relations showing "vertical" electron-hole recombination and photon emission.

In the emission process both energy and momentum must be preserved. The momentum of the electron is given by

$$p = m \times v = \sqrt{2m * kT} \tag{2.53}$$

and the photon momentum by

$$p = (h/2\pi) k = h\nu/c = E_g/c$$

(2.54)

In order to have momentum conservation only "vertical" transitions can occur, and the condition on the conservation of energy, allows us to write

$$h\nu = E_C + \frac{\left(h/2\pi\right)^2 k^2}{2m_e^*} - E_V + \frac{\left(h/2\pi\right)^2 k^2}{2m_h^*} = E_g + \frac{\left(h/2\pi\right)^2 k^2}{2m_r^*}$$

(2.55)

where we have used the "reduced mass"  $m_r^*$ , defined as

$$\frac{1}{m_r^*} = \frac{1}{m_e^*} + \frac{1}{m_h^*} \tag{2.56}$$

The density of states has a parabolic dependence on energy, as we can see in the following equation

density of states

$$= \frac{1}{2\pi} \left(\frac{2m_r^*}{\hbar^2}\right)^{\frac{3}{2}} \sqrt{E - E_g}$$

(2.57)

and the carriers in the bands obey Boltzmann distribution

$$f_B(E) = e^{-E/kT} \tag{2.58}$$

we can therefore deduce that the emitted radiation intensity (as a function of energy) is proportional to the product of the former two equations.

$$I(E) \propto \sqrt{E - E_g} e^{-E/kT}$$

(2.59)

Exploiting this relation we can deduce the LED's theoretical emission spectrum, the *I-E* curve

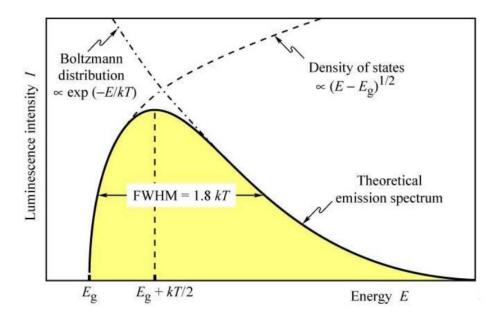

Figure 2.15: LED's theoretical emission spectrum

(luminescence intensity as a function of energy) and observe that the emission peak does not correspond to  $E_g$ , instead it is set at  $E_g + kT/2$ . Therefore we can also see that the width at half maximum of the emission spectrum as

$$FWHM = 1.8kT \tag{2.60}$$

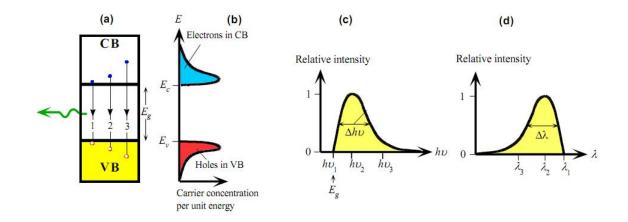

Figure 2.16: (a) Energy band diagram with recombination paths. (b) Energy distribution of electrons in the conduction band and holes in the valence band. The highest electron concentration is  $(\frac{1}{2}) k_B T$  above  $E_C$ . (c) The relative light intensity as a function of photon energy based on (b). (d) Relative intensity as a function of wavelength in the output spectrum based on (b) and (c).

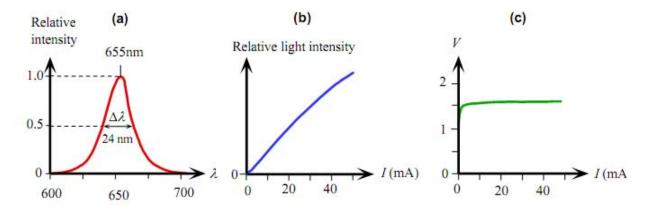

Figure 2.17: (a) Typical output spectrum (relative intensity vs. wavelength) from a red GaAsP LED. (b) Typical output light power vs. forward current. (c) Typical I-V characteristics of a red LED. The turn-on voltage is around 1.5V.

The width of the LED spectrum is of about 30 - 40nm, and if we consider human vision it is

short enough to make us see it as a single colour. nevertheless it is long enough to influence the practical applications of the device, for example in transmission through optical fiber. In fact in this medium, radiations with different wavelength travel at different velocities and scattering limits the bit-rate distance product. A LED spectrum characteristics can vary for different reasons, for example in high injection conditions it broadens, but the main parameter that influences it, is temperature. In fact an increase in temperature makes Shockley-Read-Hall non-radiative recombination and surface recombination higher, and also the number of carriers that can escape the well increases, therefore emission intensity decreases.

$$I = I_{|300K} \exp\left(-\frac{T - 300K}{T_1}\right)$$

(2.61)

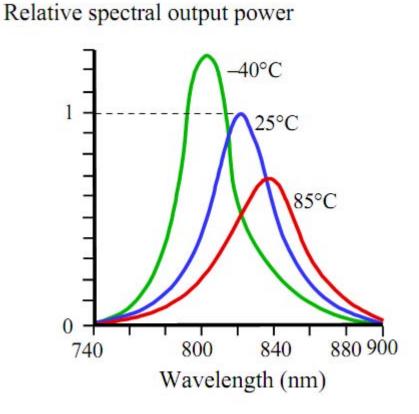

Another important effect of temperature is the decrease of the energy gap, consequently, with

an increase in temperature, the LED spectrum peak shifts to lower energies, and its intensity decreases. Finally, as we already saw in Eq. (2.60), at higher temperatures the width at half maximum increases.

Figure 2.18: The output spectrum from AlGaAs LED.Values normalized to peak emission at 25°C.

# 2.2.3 LIGHT EXTRACTION AND GENERAL EFFICIENCY IM-PROVEMENT TECHNIQUES

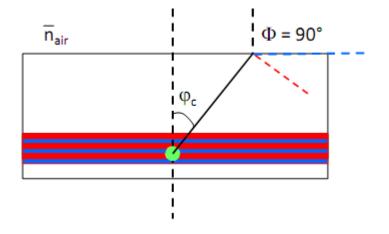

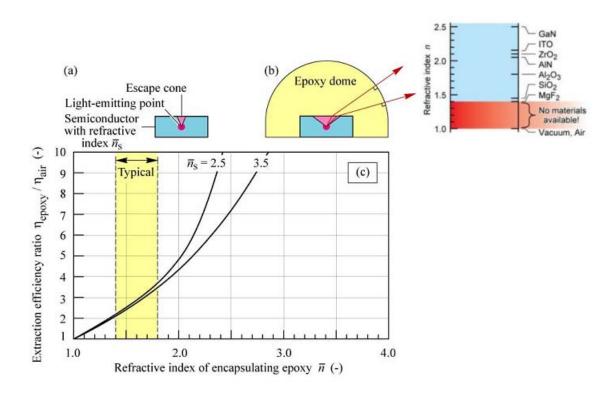

Light generated inside a semiconductor cannot escape from the semiconductor if it is totally internally reflected at the semiconductor-air interface. If the angle of incidence of the a light ray is close to normal incidence, light can escape from the semiconductor. However, when the angle of incidence is higher tan the so called *critical angle*, we have total internal reflection that reduces the external efficiency significantly. This parameter is determined by the ratio between the refractive indices at the air-semiconductor surface, and, assuming that the angle of incidence in the semiconductor at the semiconductor-air interface is given by  $\phi$ , we can evaluate the critical angle exploiting the *Snell law*.

Figure 2.19: Critical angle

$$\sin\varphi_c = \frac{n_{air}}{n_s} \approx \varphi_c \tag{2.63}$$

This approximation is valid because refractive index of semiconductors is usually high.

The angle of total internal reflection defines a light escape cone. Light emitted into this cone can escape from the semiconductor, whereas light emitted outside the cone is subject to total internal reflection.

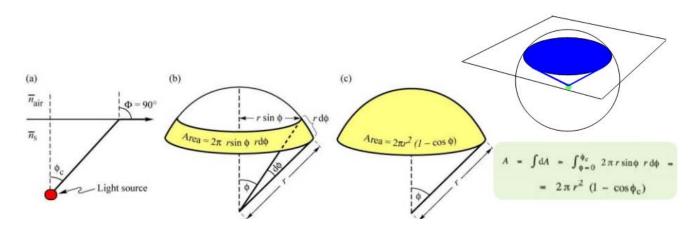

Figure 2.20: (a) Definition of the escape cone by the critical angle  $\phi_C$ . (b) Area element dA. (c) Area of calotte-shaped section of the sphere defined by radius r and angle  $\phi_C$ .

To determine the total fraction of light that is emitted into the light escape cone, we calculate the surface area of the calotte.shaped surface shown in Fig. (2.20) (b) and (c).

$$A = \int dA = \int_{\phi=0}^{\phi_C} 2\pi r \sin \phi \, r d\phi = 2\pi r^2 \left(1 - \cos \phi_C\right)$$

(2.64)

Let us assume that light is emitted from a point.like source in the semiconductor with a total

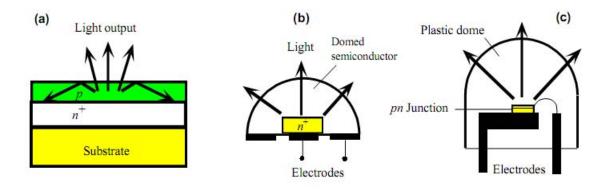

Figure 2.21: (a) Reflection of part of the light generated in a flat LED. (b) Dome shaped semiconductor to improve extraction. (c) LED encapsulated in a plastic dome.

power of  $P_{source}$ . Then the power that can escape from the semiconductor is given by

$$P_{escape} = P_{source} \frac{2\pi r^2 \left(1 - \cos \phi_C\right)}{4\pi r^2}$$

(2.65)

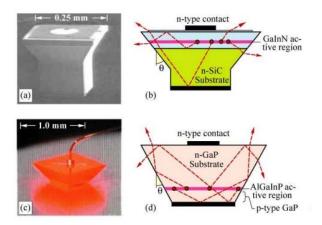

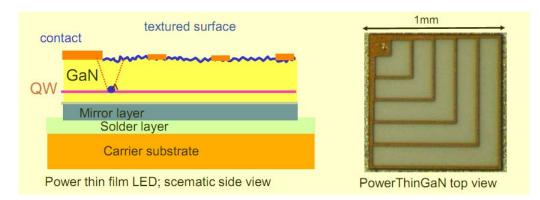

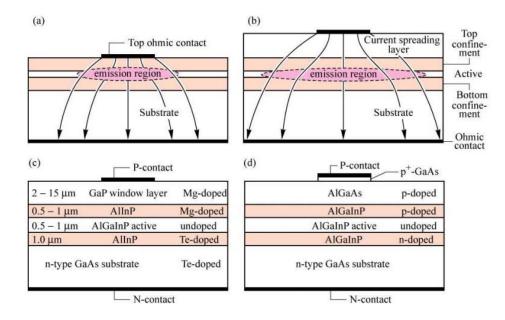

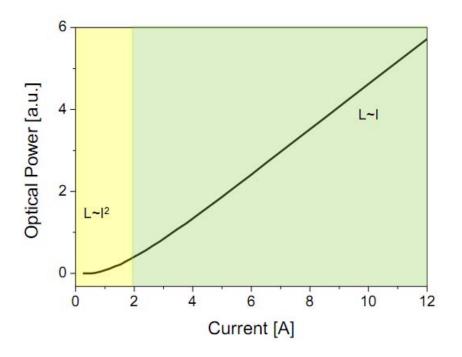

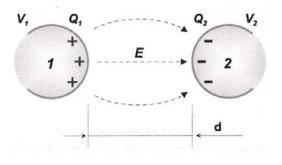

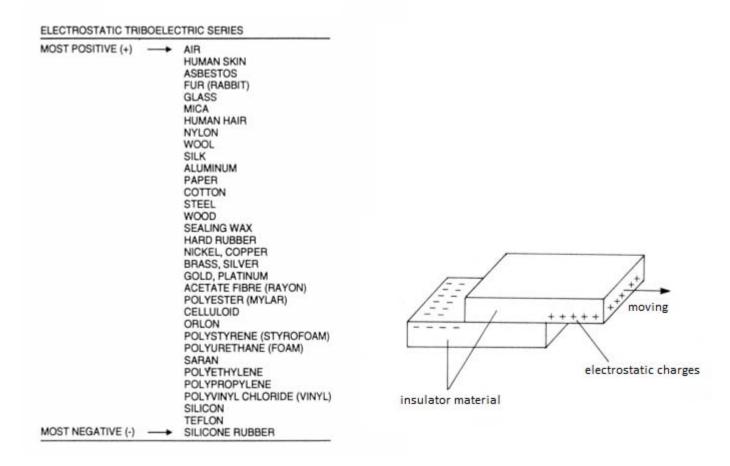

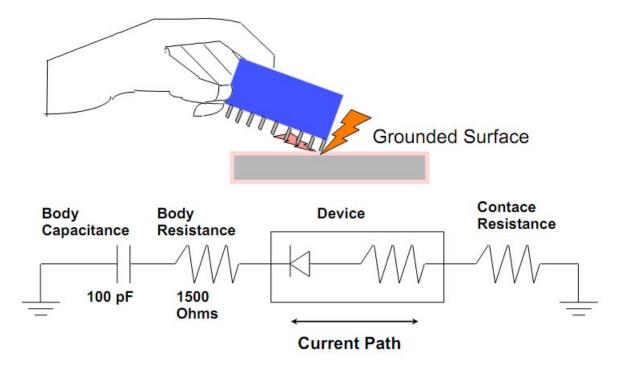

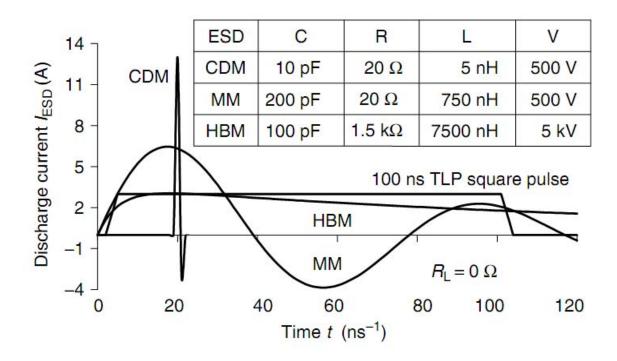

where  $4\pi r^2$  is the entire surface area of the sphere with radius r. The calculation indicates that only a fraction of the light emitted inside a semiconductor can escape from it. This fraction is given by