## Università degli Studi di Padova

#### DIPARTIMENTO DI INGEGNERIA DELL'INFORMAZIONE

Corso di Laurea Magistrale in Ingegneria Elettronica

## Output stage design of voltage regulator for synchronous generators

*Relatore:* PROF. NICOLA TRIVELLIN

Laureando: SIMONE SCARPARI 2003342

Anno Accademico 2021-2022

Data di laurea 03/10/2022

## Contents

|   | Intro                                                     | oductic                                                         | on                                    | 1  |  |  |  |

|---|-----------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------|----|--|--|--|

| 1 | Voltage regulation in electrical generators               |                                                                 |                                       |    |  |  |  |

|   | 1.1 The three-phase synchronous generator                 |                                                                 |                                       |    |  |  |  |

|   | 1.2                                                       | General structure                                               |                                       |    |  |  |  |

|   | 1.3                                                       | xcitation system                                                | 8                                     |    |  |  |  |

|   |                                                           | 1.3.1                                                           | Rotating excitation                   | 9  |  |  |  |

|   |                                                           | 1.3.2                                                           | Static excitation                     | 9  |  |  |  |

|   |                                                           | 1.3.3                                                           | Brushless excitation                  | 10 |  |  |  |

|   | 1.4 The voltage regulator                                 |                                                                 |                                       |    |  |  |  |

|   |                                                           | 1.4.1                                                           | Functional block                      | 12 |  |  |  |

|   |                                                           | 1.4.2                                                           | Protection block                      | 13 |  |  |  |

| 2 | Analysis of the current voltage regulator output stage    |                                                                 |                                       |    |  |  |  |

|   | 2.1                                                       | Switc                                                           | hing inductive load                   | 15 |  |  |  |

|   |                                                           | 2.1.1                                                           | Simultaneous dual switch - ideal case | 17 |  |  |  |

|   |                                                           | 2.1.2                                                           | Single switch - real case             | 19 |  |  |  |

|   | 2.2                                                       | Current Mecc Alte voltage regulator output stage implementation |                                       |    |  |  |  |

|   |                                                           | 2.2.1                                                           | Thyristors                            | 24 |  |  |  |

|   |                                                           | 2.2.2                                                           | Circuit operation                     | 25 |  |  |  |

|   |                                                           | 2.2.3                                                           | Limits                                | 32 |  |  |  |

| 3 | Development of the voltage regulator output stage circuit |                                                                 |                                       |    |  |  |  |

|   | 3.1                                                       | Company request                                                 |                                       |    |  |  |  |

|   | 3.2 Project specification                                 |                                                                 |                                       |    |  |  |  |

|   |                                                           | 3.2.1                                                           | Short circuit test                    | 37 |  |  |  |

|   | 3.3                                                       | Circui                                                          | it development                        | 38 |  |  |  |

|   |                                                           | 3.3.1                                                           | Switching frequency                   | 39 |  |  |  |

|   |                                                           | 3.3.2                                                           | Full wave rectification               | 45 |  |  |  |

|   |                      | 3.3.3                         | Controllable power switch                                | 48  |  |  |  |  |

|---|----------------------|-------------------------------|----------------------------------------------------------|-----|--|--|--|--|

|   |                      | 3.3.4                         | Driving circuit                                          | 49  |  |  |  |  |

|   |                      | 3.3.5                         | Freewheeling diode                                       | 56  |  |  |  |  |

|   |                      | 3.3.6                         | Auxiliary winding electric equivalent model              | 58  |  |  |  |  |

|   |                      | 3.3.7                         | Solution attempts                                        | 64  |  |  |  |  |

|   |                      | 3.3.8                         | Solution for auxiliary inductance problem                | 75  |  |  |  |  |

|   |                      | 3.3.9                         | Turn-off snubber                                         | 80  |  |  |  |  |

|   | 3.4                  |                               | circuit topology                                         | 91  |  |  |  |  |

|   | 3.5                  |                               |                                                          |     |  |  |  |  |

| 4 | Thermal management 9 |                               |                                                          |     |  |  |  |  |

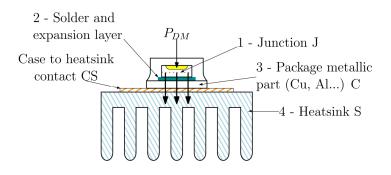

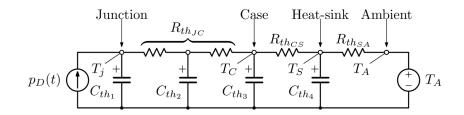

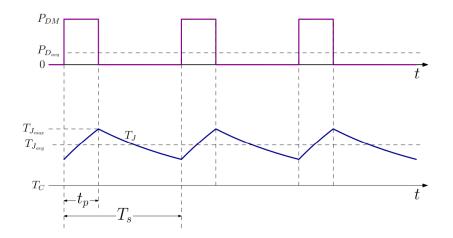

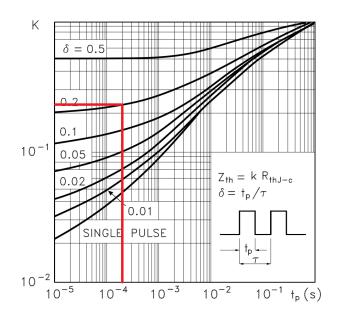

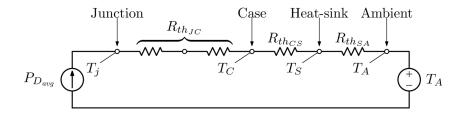

|   | 4.1                  | Contro                        | ol of semiconductor device temperatures                  | 97  |  |  |  |  |

|   | 4.2                  | Heat dispersal                |                                                          |     |  |  |  |  |

|   | 4.3                  | 3 Power losses computation    |                                                          |     |  |  |  |  |

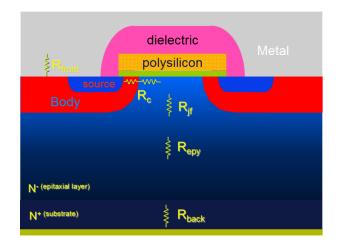

|   |                      | 4.3.1                         | MOSFET power losses                                      | 101 |  |  |  |  |

|   |                      | 4.3.2                         | Thyristor power losses                                   | 108 |  |  |  |  |

|   |                      | 4.3.3                         | Freewheeling diode power losses                          | 110 |  |  |  |  |

|   | 4.4                  | Heat sinks thermal resistance |                                                          |     |  |  |  |  |

|   |                      | 4.4.1                         | MOSFET heat sink thermal resistance                      | 120 |  |  |  |  |

|   |                      | 4.4.2                         | Thyristor heat sink thermal resistance                   | 122 |  |  |  |  |

|   |                      | 4.4.3                         | Freewheeling diode heat sink thermal resistance          | 123 |  |  |  |  |

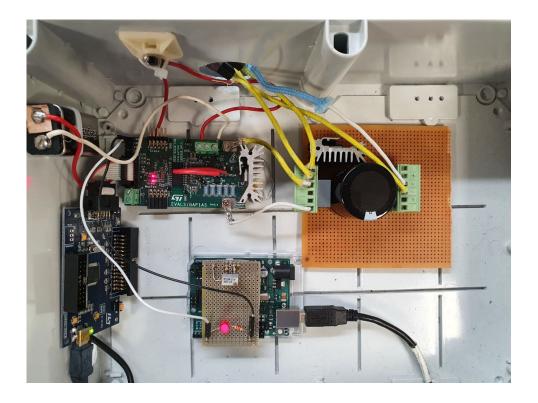

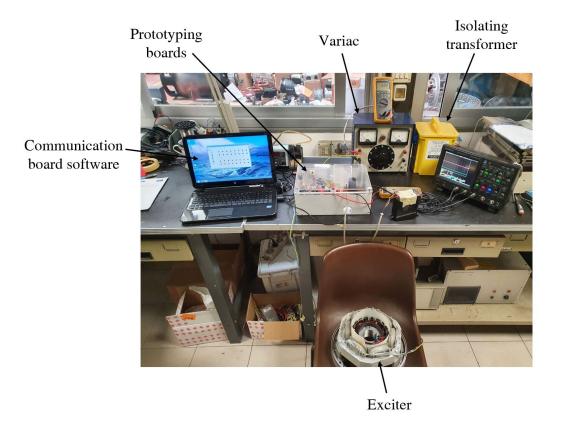

| 5 | Exp                  | xperimental validation 12     |                                                          |     |  |  |  |  |

|   | 5.1                  | Circui                        | t test bench setup                                       | 125 |  |  |  |  |

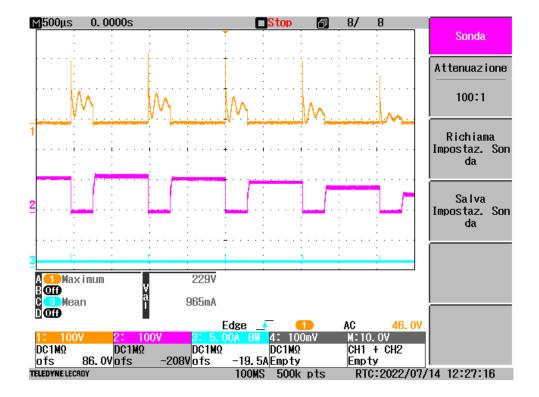

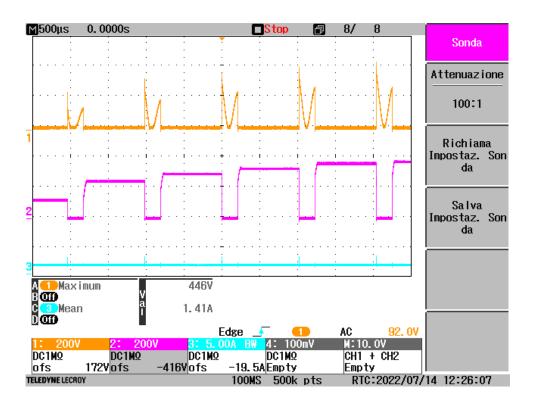

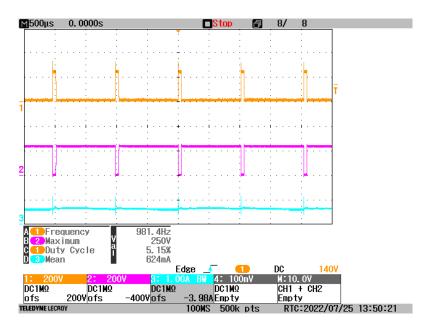

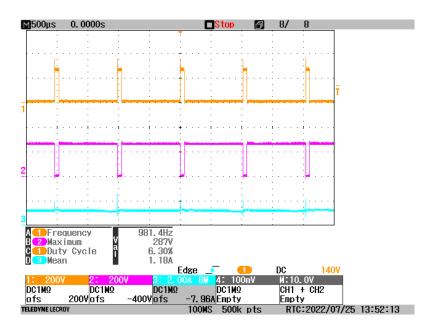

|   |                      | 5.1.1                         | Results at project specification ratings                 | 127 |  |  |  |  |

|   | 5.2                  | Test of                       | n real generators                                        | 129 |  |  |  |  |

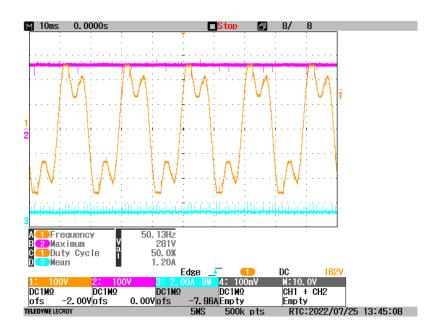

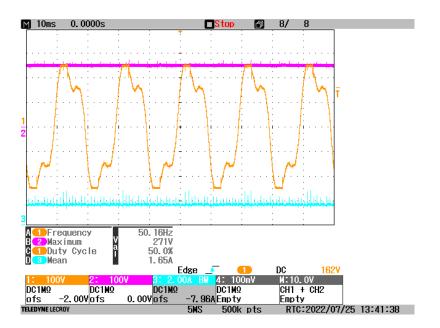

|   |                      | 5.2.1                         | Results on ECP4 model                                    | 131 |  |  |  |  |

|   |                      | 5.2.2                         | Results on ECO38 model                                   | 137 |  |  |  |  |

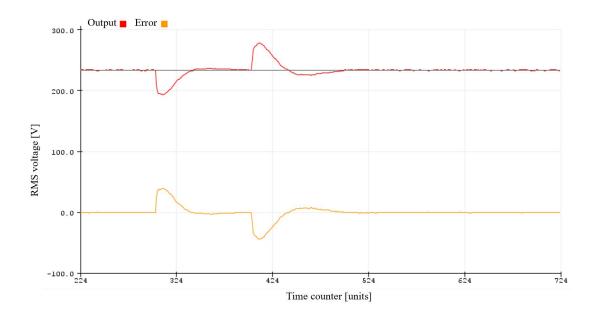

|   | 5.3                  | Test of                       | n generator excitation system dynamic response           | 141 |  |  |  |  |

|   |                      | 5.3.1                         | Closed-loop regulation                                   | 142 |  |  |  |  |

|   |                      | 5.3.2                         | PID controller                                           | 142 |  |  |  |  |

|   |                      | 5.3.3                         | Results on dynamic response at generator load connection | 145 |  |  |  |  |

| 6 | Con                  | Conclusions 149               |                                                          |     |  |  |  |  |

|   | Bibl                 | Bibliography                  |                                                          |     |  |  |  |  |

#### Abstract

The aim of this thesis is the design of the output stage for voltage regulators used in synchronous generators made by the company Mecc Alte SpA. For design it is understood: the study, development, simulation, implementation and test of such a circuit, in order to provide an innovative design that Mecc Alte can exploit for its future regulator product releases. Obviously, at the moment, the company has already developed multiple regulators, currently working correctly on the alternators already sold. For this reason, it is necessary to say that in this context the thesis has the objective of improving the existing regulators by modifying the output stage that regards the power circuitry that controls the current supplied to the alternator, fundamental in order to guarantee its correct control.

Lo scopo di questa tesi è la progettazione dello stadio di uscita per regolatori di tensione usati in generatori sincroni prodotti dall'azienda Mecc Alte SpA. Per progettazione si intende lo studio, lo sviluppo, la simulazione, l'implementazione ed il test di tale circuito, al fine di offrire un'innovazione che Mecc Alte possa sfruttare per le sue future versioni di regolatori. Ovviamente durante lo svolgimento di questa attività l'azienda ha già sviluppato diversi regolatori, che funzionano correttamente e che sono venduti assieme agli alternatori. Per questa ragione c'è da dire che in questo contesto la tesi ha l'obiettivo di migliorare i regolatori esistenti attualmente usati modificando lo stadio di uscita, che riguarda il circuito di potenza che controlla la corrente fornita all'alternatore, fondamentale per garantire il suo corretto controllo.

## Introduction

This thesis is the result of the curricular internship in Mecc Alte SpA. The company main business is the manufacture of synchronous generators. In fact, generators, in addition to the fundamental mechanical and electrical elements, are often controlled in order to guarantee the correct operation in every working condition. In particular, the controller aims to regulate the alternating output voltage to a constant level, which is desired to be independent on the electric utilities the generator supplies. Typically this control, as done in Mecc Alte, is electronically performed by a microcontroller based PCB. This explains the interest of electronic engineering in this environment.

One of the most exciting aspects of this thesis is that it is developed within a real industrial environment. The possibility to get involved in the industrial world, which has an actual interest in this work activity, is extremely important for the student. Certainly some adding difficulties are present, like the high level of autonomy required, the obvious company precedence in its business or the need to learn basic practical skills to make do as much as possible. However, if on one hand those represent a step to overcome, on the other hand, they allow the student to develop extra experience for personal background.

Additional interest for this thesis is generated because it is developed on and for real industrial products, which, at the time this thesis is written, are currently produced and sold to customer companies. The possibility to design and develop a solution for the pragmatic environment of the industrial world is an element of great interest for a graduation thesis, because the proposed solution has to guarantee a series of properties regarding the meeting of regulation requirements, reliability and durability over time, all features not commonly required in the execution of a common project, in which the focus is only the project functionality.

The aim of this thesis is the investigation of the modification of a part of the voltage regulator circuit, that is its output stage. This part has the role to manage the power signals of voltage and current involved to enable the possibility to adjust the output voltage the machine generates. The company already has a series of voltage regulators

#### Contents

that are currently mounted and sold with the generators. The company objective is to develop a new circuit based on a different kind of power switch. Specifically, the current versions of the power stage of the voltage regulators are based on a thyristor. The aim is to substitute the thyristor with a both turn-on and turn-off controllable silicon power switch, like a power MOSFET or IGBT, because some advantages in the control system, which are going to be described throughout the thesis, are expected. In order to do so the thesis discusses the study, development, simulation, implementation and test of such a circuit, in order to provide an innovative design that Mecc Alte can exploit for its future regulators releases.

The thesis work is subdivided in the following chapters:

- Chapter 1: an overview regarding the electrical generator, the excitation system and the voltage regulator is presented.

- Chapter 2: the current thyristor-based output stage of the voltage regulator is analyzed, with an emphasis on its issues and limitations.

- Chapter 3: in the core of the thesis, the following topics are discussed: the development of the new circuit, the encountered issues, the solution attempts, the reasons for their inapplicability, the final proposed solution.

- Chapter 4: the thermal analysis of the power devices is performed to evaluate the power losses and to compute the required thermal resistances of the heat sinks.

- Chapter 5: the results of the thesis work are reported.

- Chapter 6: the conclusion provides a summary of the work completed, including a commentary on the advantages and disadvantages of the proposed circuit compared with the present design and describes possible future developments.

## Chapter 1

## Voltage regulation in electrical generators

This chapter is intended to introduce gradually the voltage regulation in synchronous generators. For this reason, the discussion starts from the electrical generator, known also as alternator, with a particular focus on the AC three-phase synchronous generator, since it is the electrical machine on which the consequent discussion on the development of the output stage of voltage regulator will be about.

The electrical generator is an electrical machine which converts mechanical energy into electrical energy. Its operation is based on the electromagnetic induction phenomenon, ruled by Faraday's law: the variation of magnetic flux linked by a coil induces an electromotive force (EMF) at the coil terminals.

$$f_{em} = -\frac{d\Phi(\vec{B})}{dt} \tag{1.0.1}$$

This old principle, discovered by the english physician Michal Faraday in 1831 (but important are the contributions also of Heinrich Lenz and Franz Ernst Neumann) is the one exploited to produce eletricity starting from a mechanical source of energy.

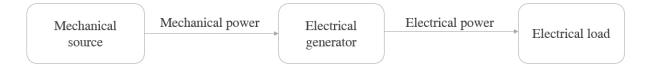

Figure 1.0.1: Power flow in the electrical generator.

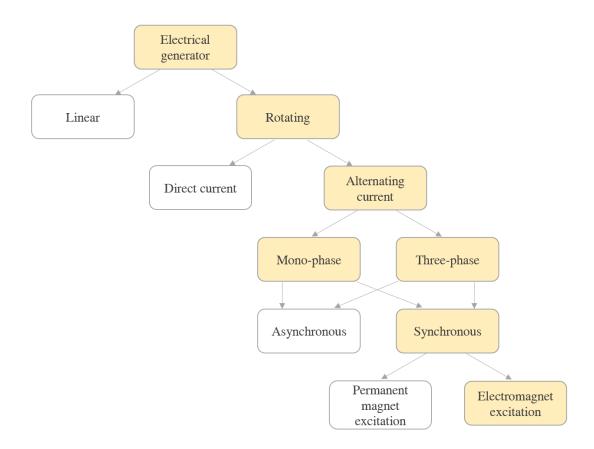

Even if it's possible to hypothesize the existence of electrical machines characterized by translational motion (linear machines), for reasons of cost and simplicity, electrical generators are always rotational machines. This means they use a rotating magnetic field with a stationary armature.

Rotating electrical generators can be classified in continuous current (DC) and alternating current (AC) generators related to the kind of voltage and current they produce. The former produce electrical energy having constant voltage and current in time; the latter produce electrical energy having a sinusoidal varying voltage and current in time.

In case of AC generators it is possible to distinguish also on the number of phases of the electrical circuit connected to the load. Typically there are single-phase and threephase generators.

Another classifying factor differentiates asynchronous from synchronous generators. In an asynchronous generator, the rotational element angular velocity differs from that of the magnetic field; in the synchronous generators, those two velocities are coincident, since the magnetic field is fixed with the rotating element.

Finally, there are two ways the magnetic induction field can be produced in synchronous generator rotors: either using permanent magnets or electromagnets, a continuous current-carrying winding wrapped around a ferromagnetic core. Considering these multi-level classifications, this thesis will consider only rotating AC synchronous generators with an electromagnet excitation rotor. The reader has to keep in mind that from here on the treatment will consider only three-phase generators; mono-phase ones can be considered as a more simple sub-case of three-phase systems, for which the following description represents a more complete discussion.

Figure 1.0.2: Generator classification. The coloured blocks highlight the sub-class of interest for the thesis.

#### **1.1** The three-phase synchronous generator

In this section the general structure of a three-phase synchronous generator is described, with the objective of introducing the excitation system, and subsequently, the voltage regulation.

Three-phase synchronous generators are used in many fields. A typical application is the energy production in power plants, where the mechanical power coming from a hydraulic, steam or gas turbine is converted into electricity. Another application, characterized by much lower power and voltage, is the genset, in which a diesel combustion engine feeds the alternator providing electrical energy to sites not reached by the electric grid, for emergency services supply and in case of the main grid blackouts. Mecc Alte alternators belong to this second category.

Figure 1.1.1: Historical image of a three-phase alternator made by Kraftwerk Heimbach, Germany.

Figure 1.1.2: An example of a three-phase Mecc Alte alternator, utilized in gensets.

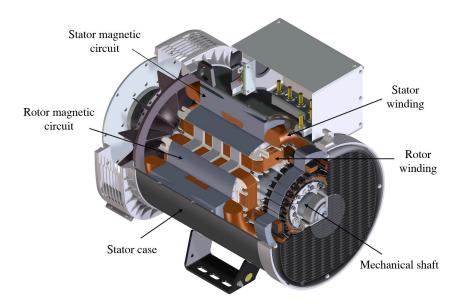

#### **1.2** General structure

The structure of a three-phase alternator is typically characterized by a *fixed induced* and a *rotating inductor* (as in case of all Mecc Alte products). Going from the center-out it is possible to find:

- **Mechanical shaft** that transfer the mechanical energy from the source to the alternator.

- **Rotor magnetic circuit** fixed and solidly rotating with the shaft, is crossed by the magnetic flux present in the machine.

- **Rotor winding** creates the magnetic field enabling the machine operation. In the typical use case of gensets the salient-pole field coil is used: the rotor winding is composed of coils wound around the poles. A constant excitation current flow-ing through the coils energizes the poles. The resulting inductor magnetic field, costant in value, rotates at the same angular velocity as the shaft.

- **Stator magnetic circuit**, separated from the rotor magnetic circuit by a small airgap, presents slots for the stator winding conductors.

- Stator winding, a stationary set of conductors wound in coils fixed in the slots are separated in three phases 120° apart. The magnetic field cuts across the conductors, generating an induced EMF, as the mechanical input causes the rotor to turn. The rotating magnetic field induces an AC voltage at the stator winding terminals.

- **Stator case**, mechanically connected to the stator magnetic circuit, the purpose of which is to support and provide suitable mounting points for the entire alternator assembly.

Figure 1.2.1: Visible structure of a Mecc Alte synchronous generator. It is possible to recognize the listed elements.

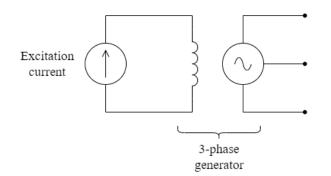

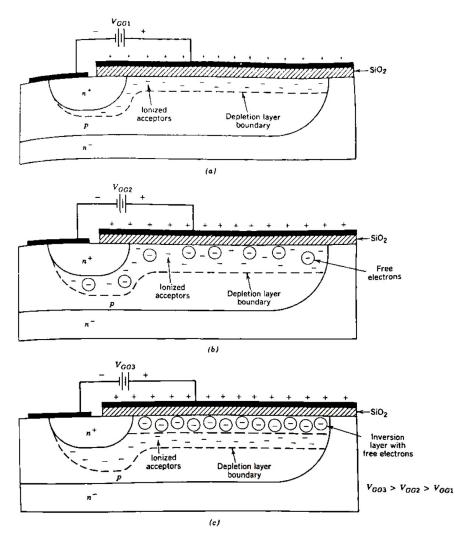

#### **1.3** The excitation system

The excitation system has the purpose of appropriately energizing the inductor circuit. A direct current provided by this system, flowing into the pole windings, creates electromagnets generating the required magnetic field.

Figure 1.3.1: Basics of excitation system.

All the windings are series-connected so the same current flows in each one. This way, each field coil produces the same magnetic flux intensity. In addition adjacent poles windings are arranged in such a way that they have opposing current directions, thus creating alternating magnetic poles N-S. The direct current can be provided to the

rotor winding using three excitation system types: rotating excitation, static excitation and brushless excitation. All these solutions have in common the necessity to vary the current in a very wide interval in order to maintain the correct operation of the generator for all the critical operation situations, like the abrupt connection or disconnection of the electric load. This continuous adjustment is performed by the voltage regulator, that will be investigated in Section 1.4.

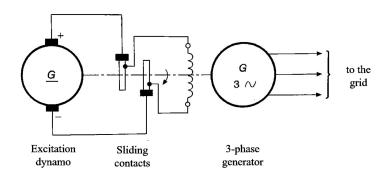

#### **1.3.1** Rotating excitation

Mostly used in the past, in the rotating excitation system the excitation current is supplied by a direct current generator (excitation dynamo) mounted on the main shaft, from which it receives the mechanical power. The DC voltage induced in the dynamo is used to supply the generator rotor winding, using a system of sliding contacts, formed by brushes and rings.

Figure 1.3.2: Rotating excitation block scheme [1].

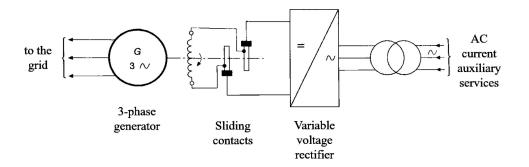

#### **1.3.2** Static excitation

Typical of high power applications, static excitation does not require any electrical machine for excitation. The DC voltage is obtained by means of either a thyristor-made or IGBT-made static rectifier supplied by a three-phase transformer from auxiliary services, allowing to regulate the voltage applied to the main rotor by means of brush and ring connection. This solution presents benefits compared to the dynamo solution: reduction of axial machine size, higher reliability and greater yield.

Figure 1.3.3: Static excitation block scheme [1].

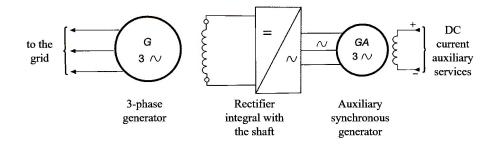

#### **1.3.3 Brushless excitation**

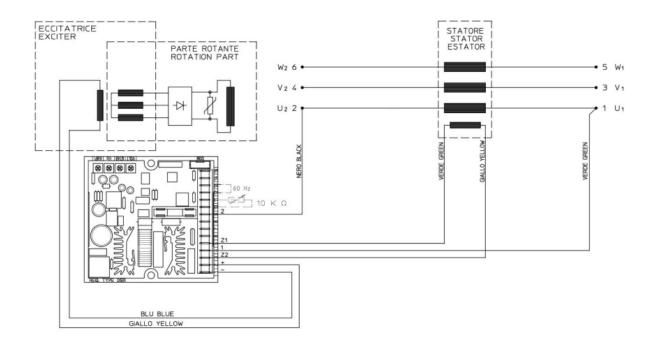

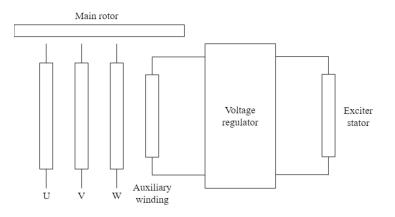

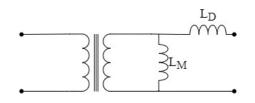

Another kind of rotating excitation, but avoiding the use of brushes, is the one shown in Fig. 1.3.4. An auxiliary generator, called exciter, having opposite configuration with respect to the main generator (*fixed inductor* in the stator and a three-phase *rotation induced* in the rotor) is coupled coaxially with the main generator, rotating at same main rotor angular speed. Sinusoidal voltages induced on the exciter rotor supply a diode rectifier mounted on the main shaft. The resulting rectified voltage constitutes the excitation for the main rotor winding. Since all the connected parts rotate at the same angular speed, no brush and ring system is required. The auxiliary alternator in turn must be supplied by applying an appropriate constant voltage on the fixed inductor in the stator. Varying this parameter allows the regulation of the excitation voltage and current of the main machine. This excitation system is the one chosen by Mecc Alte for all the alternators in its catalogue that uses electromagnet excitation. This choice is made since the absence of sliding contacts avoids components wear and replacement, losses due to friction and undesirable formation of electric arcs, resulting in a more robust and long-lasting product.

Figure 1.3.4: Brushless excitation block scheme [1].

#### 1.4 The voltage regulator

It could be considered that the AVR (Automatic Voltage Regulator) is the brain of the synchronous generator and the core of the excitation system. In fact, it performs measurements and actions in order to maintain the correct alternator operation. As it is expected to do, a generator is needed to provide a constant AC voltage at its output terminals, independently of the load attached to it.

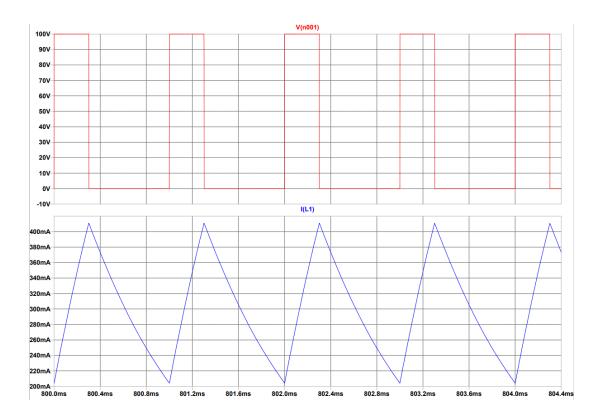

Figure 1.4.1: Excitation system block diagram from DSR digital regulator technical guide [22].

This control is performed by the voltage regulator, whose output consists of a pulsed voltage waveform that energizes the exciter stator, inducing on it a continuous current proportional to the signal voltage pulse duration. The magnetic field so produced by the exciter stator coils affects the amplitude of the AC voltage induced in the exciter rotor, that, after been rectified by the rotating diodes, feeds the main rotor windings by means of a proportional constant current. The resultant amplitude controlled rotating magnetic field produced in the field coils, linked by the main stator conductors, induces a proportional EMF at the output generator terminals. To complete the discussion, according to Eq. 1.0.1, it should be mentioned that the other parameter affecting the EMF is the rotational speed of the rotor. However, the real conditions in which a Mecc Alte alternator operates is under a constant rotor angular velocity im-

posed by the external mechanical energy source (a diesel engine). Being the derivative in time of the Faraday's law a non-controllable parameter the only possibility is acting on the intensity of the rotor magnetic field.

The excitation current regulation system has to satisfy the need of a very high operational safety level and a quick transient response. At a load connection or disconnection event, the terminal voltage undergoes a variation due to the armature reaction. In order to bring back the terminal voltage to the desired value, it will be necessary to act on the excitation current by increasing or decreasing the generated EMF. Moreover, the excitation system, in order to keep the voltage constant, must increase the excitation current in the case of inductive loads, while decrease it in the case of a capacitive load.

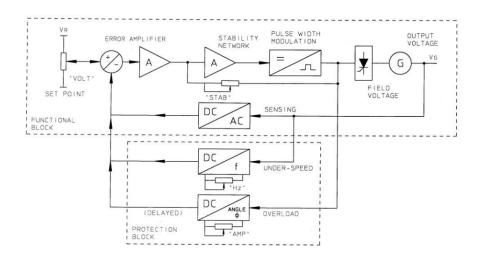

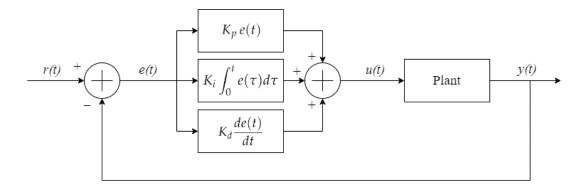

The circuit controlling and regulating the generated output voltage can be represented by the following block scheme.

Figure 1.4.2: Voltage regulation scheme [21].

It is possible to recognize two main blocks that make up the regulator:

- functional block;

- protection block.

#### 1.4.1 Functional block

This is a negative feedback system, in which the constantly maintained variable is the alternator voltage output. This voltage, after adequate conditioning, is compared with a reference signal (generated inside the electronic regulator) that is stabilized in voltage, temperature and age. The result is an error signal which, after being appropriately

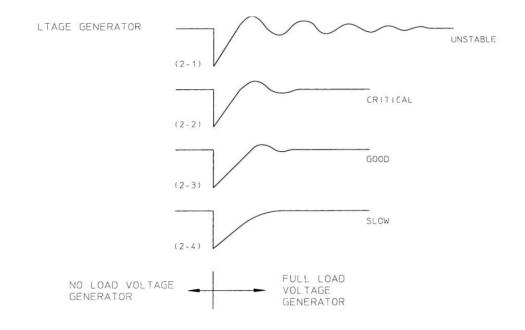

amplified and compensated, produces a control level that enters the regulator. The signal generated by the regulator will control the output terminal voltage as already explained. The set of the stability network is fundamental for the dynamic behaviour of the system. When the alternator undergoes sudden load variations, the presence of this part of the calibrated circuit makes it possible to improve system performance. System regulation with short reset time can keep the system in a stability limit condition. On the contrary, a highly stabilized and calibrated system could be too slow during the reset time.

#### **1.4.2 Protection block**

In addition to the error signal, additional inputs are sent to the regulator in order to enable protection features, that preserve the safe operation of the system. The two main monitored aspects are:

• Overload protection: in order to avoid damage to the conductors, prevent the maximum value of field current being exceeded. When the value of the continuous voltage that supplies the alternator inductor is higher than the value set by the threshold, a continuous time-delayed signal lowers the value of the alternator output voltage and limits the excitation current produced by the inductor, which guarantees safety margins for system operation. The intervention delay of this protection temporarily overloads the alternator without lowering the output

voltage to guarantee motor starting for example.

• Low frequency protection: when the frequency of the output voltage falls below the value of a given threshold, the output signal of this block produces a controlsignal which lowers the output voltage of the generator, in order to stop overexcitation (a typical example is the lowering of the speed for the preheating of the prime mover).

## Chapter 2

# Analysis of the current voltage regulator output stage

This chapter concentrates on the operation and realization of the output stage of the AVR. After a description of its working principle, the configuration currently used in Mecc Alte regulators will be exposed. Finally, a section detailing the limits of the actual design will introduce the next chapter about the company requirement and project development.

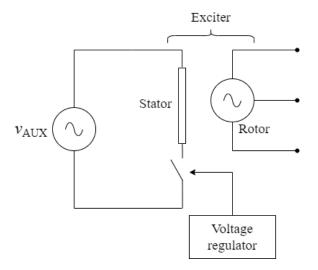

The reader should keep in mind that all the following discussion will be based on the brushless excitation system, as illustrated in Section 1.3.3.

#### 2.1 Switching inductive load

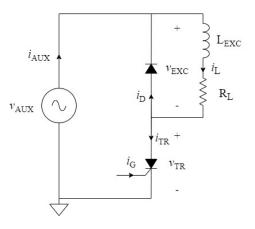

In Section 1.4 it has been mentioned that the regulator acts on the exciter stator current controlling the duration of a voltage pulsed waveform. In order to explain this phenomenon it is preferable to take as a reference the excitation scheme of Fig. 1.4.1, where the focus is posed only on the path connecting the auxiliary winding in the main stator to the exciter stator. This section of the excitation system is illustrated in the figure below.

Figure 2.1.1: Auxiliary to stator exciter winding path.

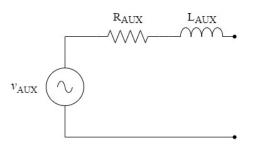

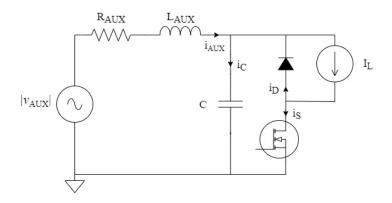

According to the brushless excitation block scheme the energy provided to the exciter stator comes from an auxiliary service. This is achieved by exploiting an additional main stator winding on which, in the same manner as the three phase coils, a voltage is induced according to Faraday's law. For this reason, this auxiliary winding can be represented in a first approximation as a sinusoidal voltage generator. The voltage imposed by the auxiliary generator is applied to the exciter stator by means of a switch, which receives the command from the voltage regulator logic. This way, a pulsed voltage waveform can be applied to the exciter stator.

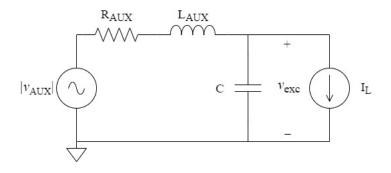

The aforementioned situation can be described by the following circuit-like scheme.

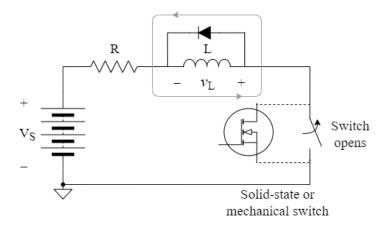

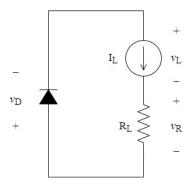

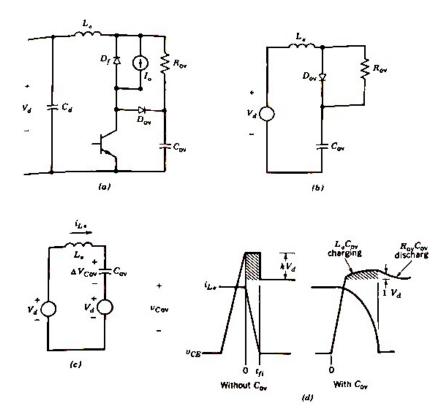

Figure 2.1.2: Voltage regulator working principle.

The application of a pulsed voltage to the exciter stator is not a trivial task since it hides problems due to the inductive nature of the exciter itself. In the two following paragraphs the switch theory of an inductive load is presented. The discussion is necessary to understand the complete output stage circuit, which will be presented later.

#### 2.1.1 Simultaneous dual switch - ideal case

Assuming to be in steady-state operation the pulsed voltage waveform applied to the exciter stator will induce a roughly constant current. This is because the exciter stator winding is of inductive nature. In particular, it can be modeled as an inductance L in series with a parasitic resistance R, accounting for the ohmic losses in the exciter stator conductor. The signal generated by the voltage regulator can instead be simply modeled by a constant voltage source in series with an ideal switch.

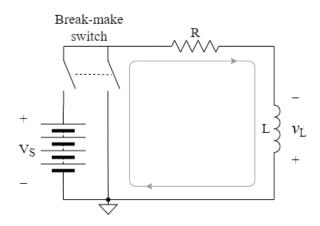

Figure 2.1.3: Circuit representing ideal inductive load switching.

The equation that relates voltage and current in an inductor is

$$v_L(t) = L \frac{di(t)}{dt} \tag{2.1.1}$$

When the switch is closed on the voltage source the Kirchhoff equation is

$$V_S - Ri(t) = L \frac{di(t)}{dt}$$

(2.1.2)

the current rises from 0 to  $V_S/R$  as

$$i(t) = \frac{V_S}{R} \left( 1 - e^{-t\frac{R}{L}} \right)$$

(2.1.3)

and the inductor voltage decays to zero volts according to

$$v_L(t) = V_S e^{-t\frac{K}{L}}$$

(2.1.4)

When the switch instantly connects the RL series to a short circuit the Kirchhoff equation becomes

$$-Ri(t) = L\frac{di(t)}{dt}$$

(2.1.5)

the current drops to zero as

100V 90V 80V 70V 60V 50V 40V 20V 10V 0V -10V

$$i(t) = \frac{V_S}{R} e^{-t\frac{R}{L}}$$

(2.1.6)

and the voltage across the inductor instantly reverses to  $-V_S$  and increases towards zero volts according to

$$v_L(t) = -V_S e^{-t\frac{R}{L}}$$

(2.1.7)

When the voltage source is disconnected to the load the reverse voltage spike across the inductor is constrained in amplitude to  $-V_S$  (a benefit of simultaneous switching). In fact, at the switching instant the broken inductor current path is replaced with an alternate one.

V(n001)

I(L1)

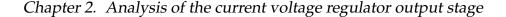

Figure 2.1.4: LTspice simulation: V(n001) inductor voltage  $v_L$ , I(L1) inductor current  $i_L$  in steady state for ideal switching case.

The above figure shows an LTspice simulation of the above circuit with  $V_S = 100V$ , L = 0.1 H,  $R = 100 \Omega$  and a switching frequency of 1 kHz, with a 30% duty cycle. The continuous switching activity makes the current stabilizing around an average value that depends on the duration of the voltage pulses.

#### 2.1.2 Single switch - real case

Actually a simultaneous dual switch is very difficult to implement. It is more likely that there would be a small gap time between the individual break and make switches that would result in a transient voltage spike greater than  $V_s$ , which could possibly drive an arc in the circuit. The inductor voltage spikes very quickly and gap time must be very fast or nearly zero.

More commonly inductors are switched on and off using an electro-mechanical or solid-state device that simply opens and closes the circuit to the inductor. However, the switching of inductive loads deserves special attention because this operation may lead to high-voltage transients that can damage the equipment.

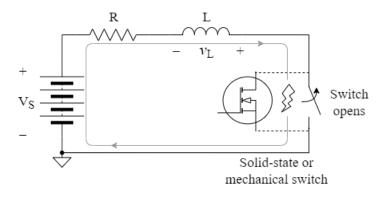

Let's now take the example of the circuit in the figure below. It comprises the same inductor L and resistor R connected to a voltage source  $V_S$  through a switch.

Figure 2.1.5: Circuit illustrating the issue with real inductive load switching.

Suppose that the switch is initially connected, and a given current  $I_0 = V_S/R$  flows through the resistor and the inductor. This time, when the current path from the source is broken, no alternate path for the discharge current is introduced. The inductor resists an instant change its current from  $I_0$  by instantly imposing a rapid reverse voltage across it that reinforces current flow in the inductor in the same direction as before the switch opened. The physical reason of this phenomenon is that the energy stored by the inductor (in the form of a magnetic field) must be abruptly released when its current vanishes. Upon discharging, the voltage across the inductor instantly reverse to an unpredictable  $-V_x$  (depending on the rate of drop of the current) and increases towards zero volts according to

$$v_L(t) = -V_x e^{-t\frac{K}{L}}$$

(2.1.8)

The negative voltage spike will go to whatever reverse amplitude is required to complete the current path that reinforces the initial steady-state inductor current prior to the switch opening. This high reverse voltage spike, if left unconstrained, can cause significant damage to any circuitry along the circuit path. For control via a mechanical switch, an arc may occur as the switch is being gapped open, eventually fouling its contacts, or the relay coil may arc over to metal inside the relay, like its armature. For a solid-state MOSFET switch, the high voltage reverse spike can destroy the switch. Moreover, a voltage spike distributed along the wiring between the switch and the load may generate noise in adjacent circuits by radiating or inductively coupling into adjacent conductors.

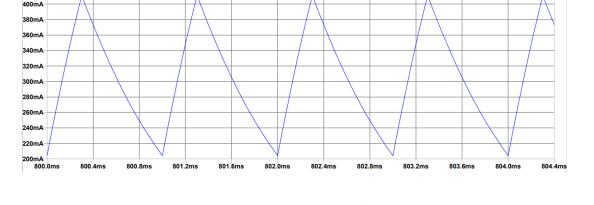

Figure 2.1.6: LTspice simulation: V(n002,N003) inductor voltage  $v_L$ , I(L2) inductor current  $i_L$  in steady state for real switching case.

The above waveforms are produced by simulating the circuit of Fig. 2.1.5, starting

from the same parameters as before. It's possible to notice the extremely high reverse voltage peaks across the inductive load at switch turn-off events.

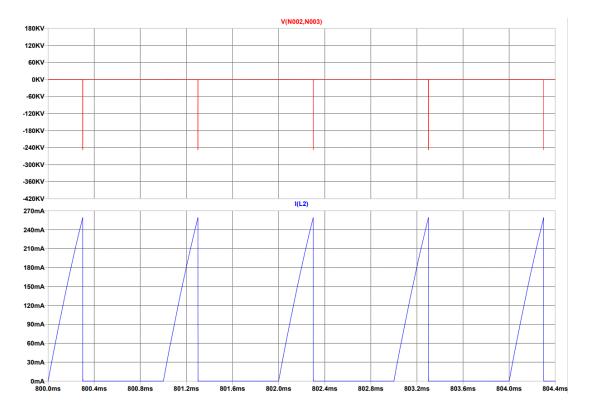

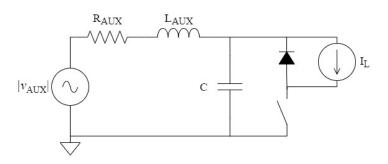

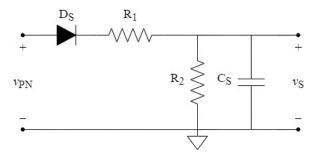

A common solution to curb destructive switching transient voltage is illustrated in Figure 2.1.7. It requires a diode (known as freewheeling diode) in parallel with the inductive load.

Figure 2.1.7: Circuit for real case switching including the freewheeling diode.

When the switch is closed, the diode is reverse-biased and therefore it does not effect the circuit. As the switch is opened, an alternate path for discharge current is present by placing the diode near the load. The voltage across the inductor instantly reverses to  $v_L(t) = -V_D e^{-t\frac{R}{L}}$  but the magnitude  $V_D$  is clamped to the forward voltage drop of the diode. The stored energy  $W_L = \frac{1}{2}LI_0^2$  in the inductor is instead dissipated via heat through the resistance of the coil-diode circuit.

The following figure shows the absence of reverse peaks at switch turn-off due to the freewheeling diode presence. The waveforms are comparable with the ones of Fig. 2.1.4.

Figure 2.1.8: LTspice simulation: V(n001) inductor voltage  $v_L$ , I(L1) inductor current  $i_L$  in steady state for real switching case where a freewheeling diode is used.

It is usually recommended to add the freewheeling diode at the load even though solid-state switching devices like MOSFETs actually include a source-drain built-in diode that could shunt voltage spikes. However, building this protection local to the load being switched is important because it prevents the transient from being distributed along the wiring between the switch and load. To place it anywhere else would not be as effective and would allow the transient energy to move along the wiring back to the switch, radiating or inductively coupling noise into adjacent wiring and other devices, and possibly damaging the switch. Moreover, taking care of the switching device by avoiding stresses in excess of the nominal rating results in a higher operation reliability over time.

### 2.2 Current Mecc Alte voltage regulator output stage implementation

At this point, after having explained the basic theory of inductive loads driving, it is possible to present the current Mecc Alte implementation of the voltage regulator

output stage and in particular the device used to enable the exciter inductor driving.

Figure 2.2.1: Block diagram of DSR Mecc Alte regulator [22]. In the red rectangle the output stage of the voltage regulator.

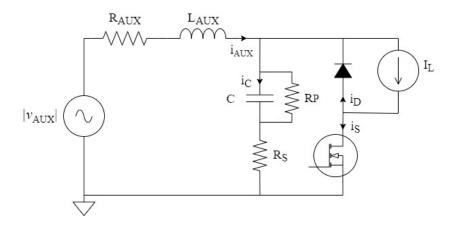

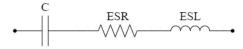

Such output stage can be fully described by the elements presented in the following circuit.

Figure 2.2.2: Current voltage regulator output stage implementation via thyristor.

The reader can recognize this circuit configuration is directly derived from the scheme of Fig. 2.1.2. It is possible to notice the auxiliary winding supply, represented as a voltage generator, on the right and the exciter stator represented as a *RL* series.

The freewheeling diode in parallel to the inductive load is placed as explained in Section 2.1.2. The switch consists of a thyristor that receives the gate command from the voltage regulator logic. A brief explanation of thyristors behaviour (Section 2.2.1) is necessary to understand how they can be used to operate the inductive load driving and therefore to regulate the current flowing through the exciter stator (Section 2.2.2). Finally, a short section about the limits of this implementation will introduce the next chapter.

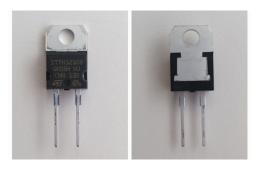

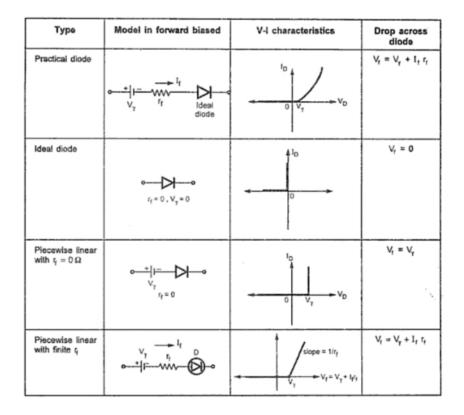

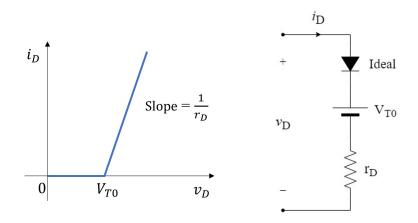

#### 2.2.1 Thyristors

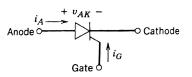

Thyristors (sometimes termed SCRs, meaning semiconductor-controlled rectifiers) are one of the oldest types of solid-state power device and still have the highest powerhandling capability. They are a latching switch that can be turned on by the control terminal (gate) but cannot be turned off by the gate.

Figure 2.2.3: Thyristor circuit symbol [2].

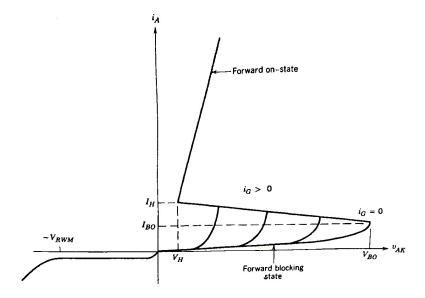

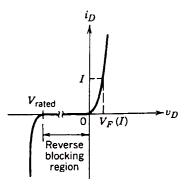

The thyristor *i*-*v* characteristic (anode current  $i_A$  as a function of the anode-tocathode voltage  $v_{AK}$ ) shows the device operation.

Figure 2.2.4: Thyristor current-voltage characteristic [2].

In the reverse direction the thyristor appears similar to a reverse-biased diode, which conducts very little current until avalanche breakdown occurs at  $V_{RWM}$ . In the forward direction the thyristor has two stable states of modes of operation that are connected together by an unstable mode that appears as a negative resistance on the *i*-*v* characteristic. The low-current, high voltage region is the forward-blocking state or the off-state, and the low-voltage, high current mode is the on-state.

Specific voltage and current values in the forward-bias quadrant of the *i-v* characteristic are of interest because they discriminate the regions of operation. The holding current  $I_H$  represents the minimum current that can flow through the thyristor and still maintain the device in the on-state. This current value and the accompanying voltage across the device, termed the holding voltage  $V_H$ , represent the lowest possible extension of the on-state portion of the *i-v* characteristic. For the forward-blocking state, the quantities of interest are the forward-blocking voltage  $V_{BO}$  (also termed breakover voltage because the *i-v* curve breaks over and goes to the on-state portion of the characteristic) and the accompanying breakover current  $I_{BO}$ .

The breakover voltage and current are defined for zero gate current, that is, the gate is open-circuited. If a positive gate current is applied to the thyristor, then the transition or breakover to the on-state will occur at smaller values of anode-to-cathode voltage, as indicated in Fig. 2.2.4. As shown in this figure, the thyristor will switch to the on-state at low values of  $v_{AK}$  if the gate current is reasonably large. Although not indicated on the *i*-*v* characteristic, the gate current does not have to be a DC current, but instead can be a pulse of current having some minimum time duration. This ability to switch the thyristor on by means of a current pulse has been the basis of the widespread applications of the device.

However, once the thyristor is in the on-state, the gate cannot be used to turn the device off. The only way to turn-off a thyristor is for the external circuit to force the current through the device to be less than the holding current for a minimum specified time period.

#### 2.2.2 Circuit operation

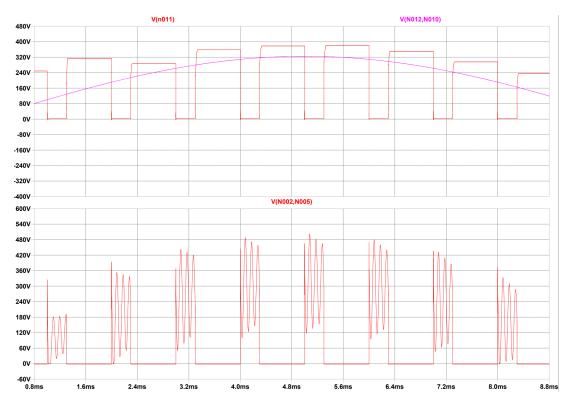

Taking as a reference the circuit of Fig. 2.2.2 it is possible to show the operation of the circuit.

The steady-state condition is assumed: this means the switching activity makes the current flowing through the exciter stator (modeled as the series *RL*) to be a constant value equal to the average superimposed to a periodic ripple, as already seen in Section 2.1.1.

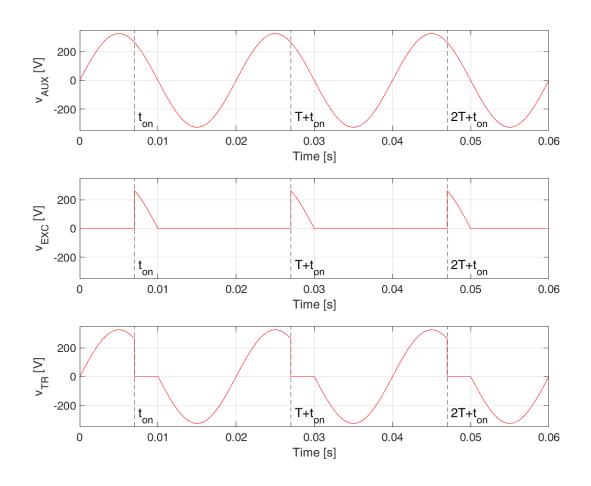

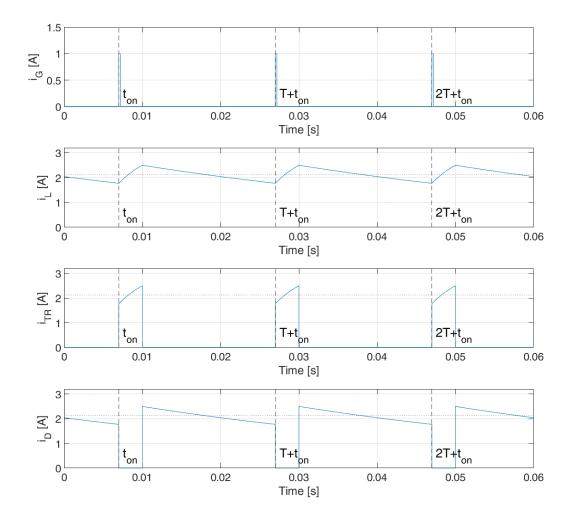

Figure 2.2.5: Voltages in the circuit.

Figure 2.2.6: Currents in the circuit.

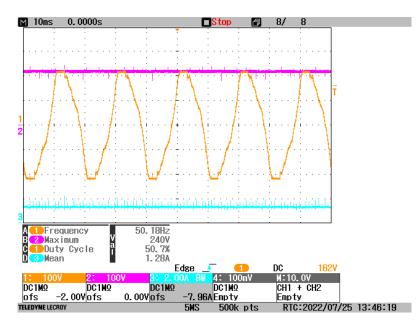

For the sake of illustration the plotted waveforms are produced considering the following parameters: auxiliary waveform having a frequency of f = 50 Hz and a root-mean-square voltage of  $V_{AUX}^{rms} = 230 V$ ; the thyristor trigger angle is  $\alpha = 54^{\circ}$  and the exciter stator parameters are  $L_{EXC} = 0.5 H$  and  $R_L = 10 \Omega$ .

The auxiliary winding represented by an equivalent voltage generator applies a sinusoidal waveform between the nodes *A* and *B* of the circuit.

Focusing firstly on the half period in which the auxiliary voltage assumes positive values [nT, nT + T/2] (*T* is the sinewave period and *n* a positive integer counter). Until a current pulse is not given to the thyristor gate terminal, the thyristor is in its off-state and can be approximated as an open circuit. The path for the current through the inductive load is provided by the freewheeling diode, that can be seen as a short

circuit in a first approximation. According to the *RL* series switching theory expressed in Section 2.1 in this considered time interval the current decreases exponentially with the time constant  $\tau = L_{EXC}/R_L$ . Thus voltages and currents in the circuit are:

$$\begin{cases}

v_{EXC} = 0 V \\

v_{TR} = v_{AUX} \\

i_L = i_D \\

i_{TR} = i_{AUX} = 0 A

\end{cases}$$

(2.2.1)

As a current pulse is given to the gate terminal of the thyristor at instants  $nT + t_{on}$  the device breakovers to the on-state. Now the thyristor, behaving like a diode, can be approximated as a short circuit and the current  $i_L$  flows through the thyristor to close the loop on the "auxiliary" generator. The freewheeling diode, on the other side, turns off since the current is no longer flowing through. Since now the inductance is connected to a voltage generator by means of a resistor, the inductor current  $i_L$  grows exponentially according to the same time constant  $\tau$ . In this time interval voltages and currents in the circuit are:

$$\begin{cases} v_{EXC} = v_{AUX} \\ v_{TR} = 0 V \\ i_L = i_{TR} = i_{AUX} \\ i_D = 0 A \end{cases}$$

(2.2.2)

As the auxiliary voltage reverses to negative values (during the second half period of the sinewave) the thyristor returns to the off-state. If, as assumed thus far, the thyristor in its on-state can be approximated as a short circuit, at instants  $nT + T/2 + \epsilon$  the auxiliary voltage reverses and forward polarizes the freewheeling diode, turning it on. The current continuously flowing in the inductive load is forced to close the loop through the freewheeling diode. The absence of current in the thyristor makes it turn-off, as explained in Section 2.2.1. The situation is similar to the first analyzed interval: the freewheeling diode being a short circuit and the thyristor an open circuit, the voltages and currents assume the same values of system of Eq. 2.2.1. The inductor current *i*<sub>L</sub> returns to exponentially decay like in the first analyzed time interval.

Up to now it has been explained that a thyristor is able to "cut" the sinewave voltage coming from the auxiliary winding and apply the voltage pulses to the exciter stator. Due to the inductive nature of the load, it is possible to induce on it a periodic current that, except for the superimposed ripple, has a constant value.

At this point, of the discussion it's clear that acting on the trigger angle  $\alpha$ , by which current pulses are sent to the gate terminal of the thyristor, has a direct impact on the average current  $I_L$  flowing in the exciter stator. Using the model considered so far it is possible to derive the relation  $\alpha$ - $I_L$ . Since it is assumed to be in steady state condition and the focus is on the mean value of the current (no interest in the ripple), the volt-second balance principle can be applied to the inductance  $L_{EXC}$ . In switch-mode power conversion circuits "volt-second balance" refers to the fact that over one complete switching cycle the total volt-seconds applied to an inductor must be zero (in steady state):

$$\int_{t}^{t+T} v_{L}(\tau) d\tau = \int_{t}^{t+T} L_{EXC} \frac{di_{L}(\tau)}{d\tau} d\tau = L[i_{L}(t+T) - i_{L}(t)] = 0$$

(2.2.3)

because of the periodicity of current  $i_L$ . For this reason, no voltage drops on the inductor in average value.

The average value  $V_{EXC}$  of  $v_{EXC}$  is going to fall all across the resistor terminal. Looking at the circuit of Fig. 2.2.2:

$$v_{EXC} = v_L + v_R \tag{2.2.4}$$

Taking the averages over the period T:

$$\int_{t}^{t+T} v_{EXC}(\tau) d\tau = \int_{t}^{t+T} v_{L}(\tau) d\tau + \int_{t}^{t+T} v_{R}(\tau) d\tau$$

(2.2.5)

$$V_{EXC} = V_L + V_R \tag{2.2.6}$$

$$V_{EXC} = V_R \tag{2.2.7}$$

Furthermore, the average current on the exciter  $I_L$  will be the average current flowing in the resistor, so  $I_L = V_R/R_L$ .

On the other side voltage  $V_{EXC}$ , being the average value of the voltage applied to the *RL* series, can be computed as a function of the trigger angle and the sinewave auxiliary voltage.

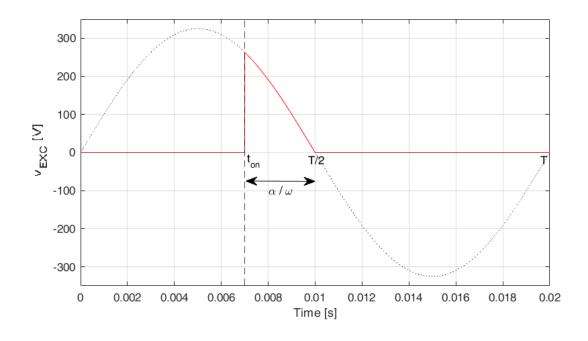

Figure 2.2.7: Exciter voltage.

The calculation is the following:

$$V_{EXC} = \frac{1}{T} \int_{t_{on}}^{T/2} v_{AUX}(\tau) d\tau = \frac{1}{T} \int_{t_{on}}^{T/2} \sqrt{2} V_{AUX}^{rms} \sin(\omega\tau) d\tau = \frac{V_{AUX}^{rms}}{\sqrt{2}\pi} \Big[ 1 + \cos(\omega t_{on}) \Big]$$

(2.2.8)

that, in terms of  $\alpha = \omega \left(\frac{T}{2} - t_{on}\right)$ , can be reduced to

$$V_{EXC} = \frac{V_{AUX}^{rms}}{\sqrt{2}\pi} \left[ 1 + \cos(\pi - \alpha) \right]$$

(2.2.9)

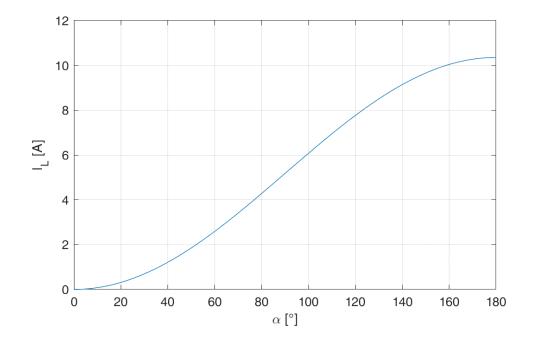

Finally, the relation  $\alpha$ - $I_L$  is found:

$$I_{L} = \frac{V_{R}}{R_{L}} = \frac{V_{AUX}^{rms}}{\sqrt{2}\pi R_{L}} \Big[ 1 + \cos(\pi - \alpha) \Big]$$

(2.2.10)

Figure 2.2.8:  $\alpha$ - $I_L$  relation.

#### 2.2.3 Limits

As shown in the previous section, an output stage for a voltage regulator involving thyristors functions to enable control on the current flowing in the exciter stator and thus consequently on the voltage induced in the exciter rotor and finally the current in the main rotor. However, this configuration brings with it some as yet undiscussed aspects that make the utilization of thyristors more complex than one would expect on a first approach to the problem.

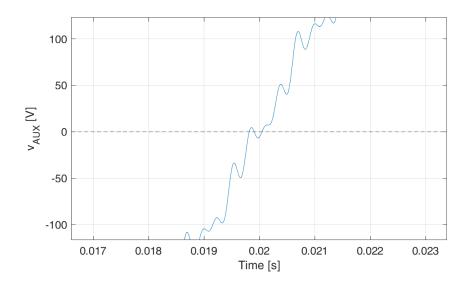

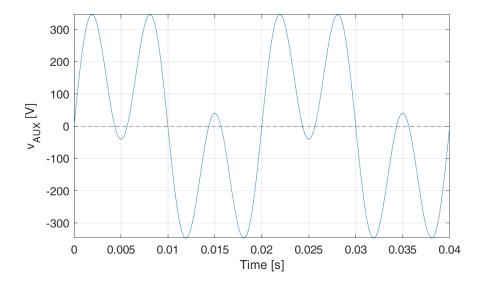

The first aspect is linked to the fact that the current pulse needs to be given to the gate terminal of the thyristor at the desired trigger angle within the first half period of the waveform generated by the auxiliary winding. This means the regulator logic needs firstly to "synchronize" on the auxiliary waveform and then to compute the time interval after which the current pulse to the gate terminal must be applied. Synchronization means that the regulator must recognize the waveform zero crossings. This activity needs the execution of a custom algorithm, typically implemented in the regulator microcontroller. This would not require an excessive effort, if not for the fact that the auxiliary voltage results not to be an ideal sinewave. Instead, due to noise, the waveform undergoes multiple zero crossings.

Figure 2.2.9: Extra zero crossings in auxiliary winding voltage waveform.

A further aspect that makes the synchronization problem a non-trivial task is that the auxiliary winding is arranged in the main stator in such a way that the induced EMF is not even expected to be a sinusoidal waveform. Actually the auxiliary voltage presents a significant third harmonic content, needed to satisfy the short circuit operation requirement, of which a more detailed discussion will be provided in the next chapter. It is possible that in some working conditions the third harmonic content is so high that the auxiliary voltage undergoes extra zero crossing that mustn't be accounted for the synchronization task, adding complexity to the algorithm.

Figure 2.2.10: Auxiliary winding voltage waveform having a third harmonic content which causes extra zero crossings.

It has to be specified the microcontroller firmware developed by Mecc Alte solves the issues related to synchronization. An appropriate strategy to recognize and discard extra zero crossings due to noise and third harmonic amplitude, based on a series of filters and time windows, is currently used in the company AVRs. However, a much simpler implementation of the microcontroller firmware would be sufficient in the case if synchronization was not required and the way the gate command is given to the device was independent of the waveform generated by the auxiliary winding.

A second aspect of placing a limit on the circuit implementation involving thyristors is the missing exploitation of the negative half period auxiliary voltage to drive the exciter stator. The reader may have noticed that the trigger angle can only span the range  $[0^{\circ}, 180^{\circ}]$ . This prevents the utilization of the energy carried by the waveform in the second half period. The energy of a voltage waveform is in fact linked to the square of the voltage itself, making the energy in a period equally divided in the two half periods. This means that the utilization of thyristors to implement the power stage of the regulator gives the disadvantage of losing half of the energy that is specifically generated in order to energize the excitation system. A diode bridge to rectify the sinusoidal waveform could potentially remove this issue, since the negative voltage half period would reverse to positive values and be exploited like first half period. However, it should be remembered that a diode bridge cannot be used since the thyristor in the considered circuit can turn-off only if the anode-to-cathode voltage reverses. Otherwise there would be a situation in which the thyristor, after the first breakover to the on-state, would remain forever turned on, losing the control of the current  $I_L$ .

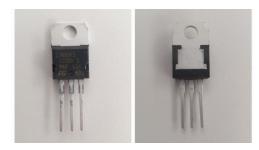

As discussed, the choice to use thyristors in order to implement the output stage of the voltage regulator, brings with it some disadvantages that could actually be removed if the thyristor was substituted by a both turn-on and turn-off controllable power switch, like a power MOSFET or IGBT.

## Chapter 3

# Development of the voltage regulator output stage circuit

This chapter is the core of the thesis. The actual development of the circuit, from the company requirements and the component selection, through the circuit simulation, the faced issues and the proposed solutions until the actual circuit production are discussed in Chapter 3.

## 3.1 Company request

It should be remembered that this thesis comes from an internship activity at Mecc Alte. The objective of this internship is to investigate an alternative approach, with respect to thyristor, to drive the exciter stator for the synchronous generator voltage regulator. The output stage used in regulators up to the present day is of course working well on the whole wide range of available alternators. However, the utilization of a both turn-on and turn-off controllable power switch takes with it many advantages, some of them mentioned at the end of the last chapter, that will be discussed and summarized in the conclusion chapter.

## 3.2 **Project specification**

The project specification is fundamental as the first step of project flow because it provides the design input needed to develop the project.

Since the circuit developed in this activity must deal with the same synchronous generators currently controlled by the regulator implemented via thyristor, the project

specification, on which the design is based, is almost identical. Even if this thesis activity could potentially be exploited to study and realize a higher-performing stage (in terms of providing higher exciter stator current values from lower auxiliary voltage levels), this would not make sense because the upstream decision was that the proposed regulator output stage is designed to be backwardly compatible to fit existing Mecc Alte products. These machines are designed to sustain up to a certain amount of current through their conductors and going beyond such bounds would be counterproductive because of magnetic saturation and windings overheating.

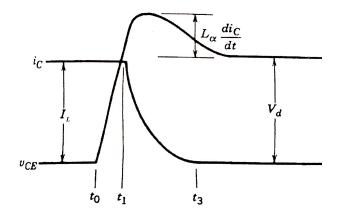

The meaningful project specification for this application, that consists of the worstcase scenario, in terms of stresses, the circuit has to deal with, are:

- the maximum peak value of the input alternating voltage provided by the auxiliary winding: V<sub>peak</sub> = 450 V. This value matches the voltage rating of the electronic components mounted on the voltage regulator board;

- the nominal RMS value of the auxiliary voltage in steady condition:  $V_{AUX}^{rms} = 230 V$ ;

- the maximum constant current that must be provided to the exciter stator:  $I_L = 6.5 A$ .

As regards the voltage specifications, it should be remembered that the waveform produced by the auxiliary winding is not a pure sinewave but contains an important third harmonic content needed to guarantee the correct machine operation in a particular working condition, that is the short circuit test. The reason for this is explained in greater depth in Subsection 3.2.1. The RMS and the peak values of such voltage are not dependent only on the machine, but also on the load connected to the alternator. The armature reaction induced by the load has, among its effects, the effect of raising and distorting (in the sense of modifying the harmonics amplitudes) the auxiliary voltage waveform. The voltage design inputs reported above are a consequence of such considerations.

With regards to the maximum exciter stator current a similar analysis is used. The current that needs to flow through the exciter stator, in addition to being dependent on the kind of machine, is extremely prone to the effects of a load attached to the generator. In fact, the armature reaction that is generated when a load is connected to the generator, modifying the total magnetic flux linked to the main stator windings, has a direct impact on the current requested to flow through the exciter stator. In particular, the armature reaction induced by an inductive or resistive load requires an increase in the exciter stator current to be able to maintain the output voltage at the

nominal value. In the uncommon capacitive load case, instead, a smaller current value would be sufficient. Despite the typical increase in requested current due to the load connection, the situation involving the maximum current is the *short circuit* test, briefly described in the following subsection.

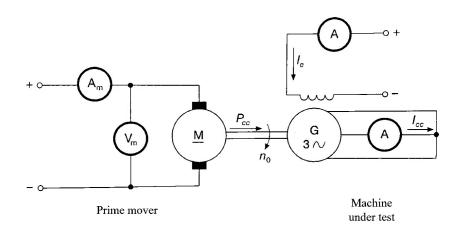

#### 3.2.1 Short circuit test

The short circuit test on the synchronous machine has two goals:

- the determination of the short circuit machine characteristics, that is the current provided short circuiting the phases as a function of the excitation current;

- the measurement of the conductor losses for efficiency evaluation.

Figure 3.2.1: Short circuit test scheme for the synchronous machine [1].

The excitation current is regulated by acting on the current flowing through the exciter stator, as already explained.

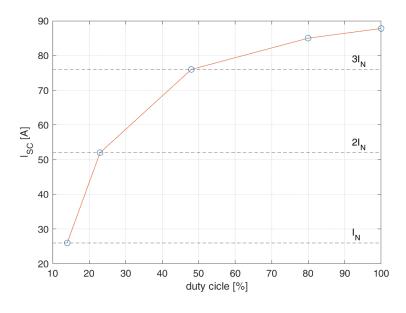

The reader should know a particular legislation regarding synchronous generators for marine application requires each synchronous generator to be able to provide a short circuit current  $I_{SC}$  equal to three times the machine nominal current  $I_N$ . The peaks of current and torque the machine is subjected represent the highest mechanical and electrical stresses, which allow also to assess the ability of the alternator to supply large inductive loads, like motors.

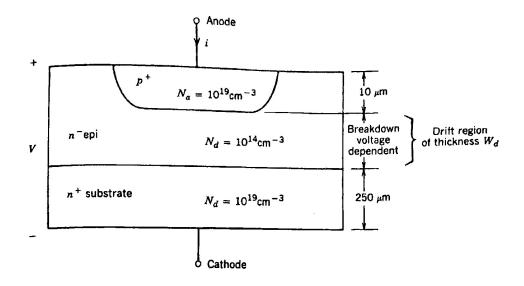

A non-trivial consequence of generator short circuit operation is the effect on the auxiliary winding induced waveform. Unlike the main three phases, which feature almost null voltages because short circuited, the auxiliary winding, which is an extra winding electrically isolated from the ones that make up the three phases, continues to present an induced voltage at its terminals. However, this induced waveform is strongly affected by the armature reaction manifesting in the short circuit situation. In the case of large load, like the short circuit, the generator works in "strong desaturation" condition: the excitation system provides the highest excitation current possible; at this point the first harmonic of each stator winding alternating voltage is gradually attenuated (also the auxiliary one). For this reason, it is necessary to design an auxiliary winding having a geometric arrangement such that the energy induced is not concentrated only in the first harmonic, but also in higher order harmonics. This is the reason why the auxiliary winding is rearranged in such a way the induced voltage is rich in third harmonic content. During the short circuit test the third harmonic is the only one surviving and providing the energy to use in order to drive the exciter stator and energize the excitation system.

Among every possible functional situation a synchronous generator can face up to, it is known that reaching  $3 \cdot I_N$  during the short circuit test is the worst-case scenario for the excitation system in terms of current that has to be flow through the exciter stator, even more than the fully-demagnetizing case of the purely inductive load.

## 3.3 Circuit development

This section is intended to give to the reader a detailed explanation about the project development process: the justifications for the design choices, the encountered issues, the solution attempts and the reasons for their failures and the final solution chosen. The starting point is the willingness to substitute the thyristor with both a controllable

turn-on and turn-off power switch, typically a power MOSFET or IGBT. The reason for this choice has already been explained in Subsection 2.2.3 about the limits of the regulator output stage implementation via thyristor. The use of a power MOSFET or IGBT is able to provide advantages, some explained in such subsection, others presented later on as the thesis discussion is developed. From this point on the reader

can appreciate the design steps that have characterized the development of the project. The submission order of such steps is the same logical order with which it has been addressed to propose the solution for this problem.

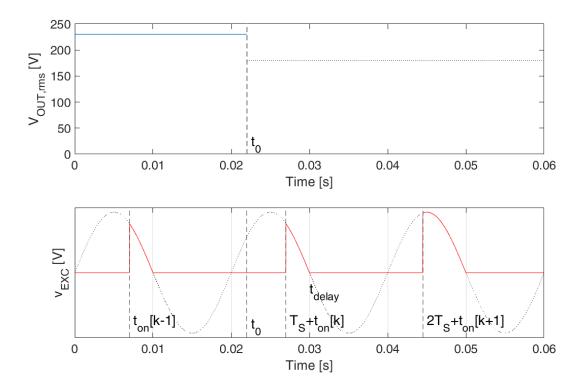

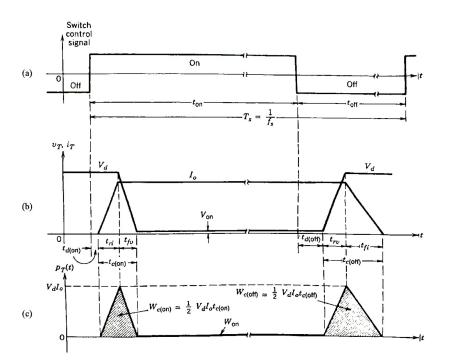

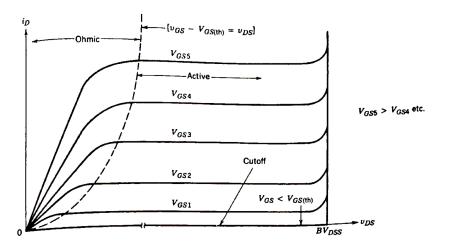

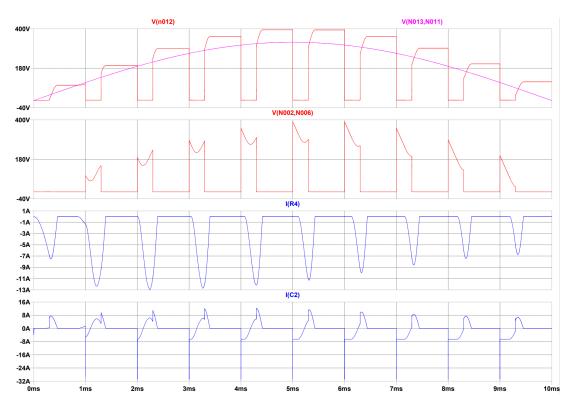

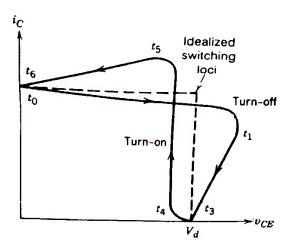

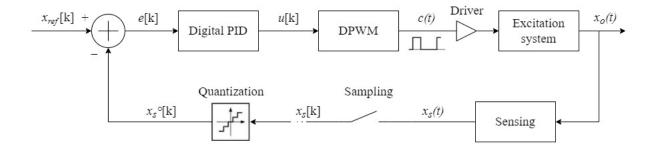

#### 3.3.1 Switching frequency

The first design choice regards the controllable power switch commutation frequency on which the exciter stator current regulation is performed. Differently from the thyristor, whose switching frequency is forced to coincide with the 50 Hz alternating auxiliary waveform frequency, in the case of both a controllable turn-on and turn-off switch it is possible to uncouple from the characteristics of such supply waveform. For this reason, the designer has the freedom to choose the appropriate operating frequency, of course within the limits set by physical properties of commercially available devices.

**Regulation velocity** Since the driving frequency of the inductive load is not forced to be 50 Hz any more, there is a clear advantage in raising the switching frequency because of a direct impact on regulation velocity. In fact, operating at 50 Hz allows to update the trigger angle once every switching period  $T_S = \frac{1}{f_S} = 20 \, ms$ . This may be critical in transient events, for example in a load connection or disconnection: at the instant such event happens, the generator output voltage undergoes a step in its value due to armature reaction phenomenon, linked to the kind of load supplied by the machine. Even making two assumptions: the first being the firmware uploaded on the regulator microcontroller performing a continuous sampling activity on the output voltage sensed signal and so recognizes immediately a difference between the setpoint and the sensed value; the second being the instantaneous microcontroller execution of the control algorithm for computation of the regulator output (the command for the switch), one must wait till the next switching period  $T_S$  before applying the latest updated trigger angle. No command can be sent to the switch before the next period because the regulator logic has to recognize a new zero crossing determining a new period from which to wait for the trigger event. This places an upper limit on the regulation velocity, that could be improved if the switching period was reduced.

Figure 3.3.1: Evidence of delay time from load connection at  $t_0$  to the next switching period, when a new command to the switch can be applied.

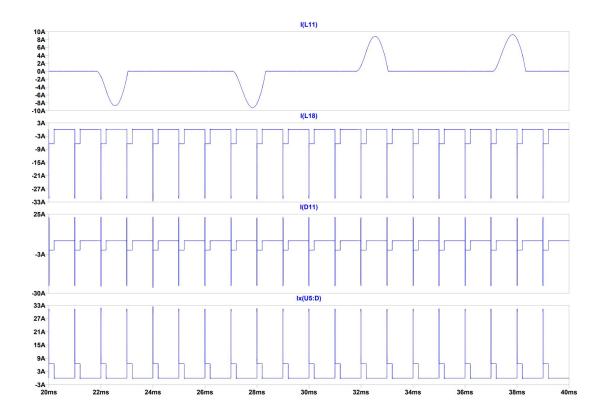

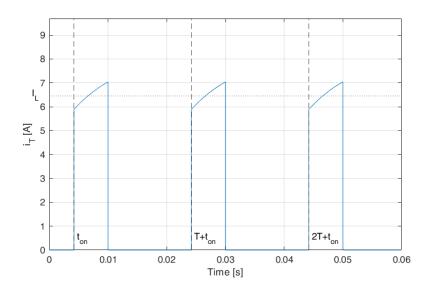

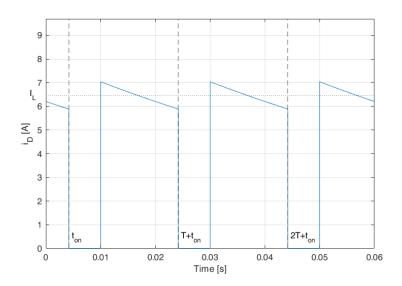

**Exciter stator current ripple** Another reason to increase the switch commutation frequency regards its effect on the inductive load current waveform. As described in Section 2.2.2 the application of a pulsed voltage waveform to an inductive *RL* load generates a periodic current characterized by a constant value superimposed on a ripple. Such a ripple acts as undesired noise in the excitation system chain: an oscillating current through the exciter stator generates an oscillating magnetic field, that induces non-sinusoidal EMF on exciter rotor windings and a less constant current on the main rotor electromagnets. Eventually the effect is to distort the synchronous generator output voltage to a non-ideal sinewave. Where possible, it is always better practice to reduce upstream any possible source of disturbance. Increasing the switch commutation frequency allows the reduction of the current ripple amplitude. In fact, as will be demonstrated, its value is inversely proportional to the switching frequency.

The value of the current ripple  $\Delta I_L$  can be computed looking either at the switch on or off phase. For example, looking at the off phase it is recalled the switch can be seen as an open circuit, while the path for the current through the inductive load is provided by the freewheeling diode, that can be seen as a short circuit. In the off period the inductive load switching circuit illustrated in Fig. 2.1.7 is simplified by the following circuit:

Figure 3.3.2: Equivalent circuit during the thyristor off phase.

For the sake of computation a constant current equivalent to the average value is assumed to flow in the circuit. The voltage across the inductor  $v_L$  is shown to be the reverse of the sum of the voltage drop across the parasitic resistance  $v_R = R_L \cdot I_L$ plus the voltage drop on the diode, negligible in a first approximation. Given  $t_{off} =$  $(1 - d) \cdot T_S$  the off phase time duration, With these assumptions the current will vary linearly in time, producing a current ripple equal to

$$\Delta I_L = \frac{v_L}{L} t_{off} = \frac{R_L \cdot I_L}{L} (1-d) \cdot T_S = \frac{R_L \cdot I_L}{L} \frac{(1-d)}{f_S}$$

(3.3.1)

After having shown the current ripple amplitude dependence on the switch commutation frequency, it is clear the best choice would be to raise the frequency as much as possible to obtain small current ripple. However, in addition to the physical limits of on the market power switches to reach arbitrary high frequencies, another reason preventing the choice of very high frequencies is shown below. **Switching losses** An ideal switch is represented in a generic manner by the circuit symbol shown in Fig. 3.3.3. No current flows when the switch is off and, when it is on, current can flow in the direction of the arrow only.

Figure 3.3.3: Generic controllable switch [2].

The ideal controllable switch has the following characteristics:

- block arbitrarily large forward and reverse voltages with zero current flow when off;

- conduct arbitrarily large currents with zero voltage drop when on;

- vanishingly small power required from control source to trigger the switch;

- switch from on to off or vice versa instantaneously when triggered.

Real devices, as intuitively expected, do not have these ideal characteristics and hence will dissipate power when they are used. In particular, the non-ideality in the instantaneous switch from one state to the other is an important factor that could make the device dissipate too much power, leading to its failure and, in doing so, the damage of the other system components.

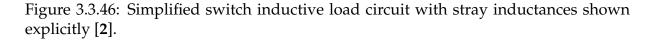

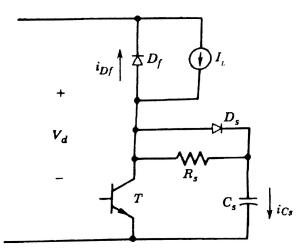

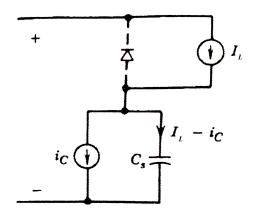

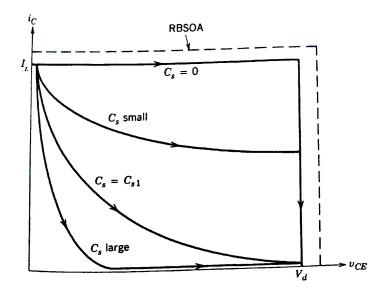

In order to explain the link between the switching frequency and the switching power losses, a simplified version of the inductive load drive circuit is considered, shown below.

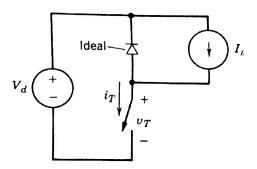

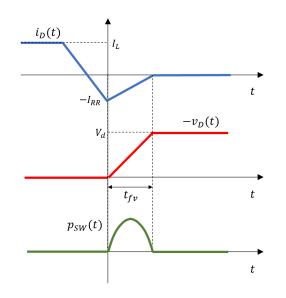

Figure 3.3.4: Simplified version of inductive load drive circuit [2].

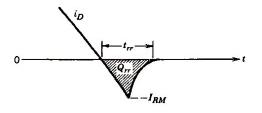

The DC current source approximates the current that would actually flow due to inductive energy storage. The diode is assumed to be ideal because the focus is on the switch characteristics, though in practice the diode reverse-recovery current can significantly affect the stresses on the switch.

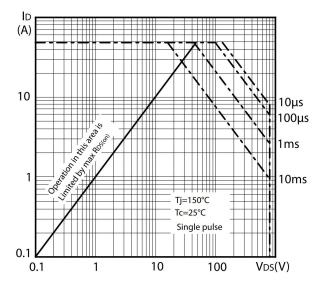

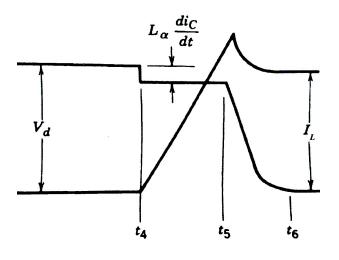

When the switch is on, the entire current  $I_L$  flows through the switch and the diode is reverse biased. When the switch is turned off,  $I_L$  flows through the diode and a voltage equal to the input voltage  $V_d$  appears across the switch, assuming a zero voltage drop across the ideal diode.

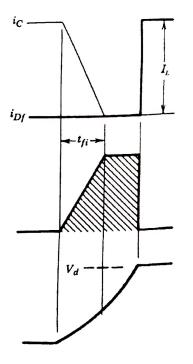

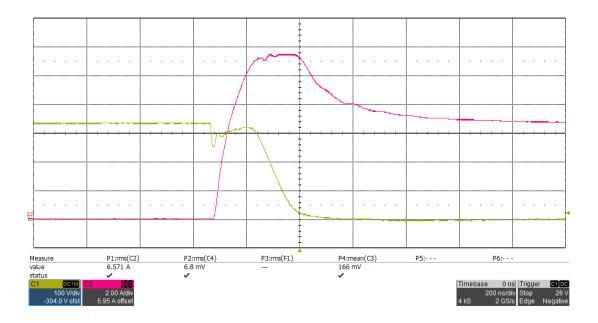

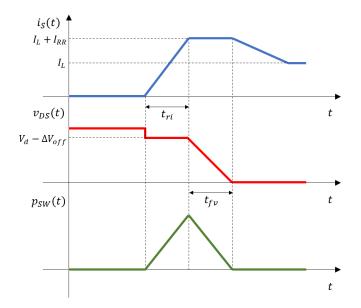

Figure 3.3.5b shows the waveforms for the current through the switch and the voltage across the switch when it is being operated at a switching frequency of  $f_S = 1/T_S$ , with  $T_S$  being the switching time period. The switching waveforms are represented by linear approximations to the actual waveforms in order to simplify the discussion.

Figure 3.3.5: Switch waveforms and instantaneous switch power loss [2].

When the switch has been off for a while, it is turned on by applying a positive control signal to the switch, as shown in Fig. 3.3.5a. During the turn-on transition of this generic switch, the current buildup consists of a short delay time  $t_{d,on}$  followed by the current rise time  $t_{ri}$ . Only after the current  $I_L$  flows entirely through the switch can the diode become reverse biased and the switch voltage fall to a small on-state value, negligible for this discussion, with a voltage fall time of  $t_{fv}$ . The waveforms indicate that large values of switch voltage and current are present simultaneously during the

turn-on crossover interval  $t_{c,on} = t_{ri} + t_{fv}$ .

The energy dissipated in the device during this turn-on transition can be approximated from Fig. 3.3.5c as

$$W_{c,on} = \frac{1}{2} V_d \cdot I_L \cdot t_{c,on} \tag{3.3.2}$$

where it is recognized that no energy dissipation occurs during the turn-on delay interval  $t_{d,on}$ .

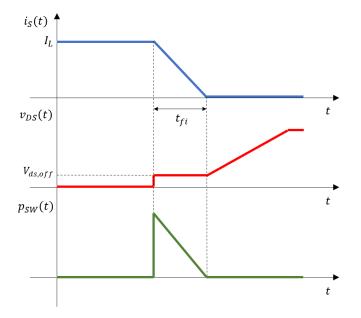

In order to turn the switch off, a negative control signal is applied to the control terminal of the switch. During the turn-off transition period of the generic switch, the voltage build-up consists of a turn-off delay time  $t_{d,off}$  and a voltage rise time  $t_{rv}$ . Once the voltage reaches its final value of  $V_d$ , the diode can become forward biased and begins to conduct current. The current in the switch falls to zero with a current fall time  $t_{fi}$  as the current  $I_L$  commutates from the switch to the diode. Large values of switch voltage and switch current occur simultaneously during the crossover interval  $t_{c,off} = t_{rv} + t_{fi}$ . The energy dissipated in the switch during this turn-off transition can be written, using Fig. 3.3.5c, as

$$W_{c,off} = \frac{1}{2} V_d \cdot I_L \cdot t_{c,off}$$

(3.3.3)

where no energy dissipation occurs during the turn-off delay interval  $t_{d,off}$ .

The instantaneous power dissipation  $p_T(t) = v_T \cdot i_T$  plotted in Fig. 3.3.5c makes it clear that a large instantaneous power dissipation occurs in the switch during the turnon and turn-off intervals. There are  $f_S$  such turn-on and turn-off transitions per second. Hence the average switching power losses  $P_S$  in the switch due to these transitions can be approximated from Eqs. 3.3.2 and 3.3.3 as

$$P_S = \frac{1}{2} V_d \cdot I_L \cdot f_S \cdot (t_{c,on} + t_{c,off})$$

(3.3.4)

This is an important result because it shows that the switching power loss in a semiconductor switch varies linearly with the switching frequency. Choosing a large value means increasing the dissipated power. Increasing the dissipated power means a greater effort and cost in removing the heat from the device die and disperse it in the ambient. For this reason, the designer has all the interest in the minimization of power losses. Therefore, from this point of view lowering the switching frequency is desirable.

From the three above mentioned switching frequency discussions about regulation velocity, exciter stator current ripple and switching losses it is evinced that the designer

has not a complete freedom in choosing the operating frequency for this application. Instead, as it happens rather often in any engineering field, the switching frequency choice is the result of a trade-off between many different issues that must be all kept into account in order to provide a good choice.

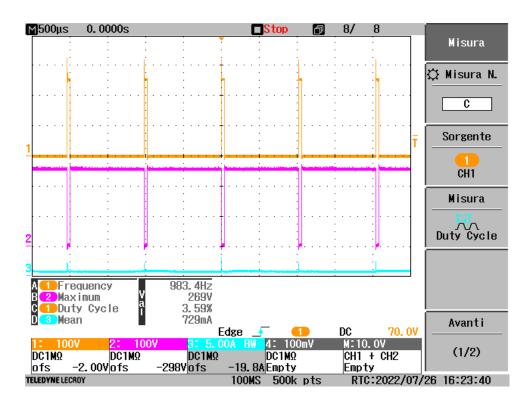

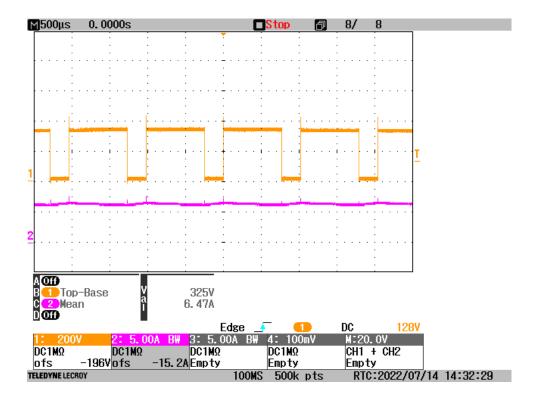

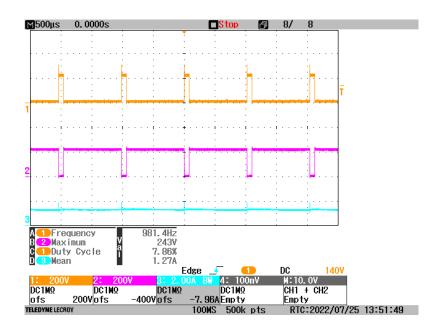

As results of this discussion it has been decided that a good switching frequency is in the order of  $1 \, kHz$ . This allows to exploit the benefit of a both turn-on and turn-off controllable power switch in order to provide a significant gain in terms of regulation velocity and current ripple with respect to the thyristor-based implementation.

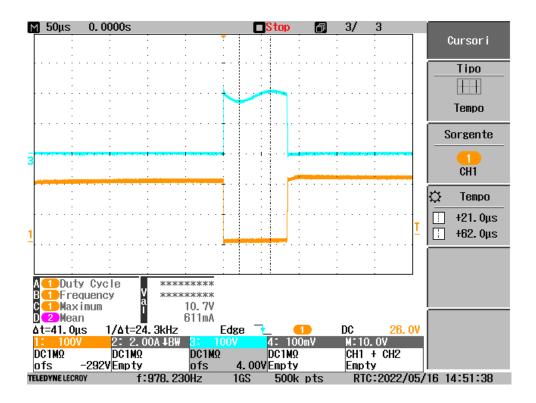

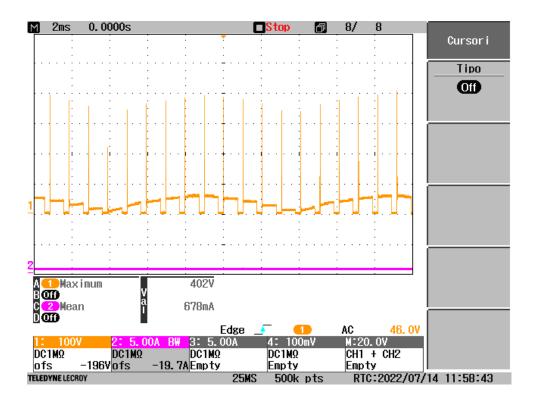

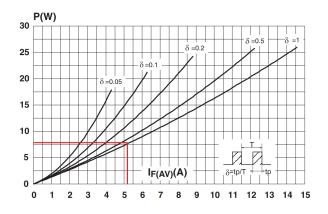

As regards the regulation velocity, if before the control signal could be updated once every 20 ms, an about 20 times shorter switching period allows to update the control signal approximately every millisecond. Regarding the current ripple there is an around 20 times reduction too. Assuming the project specification load current of  $I_L = 6.5 A$  and the typical exciter stator L = 0.8 H and  $R_L = 10 \Omega$ , the worst-case current ripple changes from  $\Delta I_{L,max,50Hz} = 1.625 A$  to about  $\Delta I_{L,max,1000Hz} = 0.081 A$ . Being such ripple approximately the 1.25% of the average value, from now on the inductive load current  $i_L$  in the case of the higher switching frequency implementation is going to be considered equal to its average value  $I_L$ . Simultaneously the around 1 kHz switching frequency value results small enough to make sure that switching losses represent a negligible amount with respect to the total device operating power loss. A dedicated treatment showing this is provided in Chapter 4.

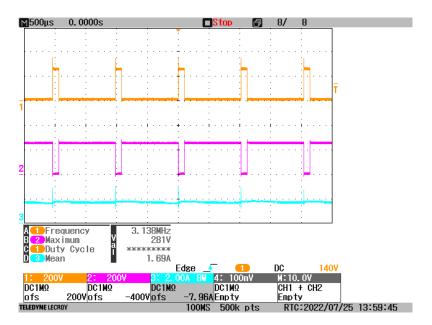

For a reason explained in Subsection 3.3.4 the ultimate value of the chosen switching frequency for this application is set to  $f_S = 976 Hz$ .

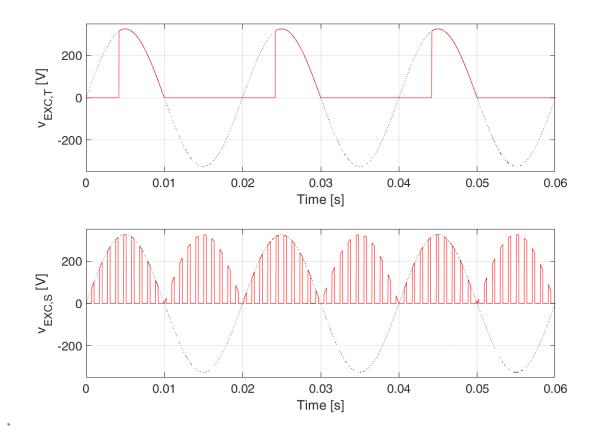

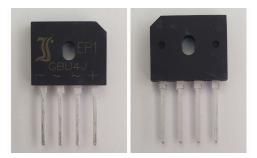

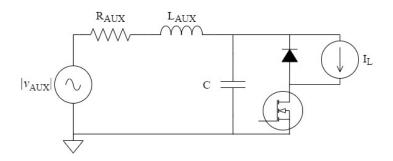

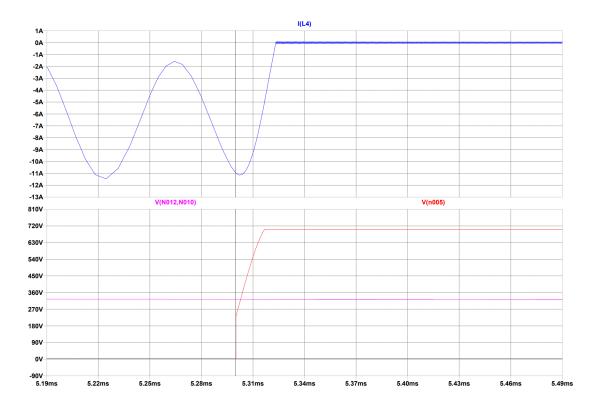

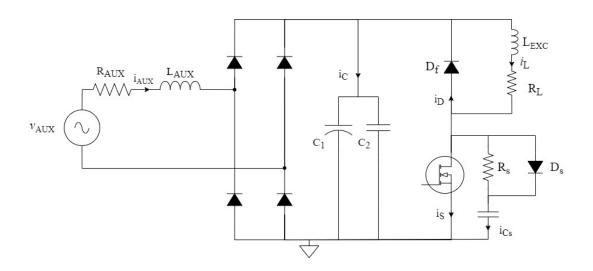

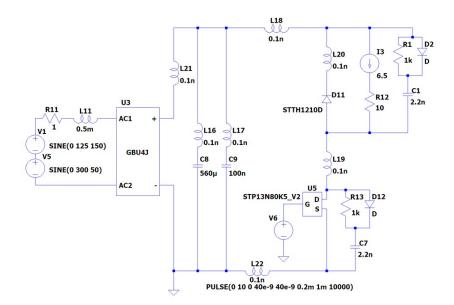

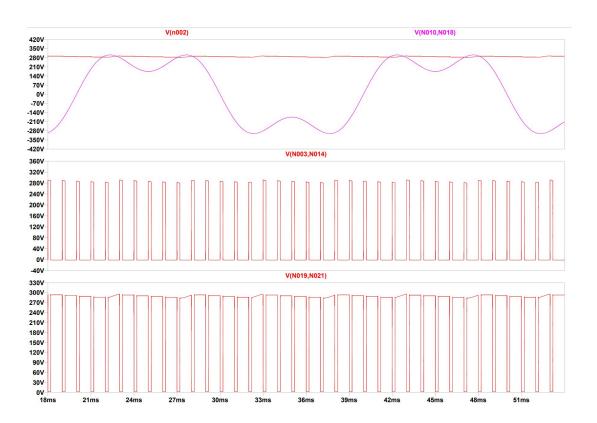

#### 3.3.2 Full wave rectification

One of the thyristor-based implementation limits exposed in Section 2.2.3 regards the impossibility to exploit the entire energy carried by the auxiliary winding to supply the excitation system. Only the positive half wave of the alternating auxiliary waveform is used to generate the voltage pulses sent to the inductive load in the currently used voltage regulator release. The reason for this is in the thyristor physical working principle: once the gate terminal is supplied by a current pulse and the thyristor turns-on, the device acts exactly as a diode. It conducts until the current through it is not brought to zero by the external circuit. To make this happen, the thyristor anode-to-cathode voltage has to reverse to negative values: assuming the thyristor is a short circuit when on, as the auxiliary alternating voltage reverses a positive bias forward-polarizes the freewheeling diode, making it to conduct. The current flow through the inductive load is drawn by the freewheeling diode, interrupting the current flow through the thyristor,

which turns off. If no zero crossing was present between the anode and cathode of the thyristor (as if a full wave rectifier was used) the current through it wouldn't have way to close up in the alternative path constituted by the freewheeling diode. Thus, it means once turned on the first time, the thyristor is not able to turn off any more and so no control is performed on the inductive current average value  $I_L$ . This is a clear disadvantage in the use of a thyristor as power switch because it automatically prevents the exploitation the energy carried by the negative half wave of the auxiliary waveform, that accounts for the half of the total energy, since it is proportional to the square of the voltage. The entire energy carried by the auxiliary waveform can instead be exploited if a controllable power switch is used: independently on the voltage applied across the device terminals, if a negative control signal is applied to the control terminal of the switch, the current flow through the device is interrupted and directed to the freewheeling diode. For this reason, a full wave rectifier can be used. A diode bridge performs exactly this task: it rectifies the input alternating voltage waveform so the voltage pulses from either positive or negative half waves can be exploited to energize the inductive load and eventually supply the excitation system. The advantage in rectifying the auxiliary waveform and being able to exploit all the energy carried by it is the possibility to obtain higher current ratings on the exciter stator starting from the same supply alternating waveform or, on the contrary, to obtain the same current level from a smaller amplitude auxiliary alternating voltage. Assuming the waveform amplitude  $V_{AUX}$  is fixed, it can be shown that a rectified waveform is able to produce up to the double of the current on the load. Recalling the relation between the average voltage applied to the load  $V_L$  and the inductive current  $I_L$  of Eq. 2.2.10, the maximum values for the average current respectively for the two cases are:

$$I_{L,max,halfwave} = \frac{V_{AUX}}{\pi \cdot R_L}$$

(3.3.5)

$$I_{L,max,fullwave} = \frac{2V_{AUX}}{\pi \cdot R_L}$$

(3.3.6)

A direct consequence of this result is that, seen from the opposite perspective, the same current level from the not rectified waveform can be obtained by a half amplitude rectified waveform.

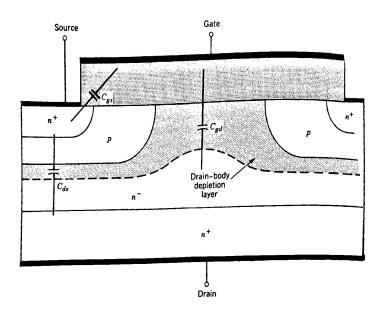

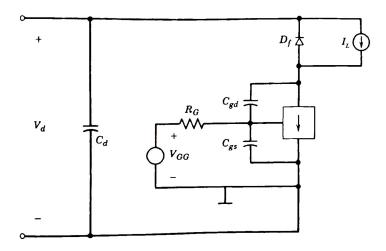

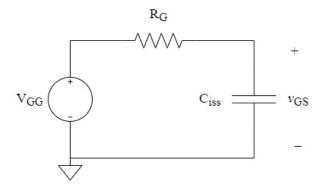

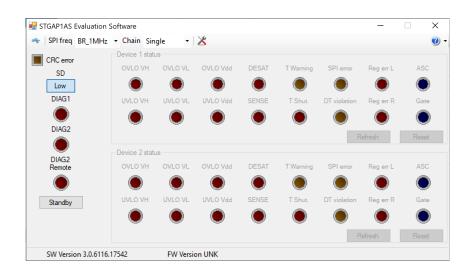

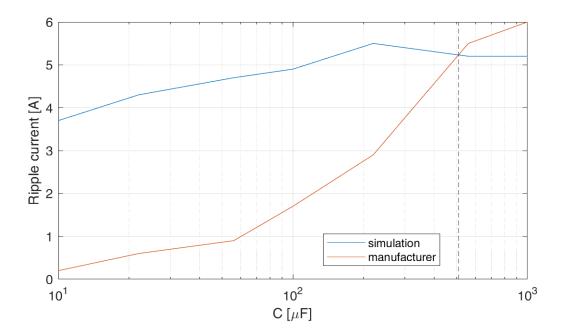

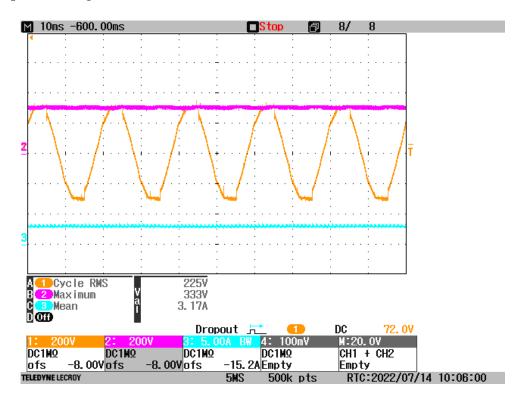

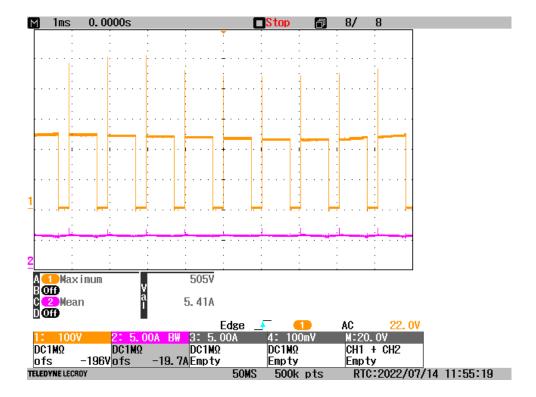

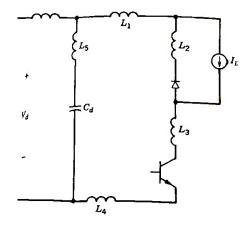

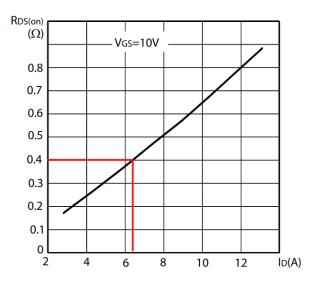

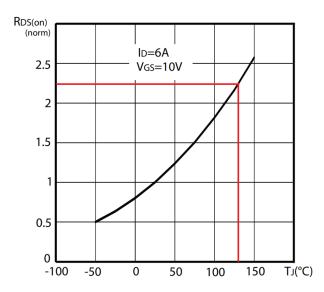

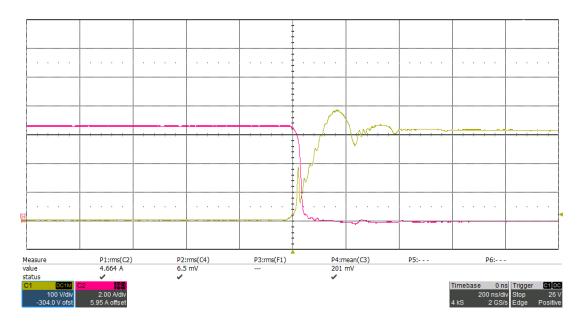

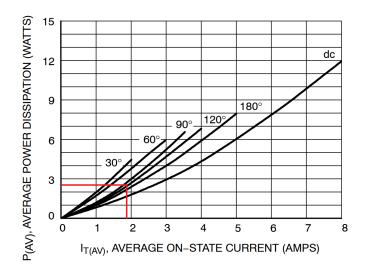

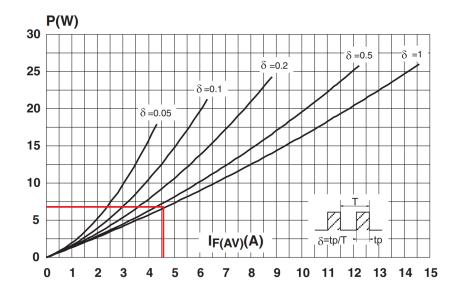

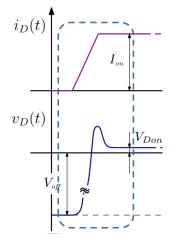

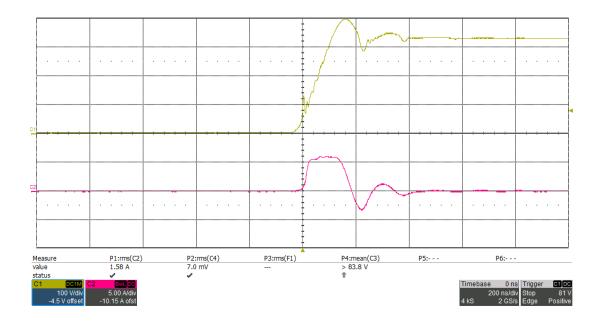

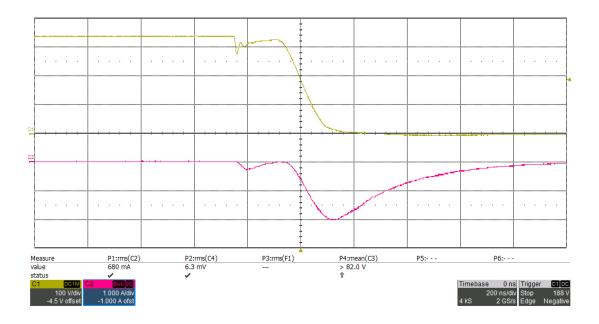

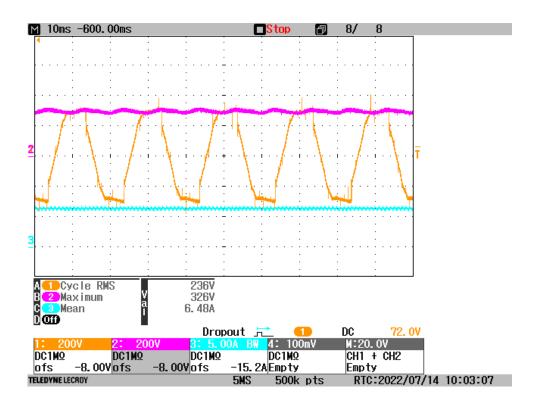

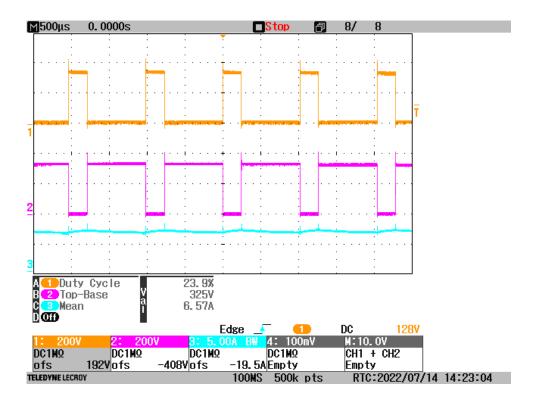

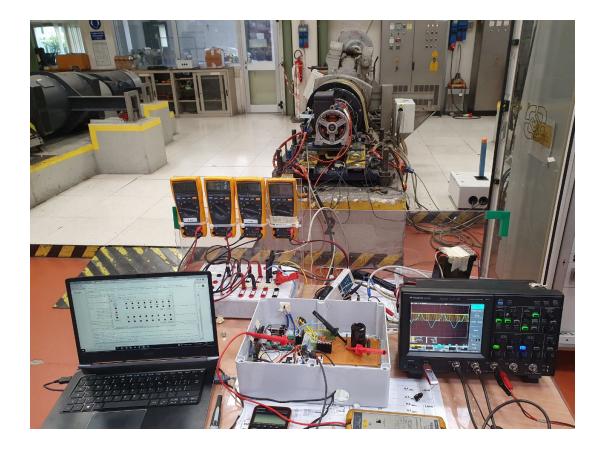

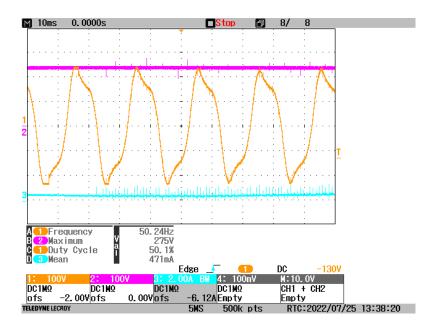

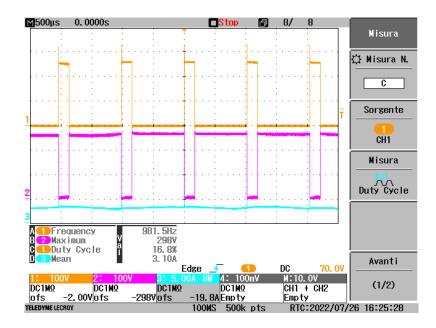

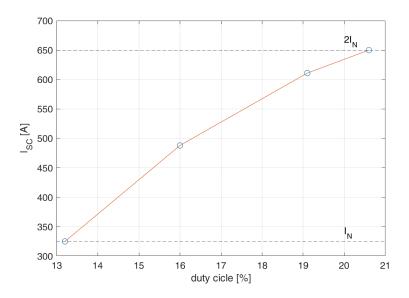

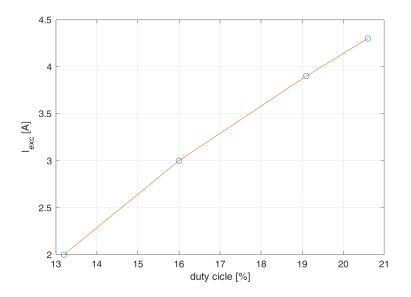

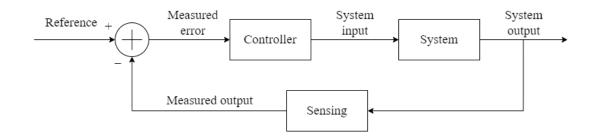

Figure 3.3.6: Exciter stator voltage pulses from not rectified auxiliary voltage for thyristor implementation and rectified auxiliary voltage for controllable switch implementation. The switching frequency for the second plot is the one decided in the last section, being 976 Hz. The pulse duration is chosen in order to provide the same  $I_L$  current starting from the same auxiliary voltage amplitude (remember  $I_L$  is independent of the switching frequency).