# Università degli Studi di Padova

DEPARTMENT OF INFORMATION ENGINEERING

MASTER'S DEGREE IN ELECTRONIC ENGINEERING

# BIDIRECTIONAL HALF-DUPLEX NEAR FIELD DATA COMMUNICATION SYSTEM FOR BIOMEDICAL IMPLANTABLE DEVICES

Supervisor Prof. Andrea Neviani *Candidate* Lucrezia Navarin

# Abstract

This work aims at designing a bidirectional half-duplex near field data communication system for biomedical implantable devices (IMDs) in the category of retinal prostheses, starting from the system realized in [19].

The purpose of IMDs is to substitute sensory or motor functionalities that have been lost due to an injury or a disease and, therefore, they require reliable transfer of a large volume of data either from external artificial sensors to the implant or in the opposite direction.

The system's architecture is based on LSK (load-shift keying) modulated inductively coupled resonators and it is strongly biased towards downlink transmission, from the external unit to the implant. Moreover it is designed to work at a carrier frequency allocated inside the ISM radio band, preferably at  $f_0 = 13.56$  MHz.

The implementation and simulation of the designed system, carried out with the aid of *Cadence Virtuoso* software, displays the limitations introduced by load-shift keying techniques in applications which require high data rate. Indeed, while LSK proves to be a reasonable choice for uplink transmission, minimizing power consumption in a direction of transmission for which data rate requirements are not that stringent, it becomes rapidly disadvantageous for downlink communication, since it evidently struggles to achieve the challenging data rate specification of 5 Mb/s.

This result suggests that exploring alternative modulation techniques, at least for downlink transmission, may lead to enhancing the performance of the system in terms of data rate requirements.

# Sommario

Lo scopo di questa tesi è la progettazione di un sistema di trasmissione di dati in tecnologia bidirezionale alternata da utilizzare per impianti biomedicali ed in particolare per l'implementazione di una retina artificiale.

I dispositivi medicali impiantabili hanno la finalità di sostituire funzioni motorie e sensoriali danneggiate a causa di infortuni o malattie e, di conseguenza, necessitano di elevata affidabilità nel trasferimento di grandi volumi di dati da sensori esterni all'impianto e nella direzione opposta.

L'architettura del sistema, progettato partendo dai risultati riportati in [19], è basata su una coppia di risonatori ad accoppiamento induttivo. La trasmissione dei dati è realizzata tramite modulazione di impedenza in tecnologia load-shift keying (LSK) ed è fortemente sbilanciata verso il downlink, ovvero la comunicazione dall'unità esterna all'impianto. Inoltre, il sistema è progettato per funzionare ad una frequenza compresa all'interno della banda ISM, preferibilmente a 13.56 MHz.

L'implementazione del sistema e le successive simulazioni, realizzate tramite l'utilizzo del software *Cadence Virtuoso*, mettono in luce le limitazioni introdotte dalla modulazione di impedenza in applicazioni, come questa, che richiedono un data rate elevato. Infatti, nonostante la modulazione LSK si configuri come una scelta ragionevole nella trasmissione in uplink, in quanto capace di minimizzare il consumo energetico in una direzione in cui le specifiche sul data rate sono alquanto lasche, essa diventa rapidamente svantaggiosa nella comunicazione in downlink, in quanto fatica a raggiungere la specifica stringente di 5 Mb/s.

Questo risultato suggerisce l'idea che approfondire tecniche di modulazione alternative, almeno per quanto riguarda la trasmissione in downlink, possa introdurre miglioramenti nella performance del sistema in termini di velocità di trasmissione dati.

# Acknowledgments

First and foremost, I would like to thank Professor Andrea Neviani for giving me the opportunity to work on this fascinating topic, advising me and supervising my work during the whole process of research and writing of my thesis.

Moreover, I would like to express my gratitude to Professor Jaeha Kim for welcoming me in the *Mixed-Signal IC and System* laboratory at Seoul National University. In there, I had the opportunity to meet hardworking, smart and motivated students whose attitude and commitment to research I will take as a positive role model throughout my whole career.

My deepest gratitude goes to Professor Jong-mo Seo for assisting me and for being a constant and valuable reference during my stay at Seoul National University.

I extend my heartfelt gratitude to all the friends who shared a moment with me in South Korea. Good times turn into good memories and each one of them made Seoul feel like a second home to me.

Last but not least, this work and my soujorn at SNU would never have been possible without the endless love and encouragement of my family and dearest friends, whose strong belief in my worth gives true meaning to everything I do.

# Contents

| Ał       | ostra | $\operatorname{ct}$                       | i             |

|----------|-------|-------------------------------------------|---------------|

| So       | mma   | ario                                      | ii            |

| Ac       | cknow | wledgements                               | iii           |

| Li       | st of | Acronyms                                  | $\mathbf{vi}$ |

| Li       | st of | Figures                                   | $\mathbf{x}$  |

| Li       | st of | Tables                                    | xi            |

| 1        | Intr  | oduction                                  | 1             |

|          | 1.1   | Motivation                                | 1             |

|          | 1.2   | Objectives                                | 2             |

|          | 1.3   | Thesis Outline                            | 3             |

| <b>2</b> | The   | ory and State of the Art                  | <b>5</b>      |

|          | 2.1   | Near Field Communication Systems          | 5             |

|          | 2.2   | Inductive Links                           | 6             |

|          | 2.3   | Data Transmission                         | 8             |

|          |       | 2.3.1 Carrier-based Modulation Techniques | 9             |

|          |       | 2.3.2 Carrier-less Modulation Techniques  | 11            |

|          | 2.4   | Other Applications                        | 13            |

|          |       | 2.4.1 Radio Frequency Identification      | 13            |

|          |       | 2.4.2 Near Field Communication            | 15            |

|          |       | 2.4.3 Wireless Power Transfer             | 16            |

| 3        | Circ  | cuit Design                               | 17            |

|          | 3.1   | Resonators                                | 18            |

|          |       | 3.1.1 Introduction to RLC Resonators      | 19            |

|          |       | 3.1.2 Resonators Design                   | 22            |

|          | 3.2   | Oscillator                                | 26            |

|          |       | 3.2.1 Introduction to Oscillators         | 26            |

|          |       | 3.2.2   | Negative   | e Res  | sista          | ance  | e M   | etł | 100 | ł. |  |  |   |   |   |   |   |   | 30 |

|----------|-------|---------|------------|--------|----------------|-------|-------|-----|-----|----|--|--|---|---|---|---|---|---|----|

|          |       | 3.2.3   | LC Diffe   | erent  | ial            | Osci  | illat | or  |     | •  |  |  |   |   |   |   |   |   | 31 |

|          |       | 3.2.4   | Oscillate  | or De  | esig           | n.    |       |     |     |    |  |  |   |   |   |   |   |   | 34 |

|          | 3.3   | LSK N   | Iodulatio  | n.     |                |       |       |     |     |    |  |  |   |   |   |   |   |   | 38 |

|          |       | 3.3.1   | Working    | ; prii | ncip           | le .  |       |     |     |    |  |  |   |   |   |   |   |   | 38 |

|          |       | 3.3.2   | CMOS S     | Swite  | ch I           | Desig | gn    |     |     |    |  |  |   |   |   |   |   |   | 46 |

|          | 3.4   | Envelo  | pe Detec   | tor    |                |       |       |     | • • | •  |  |  | • | • | • | • | • | • | 48 |

| <b>4</b> | Sim   | ulatior | ns and F   | lesu   | $\mathbf{lts}$ |       |       |     |     |    |  |  |   |   |   |   |   |   | 50 |

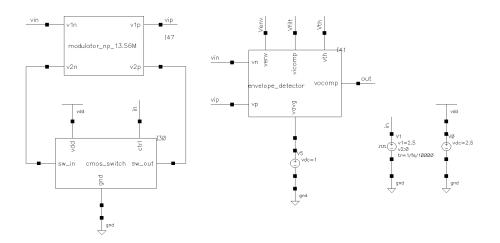

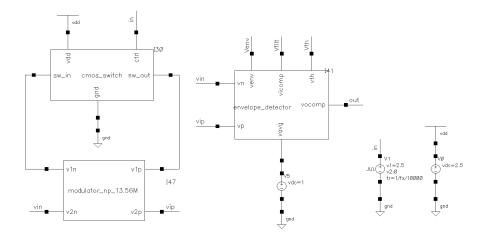

|          | 4.1   | Simula  | ation Setu | ıр.    |                |       |       |     |     |    |  |  |   |   |   |   |   |   | 50 |

|          | 4.2   | Simula  | ation Res  | ults   |                |       |       |     |     |    |  |  |   |   |   |   |   |   | 52 |

|          | 4.3   | Altern  | ative Des  | ign:   | n =            | = 3   |       |     | • • | •  |  |  | • | • | • | • | • |   | 65 |

| <b>5</b> | Con   | clusio  | ns and F   | utu    | re '           | Wo    | rk    |     |     |    |  |  |   |   |   |   |   |   | 69 |

|          | 5.1   | Conclu  | isions .   |        |                |       |       |     |     |    |  |  |   |   |   |   |   |   | 69 |

|          | 5.2   |         | e Work     |        |                |       |       |     |     |    |  |  |   |   |   |   |   |   | 70 |

| Re       | efere | nces    |            |        |                |       |       |     |     |    |  |  |   |   |   |   |   |   | 73 |

# List of Acronyms

| ASK                             | Amplitude-shift Keying 9, 10                                                                                                                                                                                                  |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BER<br>BFSK<br>BIBO<br>BPSK     | Bit Error Rate 11, 12<br>Binary Frequency-shift Keying 9<br>Bounded-input Bounded-output 27<br>Binary Phase-shift Keying 10                                                                                                   |

| CAGR                            | Compound Annual Growth Rate 1                                                                                                                                                                                                 |

| FSK                             | Frequency-shift Keying 9, 10                                                                                                                                                                                                  |

| IBC<br>IMD<br>IoT<br>ISI<br>ISM | <ul> <li>Intra-body Communication 6</li> <li>Implantable Medical Device 12, 13</li> <li>Internet Of Things 14</li> <li>Intersymbol Interference 11, 12</li> <li>Industrial, Scientifical And Medical 3, 25, 58, 69</li> </ul> |

| LFO<br>LSK                      | Low-frequency Oscillator 26<br>Load-shift Keying 10, 11, 18, 22, 25, 38, 46,<br>51, 64, 69, 70                                                                                                                                |

| NFC                             | Near Field Communication 5, 13, 14, 15                                                                                                                                                                                        |

| OOK                             | On-off Keying 9                                                                                                                                                                                                               |

| PDM<br>PHM<br>PSK<br>PTE        | Pulse Delay Modulation 12, 13, 71<br>Pulse Harmonic Modulation 11, 12, 71<br>Phase-shift Keying 10<br>Power Transfer Efficiency 11, 12                                                                                        |

| RF                              | Radio Frequency 16, 26                                                                                                                                                                                                        |

### List of Acronyms

- RFID Radio Frequency Identification 5, 13, 14, 15

- RHP Right Half Plane 27, 29, 31

- SIR Signal-to-interference Ratio 12

- WPT Wireless Power Transfer 5, 13, 16

# List of Figures

| 2.1  | Inductive link: general schematic                                | 7  |

|------|------------------------------------------------------------------|----|

| 2.2  | PHM conceptual waveforms. [6]                                    | 12 |

| 2.3  | PDM conceptual waveforms. [11]                                   | 13 |

| 2.4  | Passive RFID tags: near field power and data transfer mech-      |    |

|      | anism. [18]                                                      | 14 |

| 2.5  | NFC operating modes. [12]                                        | 15 |

| 2.6  | WPT technologies classification. [13]                            | 16 |

| 3.1  | Block diagram of the system.                                     | 17 |

| 3.2  | Series RLC tank.                                                 | 19 |

| 3.3  | Parallel RLC tank.                                               | 21 |

| 3.4  | Generic RLC tank: example.                                       | 21 |

| 3.5  | Series to parallel transformation.                               | 22 |

| 3.6  | Cadence schematic of RLC resonators.                             | 24 |

| 3.7  | Coupling coefficient $k$ as function of distance $r$ between the |    |

|      | coils                                                            | 25 |

| 3.8  | Oscillator as a feedback system.                                 | 27 |

| 3.9  | Ideal oscillator's output.                                       | 28 |

| 3.10 | Real oscillator's output.                                        | 28 |

| 3.11 | General schematic of Colpitts oscillator.                        | 29 |

|      | Negative resistance method: circuit's partition.                 | 30 |

| 3.13 | Negative resistance method: equivalent circuit.                  | 30 |

| 3.14 | LC differential oscillator (nMOS)                                | 32 |

| 3.15 | nMOS cross-coupled pair: circuit (left) and small signal model   |    |

|      | (right)                                                          | 32 |

| 3.16 | Small signal equivalent model for cross-coupled pair.            | 33 |

| 3.17 | LC differential oscillator: small signal model.                  | 34 |

| 3.18 | Cadence schematic of LC differential oscillator.                 | 35 |

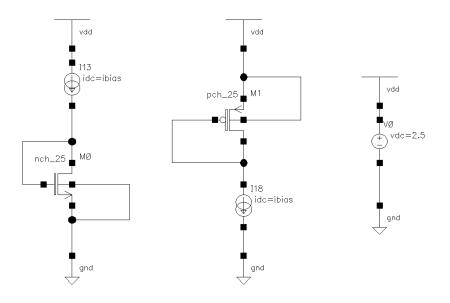

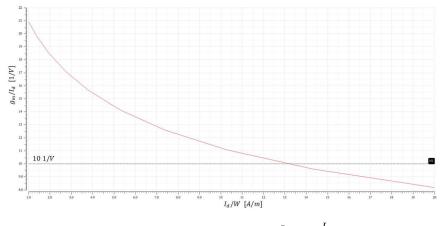

| 3.19 | Test circuit for MOS sizing.                                     | 36 |

| 3.20 | nMOS sizing: $\frac{g_m}{I_d}$ vs $\frac{I_d}{W}$ .              | 37 |

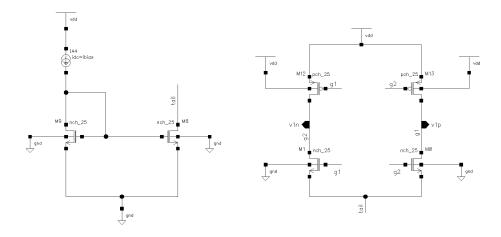

| 3.21 | Cadence schematic of CMOS oscillator with bias circuit           | 37 |

| 3.22 | Cadence schematic of the data link (resonators, oscillator and   |    |

|      | bias circuit)                                                    | 39 |

|      |                                                                  |    |

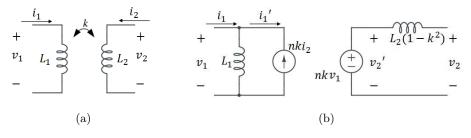

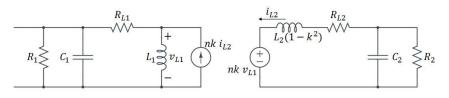

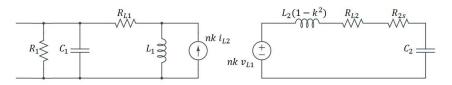

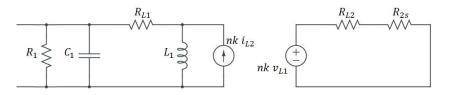

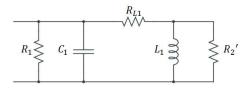

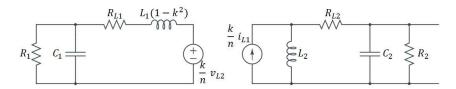

| 3.23 | Coupled coils: equivalent model derivation.                                      | 39 |

|------|----------------------------------------------------------------------------------|----|

|      | First equivalent model for uplink.                                               | 40 |

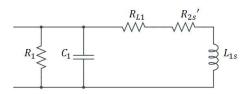

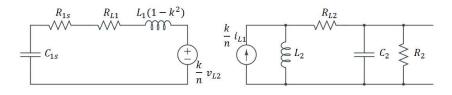

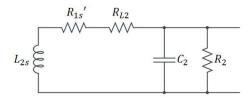

| 3.25 | Uplink equivalent model derivation: step 1                                       | 41 |

| 3.26 | Uplink equivalent model derivation: step 2                                       | 41 |

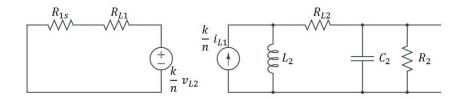

|      | Uplink equivalent model derivation: step 3                                       | 42 |

| 3.28 | Uplink equivalent model derivation: step 4                                       | 42 |

|      | Uplink equivalent model derivation: step 5                                       | 42 |

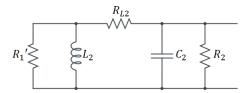

|      | Final uplink equivalent model                                                    | 42 |

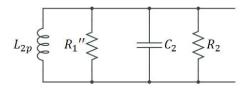

|      | First equivalent model for downlink.                                             | 44 |

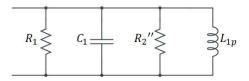

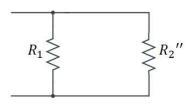

|      | Downlink equivalent model derivation: step 1                                     | 44 |

| 3.33 | Downlink equivalent model derivation: step 2                                     | 45 |

|      | Downlink equivalent model derivation: step 3                                     | 45 |

|      | Downlink equivalent model derivation: step 4                                     | 45 |

|      | Downlink equivalent model derivation: step 5                                     | 45 |

|      | Final downlink equivalent model.                                                 | 46 |

|      | AnalogLib switch component: parameter window                                     | 47 |

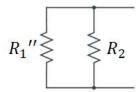

|      | Cadence schematic of CMOS switch.                                                | 48 |

|      | Cadence schematic of envelope detector.                                          | 49 |

|      | *                                                                                |    |

| 4.1  | Test bench configuration for uplink transmission                                 | 51 |

| 4.2  | Test bench configuration for downlink transmission                               | 52 |

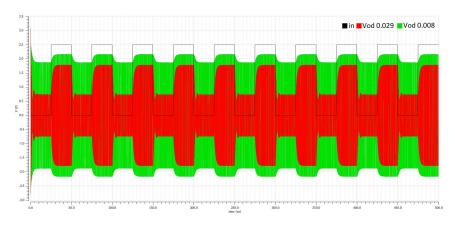

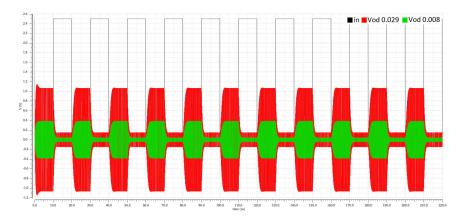

| 4.3  | Uplink at 13.56<br>MHz: modulated output voltage at 40 kb/s. $\ .$               | 53 |

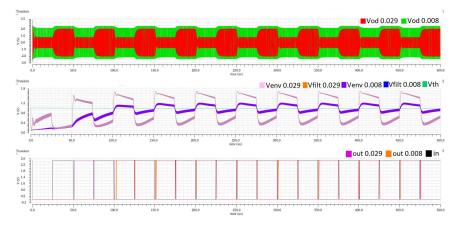

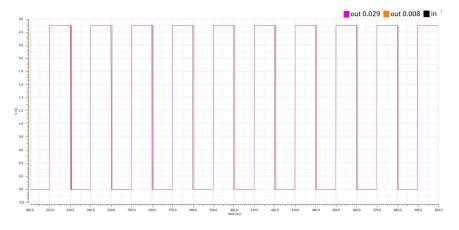

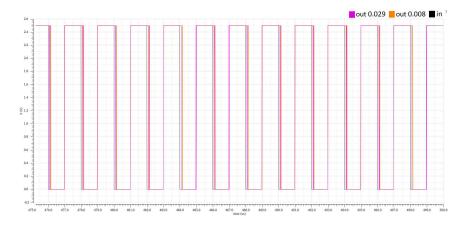

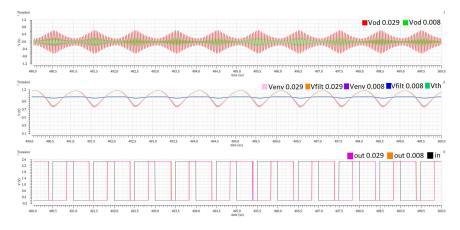

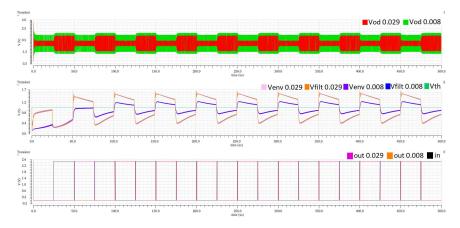

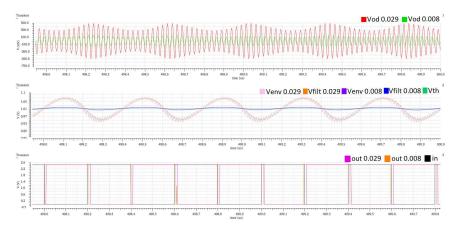

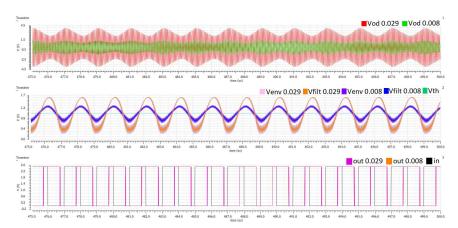

| 4.4  | Uplink at $40 \text{ kb/s}$ with $f_0 = 13.56 \text{ MHz}$ .                     | 54 |

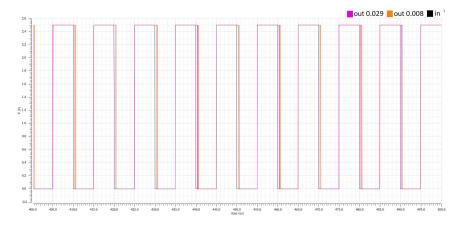

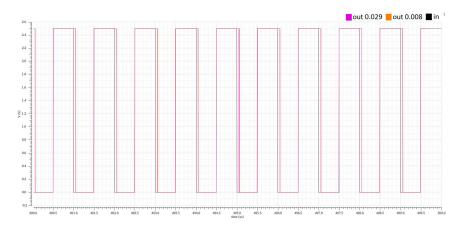

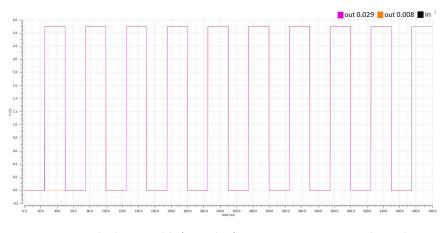

| 4.5  | Uplink at 40 kb/s with $f_0 = 13.56$ MHz: <i>out</i> aligned to <i>in</i>        | 54 |

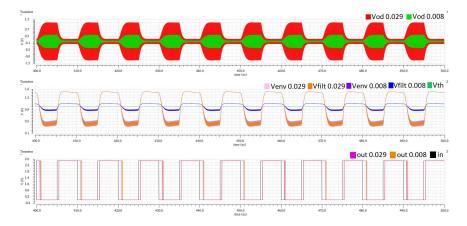

| 4.6  | Downlink at 13.56MHz: modulated output voltage at 100 kb/s.                      | 55 |

| 4.7  | Downlink at $100 \text{ kb/s}$ with $f_0 = 13.56 \text{ MHz}$ .                  | 55 |

| 4.8  | Downlink at 100 kb/s with $f_0 = 13.56$ MHz: <i>out</i> aligned to <i>in</i> .   | 56 |

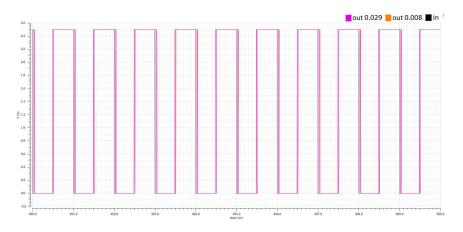

| 4.9  | Downlink at 200 kb/s with $f_0 = 13.56$ MHz                                      | 56 |

| 4.10 | Downlink at 200 kb/s with $f_0 = 13.56$ MHz: <i>out</i> aligned to <i>in</i> .   | 57 |

| 4.11 | Downlink at $1 \text{ Mb/s}$ with $f_0 = 13.56 \text{ MHz}$ .                    | 57 |

| 4.12 | Downlink at 1 Mb/s with $f_0 = 13.56$ MHz: out aligned to in                     | 58 |

|      | Downlink at 2 Mb/s with $f_0 = 13.56$ MHz: out aligned to in                     | 58 |

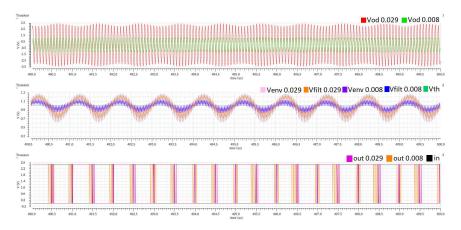

|      | Uplink at $40 \text{ kb/s}$ with $f_0 = 27.12 \text{ MHz}$ .                     | 59 |

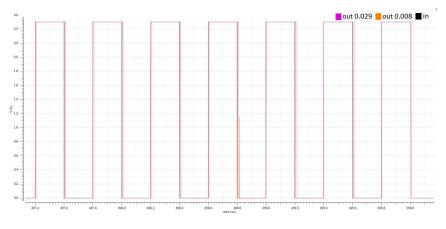

| 4.15 | Uplink at 40 kb/s with $f_0 = 27.12$ MHz: <i>out</i> aligned to <i>in</i> .      | 59 |

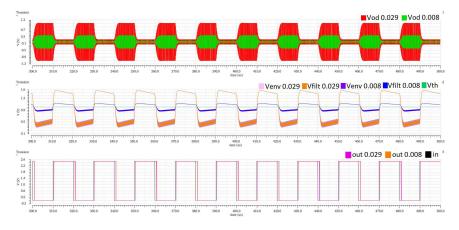

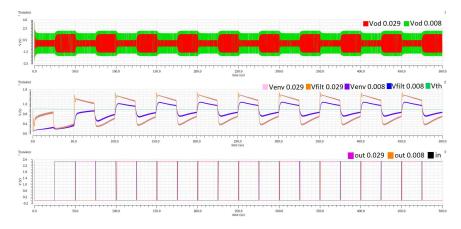

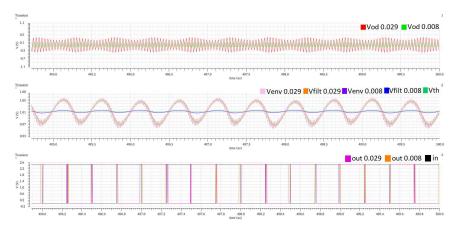

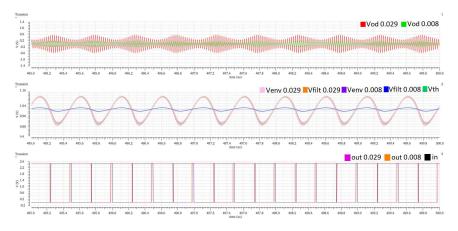

| 4.16 | Downlink at 2 Mb/s with $f_0 = 27.12$ MHz                                        | 60 |

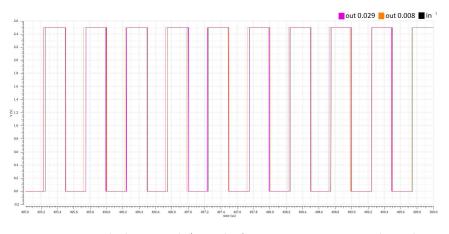

| 4.17 | Downlink at 2 Mb/s with $f_0 = 27.12$ MHz: out aligned to in.                    | 60 |

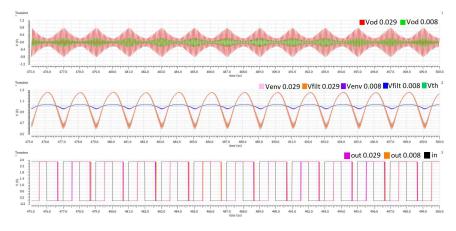

| 4.18 | Downlink at $4 \text{ Mb/s}$ with $f_0 = 27.12 \text{ MHz}$                      | 61 |

| 4.19 | Downlink at $4 \text{ Mb/s}$ with $f_0 = 27.12 \text{ MHz}$ : out aligned to in. | 61 |

| 4.20 | Uplink at $40 \text{ kb/s}$ with $f_0 = 40.68 \text{ MHz}$ .                     | 62 |

| 4.21 | Uplink at 40 kb/s with $f_0 = 40.68$ MHz: <i>out</i> aligned to <i>in</i> .      | 62 |

|      | Downlink at 4 Mb/s with $f_0 = 40.68$ MHz                                        | 63 |

| 4.23 | Downlink at 4 Mb/s with $f_0 = 40.68$ MHz: <i>out</i> aligned to <i>in</i> .     | 63 |

|      | Downlink at 5 Mb/s with $f_0 = 40.68$ MHz                                        | 64 |

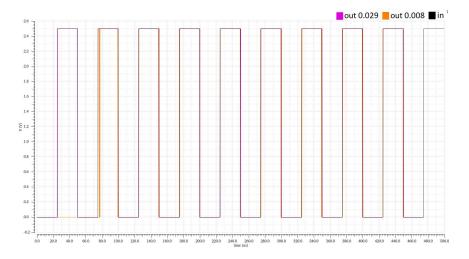

| 4.25 | Downlink at 5 Mb/s with $f_0 = 40.68$ MHz: out aligned to in                     | 64 |

|      |                                                                                  |    |

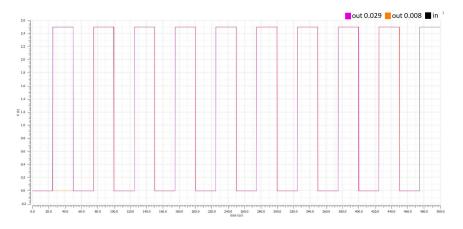

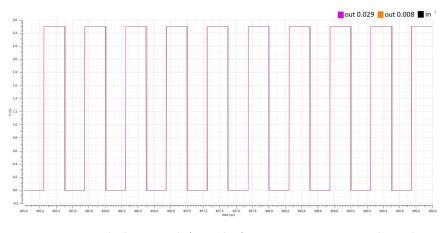

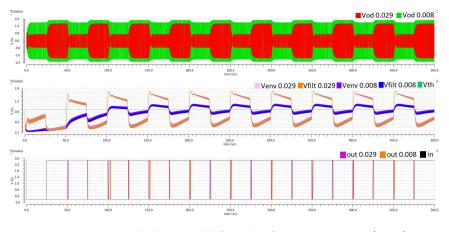

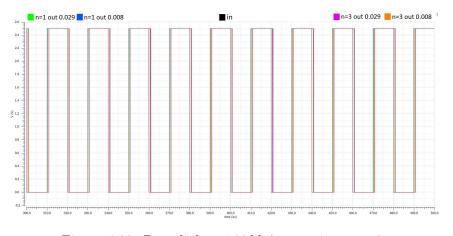

| 4.26 Uplink at 40 kb/s with $f_0 = 13.56$ MHz (n=3)  | 66 |

|------------------------------------------------------|----|

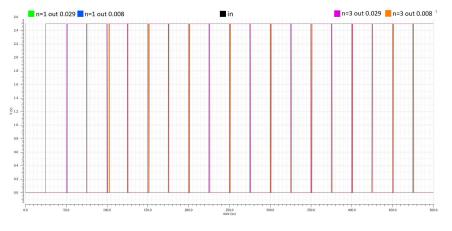

| 4.27 Uplink at 40 kb/s: $n = 1$ vs $n = 3$           | 67 |

| 4.28 Downlink at 1 Mb/s with $f_0 = 13.56$ MHz (n=3) | 67 |

| 4.29 Downlink at 2 Mb/s with $f_0 = 13.56$ MHz (n=3) | 68 |

| 4.30 Downlink at 100 kb/s: $n = 1$ vs $n = 3$        | 68 |

|                                                      |    |

# List of Tables

| 3.1 | System specifications.                                           | 18 |

|-----|------------------------------------------------------------------|----|

| 3.2 | RLC resonators components for $n=1$                              | 26 |

| 3.3 | Uplink: circuit parameters.                                      | 44 |

| 3.4 | Downlink: circuit parameters                                     | 47 |

| 3.5 | CMOS switch sizing.                                              | 48 |

| 4.1 | RLC resonators components at 13.56 MHz for $n = 1$ and $n = 3$ . | 65 |

| 4.2 | Uplink n=3: circuit parameters                                   | 66 |

| 4.3 | Downlink n=3: circuit parameters.                                | 66 |

## Chapter 1

# Introduction

This introductory chapter details the motivations for this work, dwelling on a general explanation of the field of application considered for the designed system. The focus is then shifted to the actual system to be designed, the objectives to be pursued are listed and the required specifications discussed. Finally, the structure of the document is introduced.

## 1.1 Motivation

The first record of implantation of a medical device in the human body dates back to 1958 at the Karolinska Institute in Solna, Sweden, with the first fully implantable pacemaker, designed by Rune Elmqvist and Åke Senning.

Since then, the development of the industry of implantable medical devices has been continuously proceeding at a considerably fast rate. Several factors foster the need to further expand this industry, such as the coming of the so-called super-aged society<sup>1</sup> and the rising incidence of cardiovascular and neurological illnesses. [7]

Indeed, according to a 2018 Transparency Market Research's<sup>2</sup> report, the global implantable medical devices market, which was valued at US\$ 37,700.8 Mn in 2018, is anticipated to expand at a compound annual growth rate (CAGR) of 4.6% from 2019 to 2027.

This recent and on-going proliferation of implantable medical devices, such as cochlear implants, neuro, and visual prostheses is pushing the technological research towards efficient and power saving solutions for short-range wireless data communication. A technology that has proved to be suitable to meet these requirements is inductive coupling, which is, indeed, useful to realize a reliable transfer of data between two devices placed in proximity.

<sup>&</sup>lt;sup>1</sup>According to the United Nations, the term *super-aged society* refers to a society where more than 20% of the total population is aged 65 years and older.

<sup>&</sup>lt;sup>2</sup>https://www.transparencymarketresearch.com/

The benefits introduced by inductively-based data links are particularly attractive, not only for biomedical implants, but also for other emerging technologies, such as contact-less payments and domotics applications. Nevertheless, implantable devices play, by themselves, a very central role in the demand for technological advance in this field due to their remarkable potential applications in health-care.

The main requirements driving technological research in this field are high reliability, longevity of the device and efficiency of the transfer of data and, eventually, power. Indeed, many of these links have been used to transmit wireless power to the implanted device in addition to carrying information.

It is, in fact, not feasible to rely on batteries in order to power up the device, since it would unavoidably lead to the deployment of invasive methods, such as surgical remove of the implant, for the process of recharge of the latter.

Unfortunately, the development of implantable medical devices is also facing several challenges and limitations. First and foremost, the main challenge to be faced resides in the limited available physical space, both in terms of volume and shape. Moreover, some limitations that are worth mentioning concern the materials to be deployed, the level of power consumption, bio-compatibility and the realizable functionalities.

Some other factors are also expected to be hindering the expansion of the industry, such as the high cost of the devices and the increased demand for non-invasive treatments.

Taking the aforementioned challenges into account, the design of a bidirectional half-duplex inductive data link for an artificial retina is proposed as the work for this thesis. The idea behind the artificial retina is to restore sight to the blind by transmitting digital images collected by a camera to an implant on the eye, producing artificial vision.

The system to be designed in this work relies on the technology introduced in [19], which serves as an inspiration for the work to be realized, and extends the use of load-shift keying also to the downlink direction of transmission, while adapting the system to the desired use-case. The deployed mechanism of communication leads to a system that is strongly biased towards downlink transmission, from the external device to the implant, with stringent requirements on the data rate to be achieved, which inevitably expose the main limitations of the deployed modulation technique.

## 1.2 Objectives

As previously introduced, the main objective of this thesis is to design a bidirectional half-duplex near field data communication system for a retinal prosthesis.

The system is designed based on the work reported in [19], deploying

load-shift keying modulation over a pair of inductively coupled resonators driven by an oscillator, that is working at their common resonant frequency.

The following specifications are set for the project.

First and foremost, some stringent constraints on the feasible dimensions of the coils must be respected. More specifically, the diameter of the implanted coil  $d_2$  must be smaller than 15 mm. This constraint can be slightly relaxed on the external device, with a maximum value for the coil diameter  $d_1$  equal to 30 mm.

The range of distance between the coils over which reliable communication is required varies from 30 mm to 50 mm.

Moreover, the system is designed to work inside the industrial, scientifical and medical (ISM) band, preferably at a carrier frequency of 13.56 MHz or, if not feasible, at multiples: 27.12 MHz or 40.68 MHz.

The main objective in the design of the system is to achieve a sufficiently high data rate while maintaining the carrier frequency at the lowest possible value due to the significant electro-magnetic field absorption, which increases at a rate of the carrier frequency squared.

Since the transfer of data occurs mainly from the external device to the implant (downlink), it is required to achieve a larger data rate for this direction of communication. Indeed, reliable transfer of data over a challenging data rate of at least 5 Mb/s is required for the downlink communication.

Conversely, regarding the uplink transmission, from the implant to the external device, a data rate of few kb/s, which is quite easily achieved, is required.

## 1.3 Thesis Outline

This thesis is divided in 5 chapters and the content is organized as follows.

Following this brief introduction, Chapter 2 presents an overview of the current state-of-the-art on near field data communication systems. More specifically, after generally introducing the characteristics of near field communication, the focus is placed on inductive data links. Their basic functioning is carefully explained, while the main parameters to be kept in mind during the design are defined. The focus is then shifted on the actual transfer of information, with a thorough review of some frequently deployed modulation techniques, supported by practical examples of realization. Last, some other applications beyond medical implantable devices are mentioned.

Chapter 3 gets into the heart of the work by accurately explaining the whole design process for the circuit. First the theory behind RLC resonators is introduced in order to prepare the reader for the actual design of the parallel RLC tanks constituting the link. Then, the LC oscillator is designed, after a brief introduction to the theory behind this category of circuits. The design of the modulating circuit is then completed by the analysis of the working principles characterizing the LSK modulation and by the design of the switch that is physically realizing the transfer of data. Last, the design process for the envelope detector is briefly discussed.

The results of the simulations performed on the designed circuit are then collected and discussed in Chapter 4. The focus is placed on the flaws exhibited by the circuit, in particular regarding the demanding specifications on data rate. An additional section explores briefly an alternative design approach.

Finally, the work is closed by Chapter 5 which contains a summary of the obtained results and drawn conclusions and discusses some useful suggestions for future work on the matter.

## Chapter 2

# Theory and State of the Art

This section covers the state-of-the-art on near field data communication systems. The focus is placed in particular on a sub-category of this class of systems, represented by inductive links. The theory behind the operation of inductive links is carefully explained and some frequently deployed modulation techniques are revised, both with their limits and their potentials. Last, a review of some other applications beyond the ones pertaining to the sphere of medical implants is reported, lingering on Near Field Communication (NFC) protocols, Radio Frequency Identification (RFID) technologies and Wireless Power Transfer (WPT).

### 2.1 Near Field Communication Systems

Over the last few years, the demand for short-range communication technologies has been increasing significantly, with several emerging applications requiring an efficient and reliable transfer of data and power between two or more devices. Among this class of systems, near field technologies based on magnetic and electric coupling have been profiling themselves as competitive strategies for data transmission both in biomedical applications and in general in the world of mobile electronics.

In order to present an exhaustive review of this category of systems, it is useful to start by revising the theory behind near and far field communication.

The electromagnetic field generated around any electromagnetic-radiation source, such as an antenna or scattering object, can be in general divided into two regions, the near field and far field. As the term suggests, the near field dominates in proximity of the electromagnetic-radiation source, while the far field radiation dominates at greater distance from the source.

The amount of distance between the region and the source induces different properties in how the electromagnetic field reacts and propagates in the two regions. In the far field region of the antenna, the radiated power decreases proportionally to the square of the distance and absorption of radiation does not affect the transmitter. Moreover, inside this region the electric and magnetic fields are strongly intertwined as the propagation of each of the two is associated to a change in the other one.

Conversely, in the near field region, the electric and magnetic fields exist independently of each other and in different sub-regions one of the two can dominate over the other, leading to a sub-division of the near field into magnetic and electric coupling regions. Furthermore, due to proximity, the receiving antenna does affect also the transmitting one, and the radiated power decreases more rapidly with distance with respect to what happens in the far field.

This rapid drop in power ensures that the effects of the near field vanish a few wavelengths away from the radiation source. In between these two regions, a third area can be defined, namely the transition zone, which combines properties of both the near and far fields based on the distance from the source.

The sub-division of the near field into regions where either the magnetic or the electric field dominates over the other leads to the identification of two major categories of near field communication systems, i.e., inductively coupled and capacitively coupled links. [5]

Among the two, inductive links are in general more common and they represent the best choice for biomedical applications, since the magnetic field causes less adverse effects on the human body with respect to the electric one. [15]

It's worth mentioning that several other approaches for short-range data (and power) transmission have been explored in the literature, such as ultrasonic based communication methods [17], optical links [3], intra-body communication (IBC) [20], and so on. Nevertheless, this work focuses on inductive coupling, which proved to be the most suitable strategy for both wireless power and data transmission for implantable medical devices. [12]

### 2.2 Inductive Links

In order to provide the reader with a complete understanding of the working principle of inductive links, some useful concepts should be briefly introduced. A good starting point is the definition of self and mutual inductances, which are two of the main parameters regulating the operation of inductive links.

The term *inductance* refers to the tendency of an electrical conductor to oppose a change in the electric current flowing through it. The flow of electric current in a conductor generates, indeed, a magnetic field around the conductor itself, whose intensity is proportional to the magnitude of the current and which is varying following the changes of the latter. The aforementioned variation in the magnetic field induces a voltage in the conductor, due to a process called *electromagnetic induction*. This induced voltage, generated by the changing current, has, in fact, the effect of opposing the initial change in current.

Inductance is quantified as the ratio of this induced voltage to the rate of change of the current causing it. More precisely, the quantity describing the effect of a conductor on itself is called self-inductance, while the term mutual inductance describes the effects of the conductor on nearby conductors.

Therefore, assuming a sinusoidal excitation current i at a frequency f, the amplitude of the sinusoidal voltage induced by the current flowing in the conductor on the conductor itself is given by  $v = 2\pi f i L$ , where L is indeed called *self-inductance*.

If a second conductor is placed in proximity of the first one, a varying voltage  $v = 2\pi f i M$  is induced across the second conductor as well and the parameter M accounts, indeed, for the *mutual inductance*.

Thanks to the superposition principle, the total voltage across each of the two conductors is given by the sum of their self-induced and mutually induced voltages.

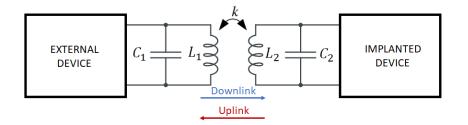

As it can be noted from the general schematic of an inductively coupled link reported in Fig. 2.1, the core of the inductive link is represented by a pair of mutually coupled inductors, which are basically two coils storing energy in the magnetic field when electric current flows through them.

Figure 2.1: Inductive link: general schematic.

From the definitions of self and mutual inductance, it is possible to derive the main parameter modeling the relation between the pair of coils constituting the inductive link, namely the *coupling coefficient*,

$$k = \frac{M}{\sqrt{L_1 L_2}} \tag{2.1}$$

with M accounting for the mutual inductance and  $L_1$  and  $L_2$  representing the self-inductances of each of the two coils.

As it can be noted straightforwardly from the definition, given that it's always true that  $M^2 \leq L_1 L_2$ , the modulus of the coupling coefficient k varies between 0 and 1 and its value expresses the strength of the coupling between

the two coils. When k = 0, the current in the first inductor doesn't affect the second one at all. Conversely, when k = 1, the first coil affects the second one as much as it affects itself.

The coupling coefficient k is proportional to the geometrical characteristics of the coils, such as their diameter, distance, orientation and alignment.

Starting from the approximated expression reported in [16] and modifying it to obey reciprocity, it is possible to derive the following simple expression for the coupling coefficient:

$$k \approx \left(\frac{d_1 d_2}{4r^2 + d_1^2 + d_2^2}\right)^{3/2} \cos\theta \tag{2.2}$$

where  $d_1$  and  $d_2$  are the diameters of the two coils, r is the distance between the coils and  $\theta$  accounts for the angle between the planes of the coils.

As reported in [19] this expression, even though an approximation, proves to fit well with measurements. From it, it is then possible to estimate the range of values acquired by the coupling coefficient, which is going to be the starting point for the inductive link design procedure.

## 2.3 Data Transmission

The main function of the inductive link to be designed in this work is to transmit information. In this work, the flow of data is bidirectional and realized as half-duplex, i.e., transmission occurs from the external device to the implant and backwards, but at two different time instants.

In this biomedical application the major focus is placed on the downlink, i.e., the transfer of data from the external unit to the eye implant, with a stringent constraint on the minimum data rate to be achieved.

Nevertheless, several other applications based on inductive links may require similar data rate in both directions of transmission or, more frequently, they may be biased towards the uplink communication.

In order to transfer data through the inductive link some modulation techniques must be deployed both concerning the uplink and downlink transmissions. In general, two different strategies can be deployed for the two directions of transmission but, in this application, load-shift keying is applied to both.

Before dwelling on the principles behind load impedance modulation, it is useful to spend some words on a more extensive revision of the main modulation techniques available in the literature, introducing both their potentials and limitations.

First and foremost, it's worth noting that all the modulation strategies introduced hereinafter relapse into either one of the two major categories, namely carrier-based and carrier-less modulation techniques. Therefore, two different sections of this chapter are dedicated to the review of some of the most common examples of carrier-based and carrier-less modulation schemes. Moreover, some practical examples of systems deploying each of these techniques, which were encountered during the review of the state of the art on near field communication systems, are briefly referenced.

### 2.3.1 Carrier-based Modulation Techniques

Most modulation techniques that have been devised for inductively coupled data links are carrier-based, i.e., they convey information by modifying either the amplitude, frequency, or phase of a sinusoidal carrier signal based on the data to be transferred. The popularity of this category of modulation techniques relies on the ease of their implementation, which is usually based on simple circuitry and consequently allows to satisfy stringent size constraints. Nevertheless, they don't always represent the most appropriate choice, mostly due to the low maximum value of data rate they can achieve, which can be significantly enhanced by deploying some other (carrier-less) modulation schemes.

#### Amplitude-Shift Keying

The most common form of carrier-based modulation is amplitude-shift keying (ASK). The basic principle behind its functioning is to represent data as variations in the amplitude of the carrier signal, while frequency and phase of the carrier are kept constant.

With this kind of techniques it is possible to achieve a very large index of modulation, in principle up to 100%, since the amplitude of the wave can be switched straightforwardly between its full-scale value and nearly zero.

The simplest realization of this modulation scheme is called on-off keying (OOK). This specific strategy refers to the case in which the modulation index is equal to 100% and the data transmission relies on the use of a carrier wave to indicate a binary one and on its absence to indicate a binary zero.

In the system introduced in article [1] ASK modulation is deployed due to its simple architecture, relatively low power consumption and affordable cost. The designed system can support power and data transfer with data rate approaching 1 Mb/s and modulation index equal to 11.1%.

#### **Frequency-Shift Keying**

An alternative approach is to keep the amplitude constant and convey digital information through discrete frequency variations of the carrier signal, implementing what is called frequency-shift keying (FSK). The simplest technique among this class of modulations is binary frequency-shift keying (BFSK), which only uses a pair of discrete frequencies to transmit binary information. As explained in [2], FSK achieves better noise performance compared to ASK schemes while keeping the design complexity low, but at the price of consuming more power. Nevertheless, in some applications such as the inductive link realized in [2], FSK appears to be a superior choice. In the aforementioned article an inductive link-based wireless power transfer system for biomedical applications is designed, additionally provided with a FSK modulated backward data transmission path achieving reliable communication up to a data rate of 10 kb/s.

#### Phase-Shift Keying

With phase-shift keying (PSK) data is sent by changing the phase of a constant frequency carrier signal. More precisely, sine and cosine inputs are varied at specific time instants. Similarly to frequency-shift keying, the simplest, and more robust, strategy among this class of techniques is binary phase-shift keying (BPSK), which relies on the use of two different phases separated by 180°.

The attractiveness of PSK (and FSK) modulation schemes is related to their ability to provide an ideally constant power envelope during data transmission and consequently achieve higher power throughput. Nevertheless, their main limitation resides in the limited data rate they can achieve. Article [8] provides an example of a realized inductive link for power and data transfer which can achieve good performances by deploying an enhanced version of PSK modulation.

#### Load-Shift Keying

In several applications a paramount objective in the realization of the link is to keep the power consumption as low as possible. This is particularly significant in the case of biomedical implantable devices, where an excessive power dissipation could lead to serious damages to the body of the patient.

Under these circumstances, it can be beneficial to rely on a modulation technique called load-shift keying (LSK), which indeed displays simple system's architecture while keeping the level of power consumption minimal. Given that any inductive link is basically a transformer made up of two inductive coils, as it is evident from the schematic in Fig. 2.1, it is possible to exploit on the following property to realize LSK modulation: a change in the secondary load is reflected onto the primary coil as a variation of the equivalent impedance.

Therefore, by switching a resistor at the load, the value of the impedance can be set to different values and this change in impedance can be directly reflected into a variation of the output voltage amplitude.

It is then straightforward to recognize load-shift keying as a special, less power-consuming, form of amplitude-shift keying. Articles [14] and [19] report two examples of LSK modulated inductive links achieving low power consumption.

#### 2.3.2 Carrier-less Modulation Techniques

The carrier-based methods are particularly attractive because the same lowfrequency data carrier can be used also to power the implanted device. However, in high-performance devices that require wider bandwidth a great improvement is obtained by separating the power carrier from the data carrier.

Indeed, aiming for high power transfer efficiency (PTE) and high data transmission bandwidth leads to conflicting requirements. To increase the data rate, a high frequency carrier is required, but to achieve a high PTE the power carrier frequency should be kept low due to the increase of loss at higher frequencies in media such as biological tissues.

As a result the use of two separated carrier signals for power and data has been introduced. A further improvement was made, as reported in articles [6] and [11], by substituting the data carrier with a series of sharp and narrow pulses, in order to reduce even more the power consumption and increase the data rate.

The two techniques introduced in the aforementioned articles are called respectively pulse harmonic and pulse delay modulation and the principles behind their operation, along with some implementation examples, are briefly explained in the following dedicated sections.

#### **Pulse Harmonic Modulation**

In article [10] a low-power transceiver for wideband near-field data transmission across inductive telemetry links is designed. Communication in the aforementioned link is achieved through the deployment of a pulse-based data transmission technique called pulse harmonic modulation (PHM), which allows to increase the data rate while lowering the power consumption.

The main goal is, therefore, to suppress the carrier signal thanks to the use of sharp and narrow pulses, reducing significantly the power consumption and transferring data across an inductive link with low self-resonance frequency. The two main parameters to be aware of are the bit error rate (BER) and the intersymbol interference (ISI) which should be kept as low as possible.

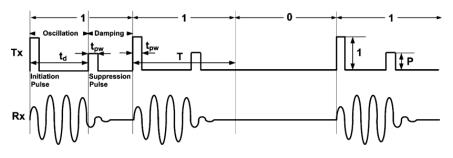

The solution introduced in article [6], where PHM is first introduced, is to "utilize a pattern of two or more pulses with specific time delays and amplitudes for transferring each bit". The key harmonic components of the so-called *initiation pulse*, at the beginning of each bit, are modulated on the receiver side by adjusting the delay time  $(t_d)$  and amplitude ratio (P) of one or more additional pulses, called *suppression pulses*, which are transmitted within every bit period (T) following the initiation pulse. The obtained signal is an amplitude modulated oscillation pattern which allows to minimize the ISI across the receiver coil and facilitate robust data demodulation with low BER.

Therefore, in PHM the oscillation pattern is modulated by sending one or more narrow pulses within the same bit period to rapidly suppress oscillation before T. Figure 2.2 shows the basic functioning of PHM, where in every "1" bit only one suppression pulse with the same width  $(t_{pw})$  is used.

Figure 2.2: PHM conceptual waveforms. [6]

In conclusion, the PHM-based transceiver designed in [10] achieves a high data rate of 20 Mb/s across a 10-mm inductive link, while minimizing the ISI at the receiver input.

#### **Pulse Delay Modulation**

Even though PHM allows to achieve overall satisfactory performances both in terms of data rate and power consumption, it is unfortunately not very robust with respect to strong power carrier interference, meaning that it operates properly only when the signal-to-interference ratio (SIR) at the receiver is high enough. Therefore, PHM becomes impractical in all the applications requiring a low-power, wideband, low BER data link that can withstand simultaneous power transmission inside the implantable medical device (IMD). [9]

To overcome this issue, another carrier-less modulation technique, called pulse delay modulation (PDM), is introduced in [11]. The main novelty introduced by PDM with respect to PHM technique is to exploit the undesired power carrier interference on the wireless data link, due to the proximity between power and data coils, to deliver information.

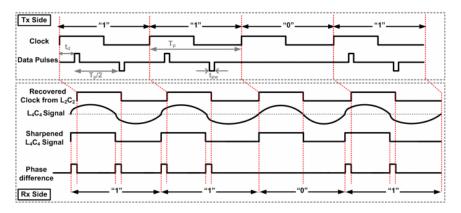

Figure 2.3 shows the operation and key waveforms of PDM for an inductive data and power transmission link where two separate links are used for power  $(L_1 - L_2)$  and data  $(L_3 - L_4)$  to keep bandwidth and PTE as large as possible.

As explained in [11], in order to send a bit "1" two narrow pulses spaced by half a power carrier cycle  $\left(\frac{T_p}{2}\right)$  are transmitted. The first pulse is applied after a specific delay  $t_d$  chosen as to introduce a shift with respect to the

Figure 2.3: PDM conceptual waveforms. [11]

interfering power carrier zero-crossing time. After  $\frac{T_p}{2}$  a second pulse with opposite amplitude is applied to introduce a similar time shift.

No pulses are transmitted for a bit "0" and, therefore, any delay between the  $L_2C_2$  and  $L_4C_4$  recovered waveforms can be easily detected as a bit "1".

In [9] a 13.56 MHz PDM-based transceiver for simultaneous power and data transmission was designed, achieving a data rate of 13.56 Mb/s across a 10-mm inductive link, while delivering 42 mW of regulated power to the load.

## 2.4 Other Applications

Even though the main focus of this work is on near field data communication systems for biomedical implantable devices, it should be noted that IMD's don't represent the only field of application for this category of circuits. Indeed, there are several other emerging applications requiring an efficient and reliable transfer of data, and eventually power, over short distances.

Some of these applications are particularly remarkable, due to their pervasiveness in our daily life. The dramatic development of mobile electronics has indeed introduced the need to deploy various magnetic-based near field technologies such as RFID, NFC and WPT. These technologies are briefly introduced in the following dedicated sections.

#### 2.4.1 Radio Frequency Identification

Radio frequency identification (RFID) leverages on the use of the electromagnetic field to automatically identify and track tags attached to objects from a distance, without requiring them to be in the line of sight.

This key property of RFID represents its main advantage over earlier bar-code technologies, together with its ability to discern multiple different tags located inside the same area without the need for human intervention. At a first, higher, level RFID devices can be categorized into two classes: active and passive tags. Active devices are in general more expensive and cumbersome due to their need for a power source. An example of active tags is the transponder attached to an aircraft identifying its national origin. [18]

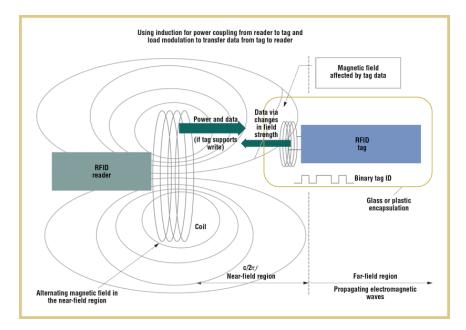

Conversely, passive tags are characterized by considerably smaller size, much longer operational life and they don't require maintenance or batteries. They are made up of an antenna, a semiconductor chip attached to it and encapsulation. The chip coordinates the process of energy capture and transfer from the antenna, while the encapsulation protects both the antenna and the chip from external contamination.

Powering and communication with the tag is carried out by the tag reader and, in most cases, it relies on magnetic coupling between the reader and the tag. In these scenarios data is sent back from the tag to the reader through the deployment of load modulation techniques. The mechanism of near field power and data transfer for RFID tags operating at less than 100 MHz is illustrated in Figure 2.4.

Figure 2.4: Passive RFID tags: near field power and data transfer mechanism. [18]

RFID is becoming more and more widespread due to its applications in traceability, access control and more in general as a key technology in the expanding field of Internet of Things (IoT). Nevertheless, this technology is unable to support peer-to-peer communication, since this standard requires initialization of communication at both ends. This standard of communication is, instead, realized by relying on the use of NFC protocols.

#### 2.4.2 Near Field Communication

NFC is a short-range half-duplex communication protocol relying on inductive coupling to provide data transfer between two close and compatible devices at a working frequency of 13.56 MHz. It was developed in late 2002 by Philips and Sony. [4]

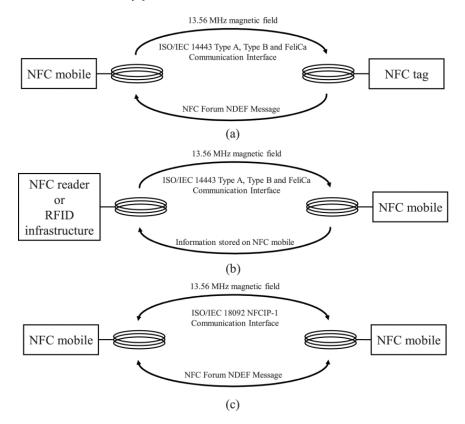

Figure 2.5: NFC operating modes. [12]

As reported in Figure 2.5 NFC technologies include three different operating modes: the reader/writer mode where an active NFC device is able to read and write the data stored in the NFC tag, the card-emulation mode which only allows contact-less reading in a fashion similar to RFID and the peer-to-peer mode which allows exchange of information in both directions. [12]

The peer-to-peer mode of operation is the main novelty introduced by NFC protocols with respect to RFID schemes, where the roles of reader device and readable tag were distinctly defined and non-interchangeable.

The development of NFC technology is contributing to the enhancement in safety, speed and user-friendliness of mobile phones, by integrating dailyuse loyalty and credit cards into it and enabling easy communication between nearby devices.

#### 2.4.3 Wireless Power Transfer

Another field of application of inductive links, which is actually closely related to biomedical implants, is represented by wireless power transfer (WPT) technologies.

Indeed, it is not feasible to rely on batteries to power up the implanted devices, due to the risks associated to the process of change or recharge of the battery which would require an invasive surgical remove of the implant. Therefore many of the links that are used to carry data signals are in addition used to transmit wireless power to the implant.

Moreover, wireless charging can introduce several other advantages with respect to traditional charging in a wider range of applications, such as improving user-friendliness by allowing different models of devices to rely on the same charger, achieving smaller dimensions due to the absence of the battery, providing better product durability and implementing more flexible and energy-efficient charging solutions. [13]

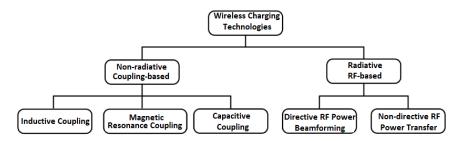

It's worth mentioning that inductive links, based on the deliver of electrical energy between two magnetically coupled coils, don't represent the only feasible option to implement efficient and reliable power transfer. Indeed, several wireless charging technologies rely on alternative techniques as illustrated in Figure 2.6.

Figure 2.6: WPT technologies classification. [13]

First of all, these technologies can be classified into non-radiative couplingbased charging and radiative RF-based charging. Among the former category, besides inductive coupling, also magnetic resonance coupling, based on evanescent-wave coupling, and capacitive coupling can be found.

The latter category, instead, comprehends directive radio frequency (RF) power beamforming and non-directive RF power transfer.

Thanks to the multiple benefits they introduce and to the several different possible realizations, WPT systems are nowadays among the most widespread technologies not only with the aim of recharging implantable devices but successfully applied to various mobile devices, and deployed to operate small home appliances and to energize electric cars.

## Chapter 3

# Circuit Design

The system designed in this work is a bidirectional half-duplex near field data communication system for biomedical implantable devices in the category of retinal prostheses.

The idea behind the functioning of the retinal prosthesis is to have an external camera collecting videos and images and sending them directly to the eye of the patient. Therefore, two transceivers must be realized: a first one to be implanted on the eye of the patient, and a second one to be mounted on a special pair of glasses.

Clearly, most of the data exchange happens from the external transceiver towards the implant, in what is referred to as *downlink* direction of communication, but some control signals must also be sent in the opposite, *uplink*, direction.

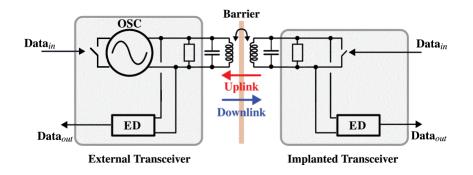

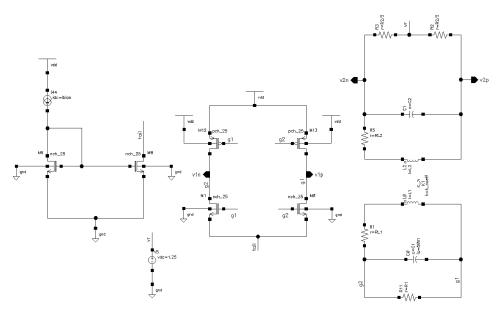

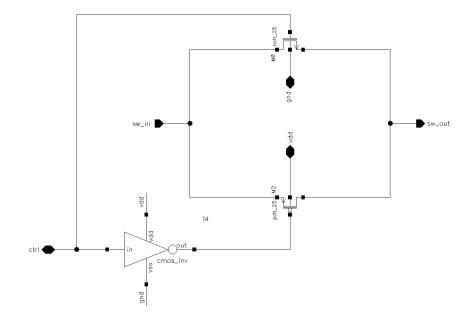

The block diagram of the link, whose design is based on the system realized in [19], is reported in Figure 3.1.

Figure 3.1: Block diagram of the system.

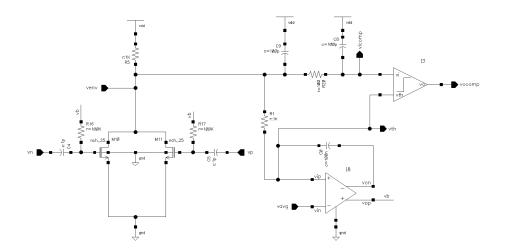

As it is visible from the block diagram, the core of the link is represented by two coupled inductors placed in close proximity. These inductors make part of two parallel RLC resonators, which are tuning an oscillator to their common resonant frequency.

The left half of the circuit, composed by the oscillator and one of the two resonators, represents the external transceiver while the other resonator accounts for the implanted device.

In order to limit as much as possible the power consumption of the system, data is transmitted through the deployment of load-shift keying.

Both the external and the implanted transceiver include a block realizing the *envelope detector* whose purpose is to demodulate the received data.

In this work the system is designed only with the aim of exchanging data and no power transfer mechanism is realized. Nevertheless, in a practical realization of the link some power supply for the implanted device, alternative to rechargeable batteries, would be essential.

The objectives and specifications for the system, which were introduced in Section 1.2, are summarized in Table 3.1.

| Parameter                     | Value                         |

|-------------------------------|-------------------------------|

| External coil diameter $d_1$  | $30 \mathrm{mm}$              |

| Implanted coil diameter $d_2$ | $15 \mathrm{~mm}$             |

| Coils distance $r$            | [30, 50]  mm                  |

| Carrier frequency $f_0$       | $13.56/27.12/40.68~{\rm MHz}$ |

| Uplink data rate $D_{up}$     | few $\rm kb/s$                |

| Downlink data rate $D_{dn}$   | $>5~{ m Mb/s}$                |

Table 3.1: System specifications.

The design of the subsystems realizing the communication system is carried out in the following sections. In particular, after introducing the basic principles behind the functioning of resonators, Section 3.1 focuses on the design of the two parallel RLC tanks constituting the core of the data link.

Section 3.2 presents an introduction to oscillators and describes the design of the CMOS LC oscillator that is driving the inductive link.

Last, Section 3.3 is dedicated to the practical implementation of the LSK modulation, while Section 3.4 dwells on the design of the circuit used for envelope detection both at the implant and at the external device.

## 3.1 Resonators

As briefly anticipated in the previous section, the core of the inductive linkbased system designed in this work is represented by a pair of mutually coupled inductors. These two inductors are part of two RLC resonators tuning an oscillator to their common resonant frequency.

Consequently, the starting point for the design of the system is the design of the resonators. In the following subsections a general introduction to the theory behind the functioning of resonators and their purposes is reported, dwelling both on the category deployed in this work, namely parallel RLC tanks, and on its dual, i.e., series RLC tanks. Afterwards, the design procedure followed in this work is discussed and the final sizing of the components of the resonating network is reported.

#### 3.1.1 Introduction to RLC Resonators

An RLC resonator is a circuit made up of a resistor, an inductor and a capacitor connected in series or in parallel. This category of elementary circuits is useful for different purposes, such as the realization of matching networks, i.e., passive networks realizing an impedance transformation, to achieve high frequency gain by cancelling transistor's parasitic elements and to filter signals over a range of frequencies.

The main property of these circuits lies in their ability to resonate at the so-called *resonant frequency*  $f_0$ . This resonant frequency is defined as the frequency at which the impedance of the resonator is purely resistive (purely real).

In order to provide the reader with more accurate knowledge on RLC networks, the following sections focus respectively on series and parallel RLC resonators. Moreover, an additional mention of how to trace back other generic RLC networks to one of the two main categories introduced above is reported.

#### Series RLC Tank

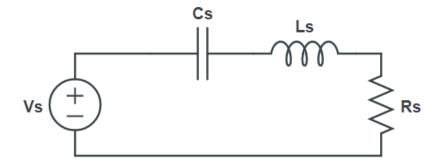

Figure 3.2: Series RLC tank.

This first section deals with series RLC tanks as the one reported in Figure 3.2. First of all, it's useful to retrieve the complex impedance of the tank, which is

$$Z_s = R_s + sL_s + \frac{1}{sC_s} = \frac{1 + sR_sC_s + s^2L_sC_s}{sC_s}$$

(3.1)

From the expression of the impedance it is possible to derive the expression of the frequency response of the system, which is given by

$$Z_s(j\omega) = R_s + \frac{j}{\omega C_s} (\omega^2 L_s C_s - 1)$$

(3.2)

It is then evident that  $|Z_s(j\omega)| \to \infty$  both as  $\omega \to 0$  and as  $\omega \to \infty$ . Therefore, both at very low (DC) and at very large frequencies the resonant network is equivalent to an open circuit.

Moreover, the resonant frequency  $f_0$  can be derived as the frequency at which the inductive and capacitive reactances cancel out and the impedance is purely resistive:

$$|Z_s(j\omega_0)| = R_s \quad \text{at} \ \omega = \omega_0 = \frac{1}{\sqrt{L_s C_s}}$$

(3.3)

A key property of any resonator lies in its ability to store energy. More specifically, a good resonator is able to store a significant amount of energy while dissipating as little power as possible.

A measurement of the quality of the resonator is provided by the *quality* factor Q, which is a dimensionless figure of merit that is only defined at resonance as:

$$Q = \omega \frac{W_t}{P_l} \tag{3.4}$$

where  $W_t = \frac{1}{2} L_s I_{pk}^2$  is the total energy stored in the resonator at resonance, while  $P_l = \frac{1}{2} R_s I_{pk}^2$  is the average dissipated power.

Therefore, for a series RLC tank  $Q = \sqrt{\frac{L_s}{C_s}} \frac{1}{R_s}$ , where  $\sqrt{\frac{L_s}{C_s}}$  is called the *characteristic impedance* of the resonator.

It's worth noting that, from the definition of 3 dB bandwidth, the following relation can be retrieved:

$$Q = \frac{\omega_0}{\omega_{-3dB}} \tag{3.5}$$

This relation implies that the higher the quality factor Q is, the smaller the bandwidth would be, meaning that a resonator with very high Q is a very frequency selective resonator. This statement is one of the main rules guiding the design of the system realized in this work.

#### Parallel RLC Tank

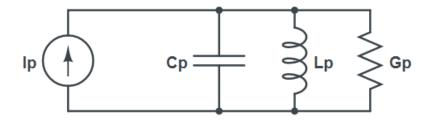

The parallel tank reported in Figure 3.3 is the dual circuit of the series RLC resonator. Therefore, the properties of the parallel RLC tank can be retrieved in a very similar fashion.

Figure 3.3: Parallel RLC tank.

By duality the admittance of the circuit is given by:

$$Y_p(j\omega) = \frac{1}{R_p} + \frac{j}{\omega L_p} (\omega^2 L_p C_p - 1)$$

(3.6)

In this case, both at very low (DC) and very large frequency the resonant network is equivalent to a short circuit. Moreover, the resonant frequency and the quality factor of the RLC parallel tank are given by:

$$\omega_0 = \frac{1}{\sqrt{L_p C_p}}$$

and  $Q = R_p \sqrt{\frac{C_p}{L_p}}$  (3.7)

Once again, a very high Q leads to a very frequency selective resonator.

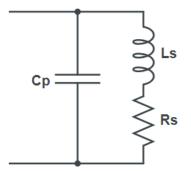

### Other RLC Resonators

Figure 3.4: Generic RLC tank: example.

In practical situations most resonant networks are neither purely series nor purely parallel tanks, but they may instead present a configuration similar to the one reported in Figure 3.4. It is then paramount to derive a set of formulas allowing to trace back this kind of configurations to one of the two studied in the previous sections. It is useful to start from a general case as the one reported in Figure 3.5.

Figure 3.5: Series to parallel transformation.

By equating the impedances of both networks it is retrieved:

$$R_s + jX_s = \frac{1}{\frac{1}{R_p} + \frac{1}{jX_p}}$$

(3.8)

It is then useful to define the *impedance transformation factor* M as  $M(\omega) = \frac{X_s}{R_s} = \frac{R_p}{X_p}$  and, by separating the real and imaginary components in Equation 3.8, the following formulas for series-to-parallel transformation are obtained:

$$R_{p} = R_{s}(1 + M^{2}(\omega))$$

$$X_{p} = X_{s}(1 + M^{-2}(\omega))$$

(3.9)

The parallel-to-series transformation, instead, is achieved by simply inverting the above equations. It's worth noting that at resonance, if  $X_s$  and  $X_p$  are either purely inductive or purely capacitive, the impedance transformation factor  $M(\omega_0)$  coincides with the quality factor Q of the resonator.

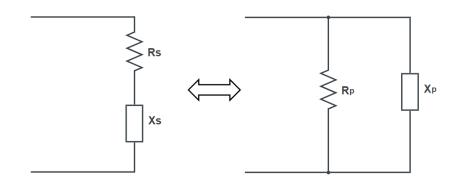

#### 3.1.2 Resonators Design

Now that the general theory behind RLC resonators has been introduced, the focus can shift on the actual circuit to be designed. In this work, the couple of RLC resonators making up the core of the inductive link are realized as parallel RLC tanks. As introduced in [19], this topology choice allows to achieve better responsiveness of the circuit to changes in the load, meaning that a better LSK modulation can be obtained. Moreover, "a parallel resonator straightforwardly tunes a differential LC oscillator" [19], which is one of the main components of the designed circuit.

Once the topology for the resonators is chosen, the first step is to accurately size the components, i.e., inductors, capacitors and resistors. The starting point is represented by the inductors, which coincide indeed with the core element realizing the inductive link.

The sizing of the inductors is carried out starting from the specifications on the maximum diameter of the coils. An online inductance calculator <sup>1</sup> is deployed to retrieve an estimate of the maximum feasible values for inductances  $L_1$  and  $L_2$  realizing the link.

This online tool provides both an estimate of the maximum achievable inductance and an estimate of the quality factor of the considered inductor. Since the calculator is not perfectly accurate, some margin is kept on the actual chosen values with respect to the maximum values retrieved.

From the value for the quality factor retrieved from the online calculator it is possible to derive an estimate of the parasitic series resistance of each inductor. Indeed, to each coil is associated some finite resistivity which can be modelled by simulating the behavior of the actual inductor through the series combination of an ideal inductor and of an explicit resistance accounting for this parasitic component.

The parasitic series resistance of the inductor can be estimated from the quality factor as  $R_L = \frac{2\pi f_0 L}{Q}$ , where  $f_0$  is the operative frequency of the circuit.

From Equations 3.7 for the general parallel RLC tank it is then straightforward to retrieve the values for capacitors  $C_1$  and  $C_2$ , allowing to have the system resonating at  $f_0$ , as  $C = \frac{1}{L\omega_0^2}$ .

One important thing to note is that at the desired frequency of operation ( $f_0 = 13.56$  MHz and multiples) the quality factors of the obtained capacitors are significantly larger than the ones of the corresponding (large) inductors. Therefore, throughout the whole design procedure that is following, the capacitors are considered ideal.

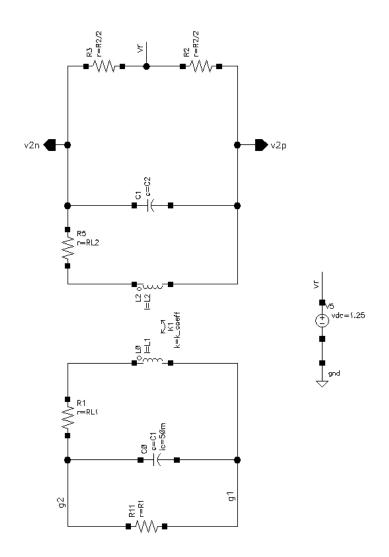

The schematic for the couple of parallel RLC resonators realized in *Cadence Virtuoso* is reported in Figure 3.6. In the reported schematic the upper half of the circuit represents the implanted circuit while the lower half accounts for the external device.

<sup>&</sup>lt;sup>1</sup>https://spok.ca/index.php/resources/tools/102-circularinductorcalc

Figure 3.6: Cadence schematic of RLC resonators.

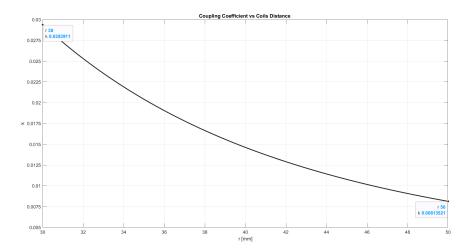

As introduced in Chapter 2, the main parameter that is modeling the interaction between the coils constituting the inductive link is the coupling coefficient k. From the specifications reported in Table 3.1 and considering two coils with maximum diameter lying on the same plane with the same orientation, the coupling coefficient k is found to be comprised between 0.008 and 0.029. It is visible from Figure 3.7, reporting the variations of the coupling coefficient as the distance between the coils varies between 30 and 50 mm, that the coupling is much weaker as the distance between the coils increases.

Figure 3.7: Coupling coefficient k as function of distance r between the coils.

The dramatically low values acquired by the coupling coefficient represent a significant issue in the design of the link since, due to the weak coupling, variations in one of the two sides of the circuit reflect very poorly on the other one. This strongly limits the quality of the LSK modulated circuit, since the main idea behind this modulation strategy is to achieve large variations in the output voltage amplitude by setting the load to different values of resistance.

As it is apparent from the schematic of the system the two inductively coupled coils basically form a transformer with ratio 1 : nk where k is, indeed, the coupling coefficient, while  $n = \sqrt{\frac{L_2}{L_1}}$  represents the so-called *turn ratio*.

A first, simple, choice to make in the design of the system is to consider unitary turn ratio and therefore two coils with the same value of inductance  $L_1 = L_2$ . In this work, as an alternative approach, also the case of an asymmetric pair of inductors with n = 3 is considered.

At a first glance, increasing the value of the turn ratio above one may introduce some advantages in the modulation, since it practically allows to compensate the extremely low values of the coupling coefficient. Nevertheless, this solution proves to be unsuitable for the system, since, along with this reduced benefit, it introduces several disadvantages, such as a significant increase in the value of the supply current.

This is more thoroughly explained in the following chapters, where the LSK modulation is analyzed more carefully.

The calculated values for the main components constituting the links are reported in Table 3.2. The values of the inductors with their parasitic series resistances and of the capacitors needed to resonate the network are calculated at three different working frequencies inside the ISM band: 13.56 MHz, 27.12 MHz and 40.68 MHz.

The inductors are sized in order to respect the constraint on the maximum diameter and to have the self-resonant frequency of each inductor being at least three times the operating frequency of the circuit.

The sizing of the explicit resistors  $R_1$  and  $R_2$  that complete the RLC resonators is carried out in Section 3.3 since it's strongly related to the load impedance modulation.

| Parameter | 13.56 MHz           | 27.12 MHz              | 40.68 MHz              |

|-----------|---------------------|------------------------|------------------------|

| $L_1$     | $1.5 \ \mu H$       | 700  nH                | 400  nH                |

| $L_2$     | $1.5 \ \mu H$       | 700  nH                | 400  nH                |

| $C_1$     | $91.84~\mathrm{pF}$ | 49.2  pF               | $38.27~\mathrm{pF}$    |

| $C_2$     | $91.84~\mathrm{pF}$ | 49.2  pF               | $38.27~\mathrm{pF}$    |

| $Q_{L1}$  | 200                 | 340                    | 400                    |

| $Q_{L2}$  | 140                 | 200                    | 240                    |

| $R_{L_1}$ | $639~{ m m}\Omega$  | $351~\mathrm{m}\Omega$ | $256~\mathrm{m}\Omega$ |

| $R_{L_2}$ | 913 m $\Omega$      | 596 m $\Omega$         | $426~\mathrm{m}\Omega$ |

Table 3.2: RLC resonators components for n=1.

### 3.2 Oscillator

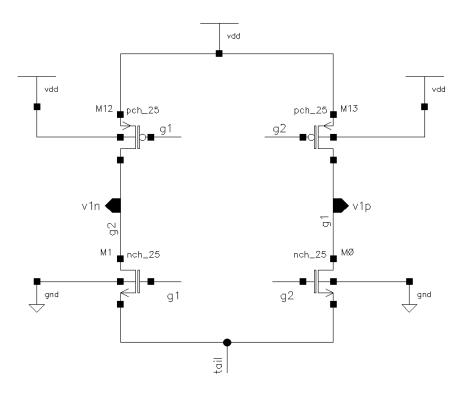

The two parallel RLC resonators designed in Section 3.1.2 tune an oscillator to their common resonant frequency. Therefore, the next step in the design of the system is represented by the design of the oscillator.

In the following subsections a brief introduction to electronic oscillators is reported and, subsequently, greater focus is placed on LC differential oscillators, such as the one implemented in this work. The last subsection focuses on the design procedure followed to realize the oscillator together with its bias circuit and displays the final schematic with chosen sizing for each component.

#### 3.2.1 Introduction to Oscillators

An electronic oscillator is an autonomous circuit converting DC power into a periodic signal. Indeed, an oscillator produces as output a periodic, oscillating signal which is often a sine wave, a square wave or a triangle wave.

Electronic oscillators are characterized by the frequency of the output signal. For example, a low-frequency oscillator (LFO) generates a signal at a frequency generally below 20 Hz, an audio oscillator in the audio range (between 16 Hz and 20 kHz) and an RF oscillator in the RF range (between 100 kHz and 100 GHz).

A relevant category of oscillators is represented by the so-called *harmonic* oscillators which produce a sinusoidal output.

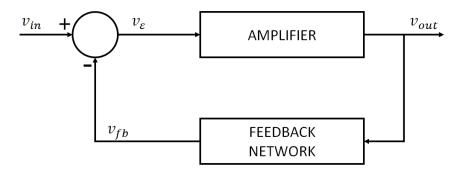

An harmonic oscillator can be easily modeled as a feedback system, like the one reported in Figure 3.8.

Figure 3.8: Oscillator as a feedback system.

The feedback system reported in Figure 3.8 is characterized by the transfer function

$$H(s) = \frac{v_{out}}{v_{in}} \tag{3.10}$$

In general, an oscillating circuit can be easily realized through the deployment of a BIBO<sup>2</sup> unstable system. Since the necessary (and sufficient) condition for the BIBO stability of a system is to have no poles of the system's transfer function lying on the right half plane (RHP), one condition needed to realize an oscillator is to have some poles lying on the RHP.

For simplicity it can be assumed to start from a simple system with  $H(s) = \frac{k}{(s-s_1)(s-s_2)}$ . Since an oscillator is a self sustaining circuit, it is able to produce an output without needing any signal at the input. Therefore, it must be assumed  $v_{in}(t) = 0$ .

Consequently, the output of the system is given by the *natural response* of the system:

$$v_{out}(t) = a_1 e^{s_1 t} + a_2 e^{s_2 t} aga{3.11}$$

where  $a_1$  and  $a_2$  are two complex numbers depending on the initial conditions of the system.

Assuming  $s_1$  and  $s_2$  to be a pair of complex conjugate poles with positive real part:

$$s_{1} = \sigma + j\omega'_{0} = s_{2}^{*}$$

$$s_{2} = \sigma - j\omega'_{0}$$

(3.12)

and  $a_1 = a_2^*$ , the output signal becomes

$$v_{out}(t) = 2|a_1|e^{\sigma t}\cos(\omega'_0 t + \angle a_1)$$

(3.13)

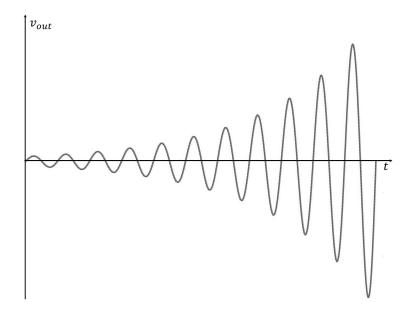

Therefore, the signal that is obtained at the output is an oscillating waveform with amplitude increasing over time, such as the one reported in Figure 3.9.

<sup>&</sup>lt;sup>2</sup>In control theory a bounded-input bounded-output (BIBO) stable system is a system in which the output is bounded for every input that is bounded.

Figure 3.9: Ideal oscillator's output.

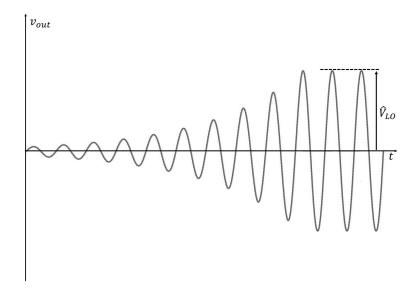

This is an accurate representation of the output sinusoid only in the ideal case. In fact, in the case of a real circuit, the non-linearities of the circuit stabilize the amplitude of oscillation which settles to a maximum value  $\hat{V}_{LO}$ . The corresponding output waveform is reported in Figure 3.10.

Figure 3.10: Real oscillator's output.

In conclusion, to realize an oscillator a feedback system which is able to generate a natural response with the following characteristics is needed:

- a pair of complex conjugate poles

- poles lying in the RHP ( $\sigma > 0$ )

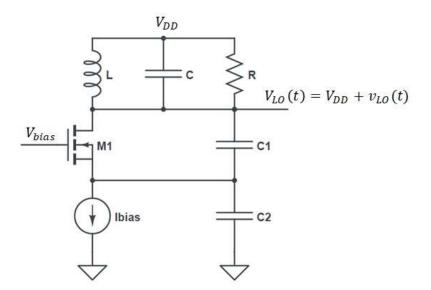

One simple, yet effective, example of a circuit realizing an oscillator is the so-called *Colpitts oscillator*. This circuit is made up of a common gate tuned amplifier and a capacitive voltage divider realizing the feedback network. The general schematic of the Colpitts oscillator is reported in Figure 3.11.

Figure 3.11: General schematic of Colpitts oscillator.

The analysis of the Colpitts oscillator can be easily carried out by treating it as a feedback system and focusing on the loop gain of the system to find the conditions needed for the oscillation start-up.

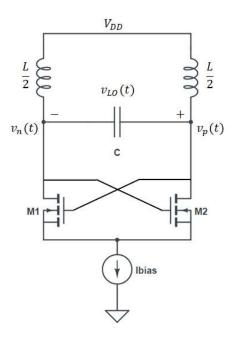

However, for several other topologies of oscillators it may be difficult to identify the feedback and it is, therefore, needed to carry out the analysis in a different fashion. This is, for example, the case of the LC differential oscillator, which is the topology chosen in this work.

It becomes then essential, before introducing this topology of circuits, to dwell on explaining a different methodology that is particularly suited for the analysis of this category of oscillators. This approach is referred to as the *negative resistance method*.

#### 3.2.2 Negative Resistance Method

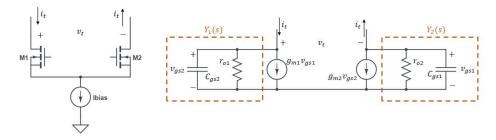

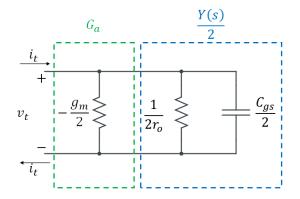

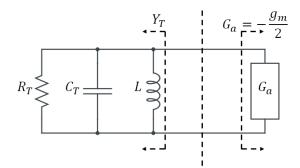

Figure 3.12: Negative resistance method: circuit's partition.

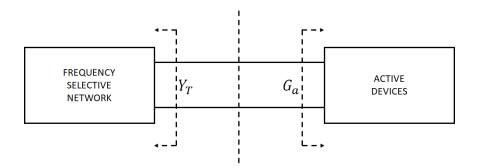

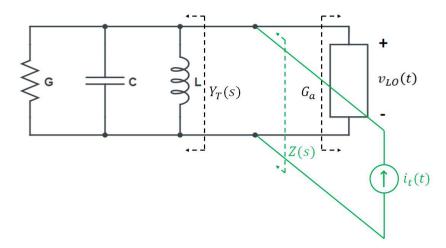

The main idea behind this approach to analyze oscillating circuits is to find an electrical port partitioning the circuit in two distinct parts (as reported in Figure 3.12): the frequency selective network comprising all the reactive components of the circuit and identified by the admittance  $Y_T$  and the active devices summarized by the parameter  $G_a$ .

First of all, the frequency selective network can be modelled as a resonant tank with overall admittance  $Y_T$ . In this case a parallel RLC tank is considered, but the same analysis can be carried out in a very similar fashion for a series RLC tank. This tank includes not only the explicit inductance, conductance and capacitance but also all the parasitic elements coming from the active devices.