Università degli studi di Padova

Laurea Magistrale in Ingegneria Elettronica

# WideBand Upconverting IQ Modulator Design in BiCMOS Technology

Relatore Prof. Andrea Bevilacqua Correlatore Dr. Ing. Marc Tiebout

> Candidato Marco Pesce

Ai miei genitori Riccardo e Mirna

# Contents

| 1        | $\operatorname{Intr}$ | oduction                                                                                                                      | 1 |

|----------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------|---|

|          | 1.1                   | Radar Systems                                                                                                                 | 2 |

|          | 1.2                   | Monostatic Phased Array Radars                                                                                                | 5 |

|          | 1.3                   | WideBand upconverter for tracking radars                                                                                      | 6 |

|          | 1.4                   | Target Specifications                                                                                                         | 7 |

|          | 1.5                   | Infineon BiCMOS technology                                                                                                    | 8 |

|          | 1.6                   | Figures of Merit                                                                                                              | 9 |

|          |                       | 1.6.1 Gain and Conversion gain                                                                                                | 0 |

|          |                       | 1.6.2 Distortion $\ldots \ldots 1$ | 1 |

|          |                       | 1.6.3 Noise Figure and SNR                                                                                                    | 4 |

|          |                       | 1.6.4 Scattering Parameters                                                                                                   | 9 |

|          |                       | 1.6.5 Unconditional Stability                                                                                                 | 0 |

| <b>2</b> | Syst                  | em Blocks 23                                                                                                                  | 3 |

|          | 2.1                   | IQ Modulator                                                                                                                  | 3 |

|          | 2.2                   | Current Commutating Mixers                                                                                                    | 6 |

|          |                       | 2.2.1 The Conversion Gain                                                                                                     | 7 |

|          |                       | 2.2.2 Noise analysis $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 3$                                | 0 |

|          |                       | 2.2.3 Linearity assumption                                                                                                    | 4 |

|          | 2.3                   | Frequency division                                                                                                            | 6 |

|          | 2.4                   | WideBand spurs issues                                                                                                         | 8 |

|          | 2.5                   | Multipath Polyphase Filtering                                                                                                 | 8 |

|          | 2.6            | Multipath Polyphase Mixer                    | 42  |

|----------|----------------|----------------------------------------------|-----|

| 3        | $\mathbf{Des}$ | ign                                          | 45  |

|          | 3.1            | Design Overview                              | 45  |

|          | 3.2            | The buffers                                  | 48  |

|          |                | 3.2.1 The input buffer                       | 48  |

|          |                | 3.2.2 Wideband Input Matching                | 50  |

|          |                | 3.2.3 The output buffer                      | 53  |

|          | 3.3            | The mixer                                    | 58  |

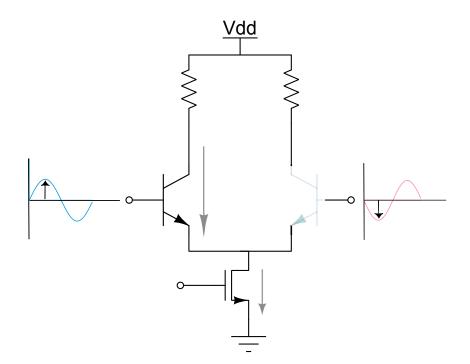

|          |                | 3.3.1 The transconductor                     | 58  |

|          |                | 3.3.2 The switching cell and the output load | 84  |

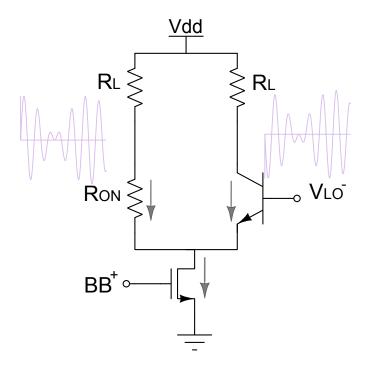

|          |                | 3.3.3 LO port buffer                         | 88  |

|          |                | 3.3.4 Mixer Design Summary                   | 91  |

|          | 3.4            | Biasing circuits                             | 95  |

|          |                | 3.4.1 BiCMOS current mirrors                 | 95  |

|          |                | 3.4.2 Enable circuits                        | 96  |

|          |                | 3.4.3 ESD Protections                        | 98  |

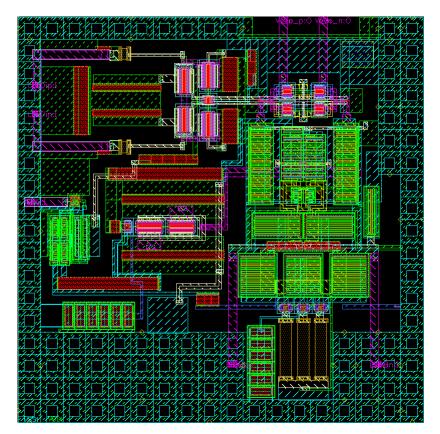

|          | 3.5            | The Frequency divider                        | 99  |

|          | 3.6            | The Multipath Polyphase structure            | 103 |

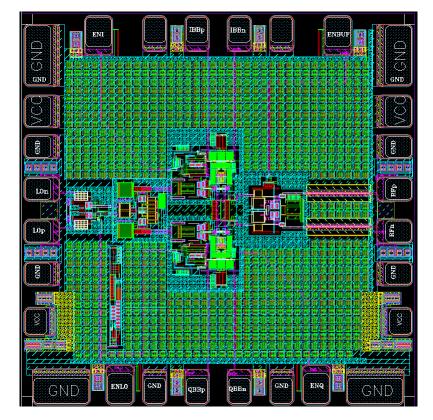

| 4        | Lay            | out 1                                        | .07 |

|          | 4.1            | Layout considerations                        | 107 |

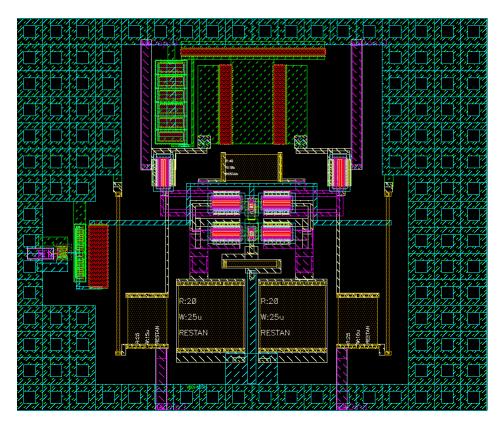

|          | 4.2            | Input buffers                                | 109 |

|          | 4.3            | Output buffers                               | 110 |

|          | 4.4            | Mixer                                        | 111 |

|          | 4.5            | Frequency Divider                            | 113 |

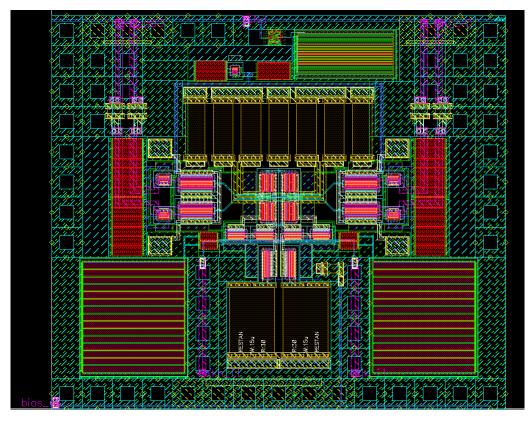

|          | 4.6            | Top Level                                    | 114 |

| <b>5</b> | $\mathbf{Sim}$ | ulations 1                                   | 17  |

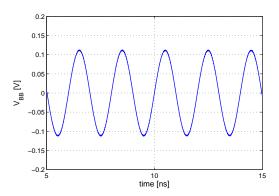

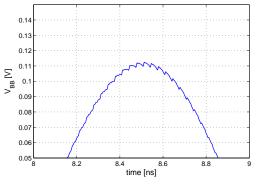

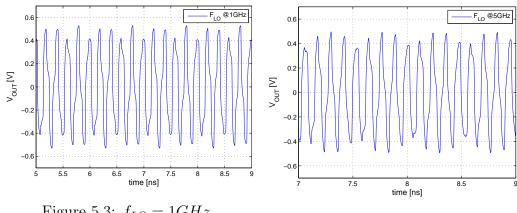

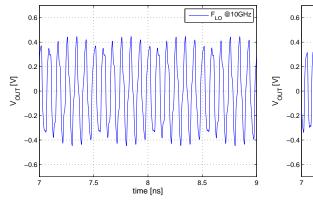

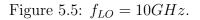

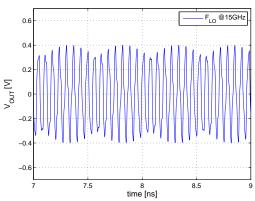

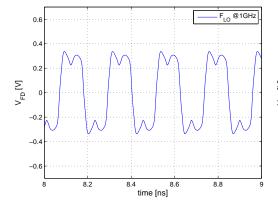

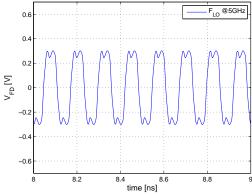

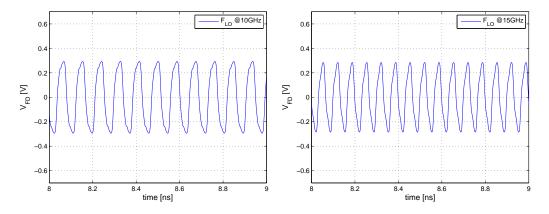

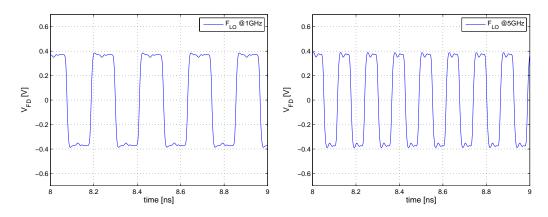

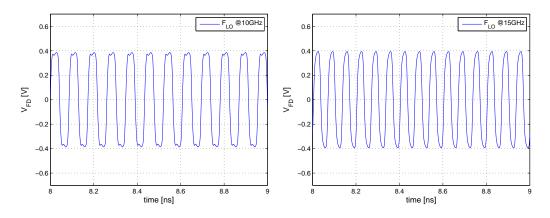

|          | 5.1            | Waveforms in the time domain                 | 118 |

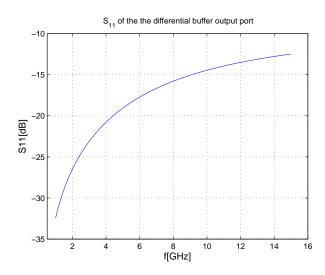

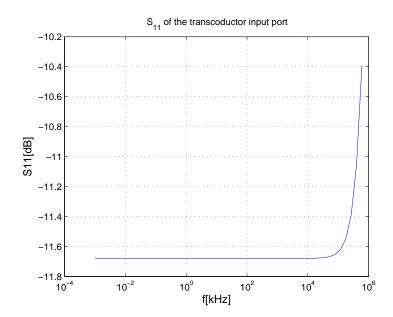

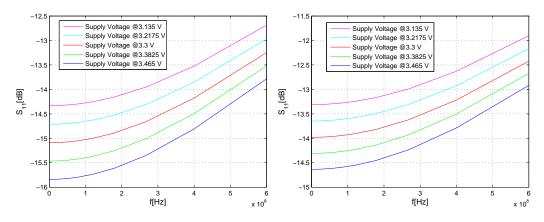

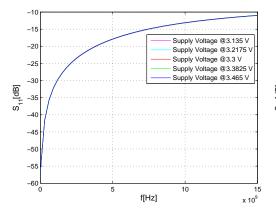

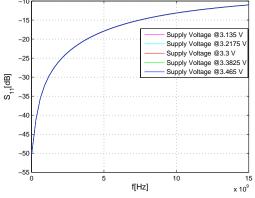

|          | 5.2            | Reflection coefficients                      | 122 |

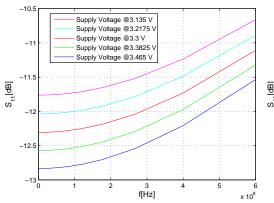

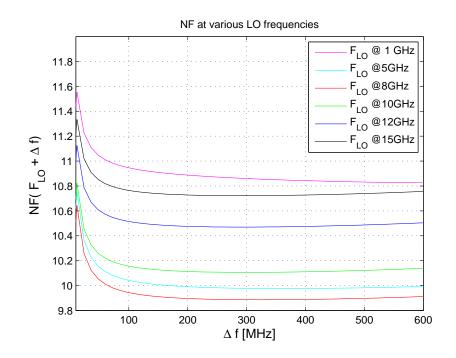

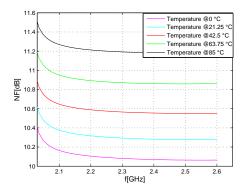

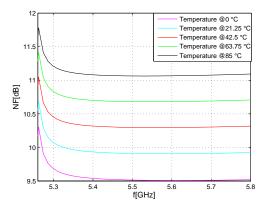

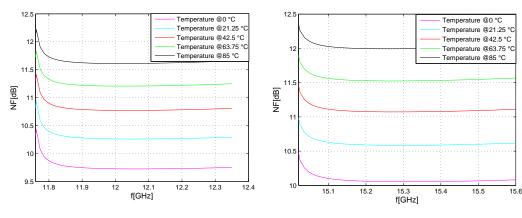

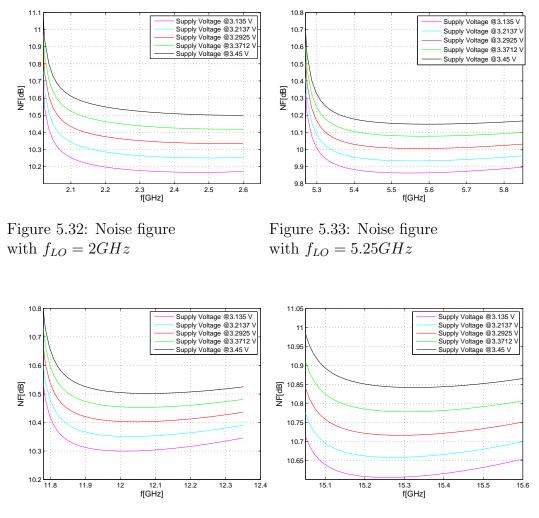

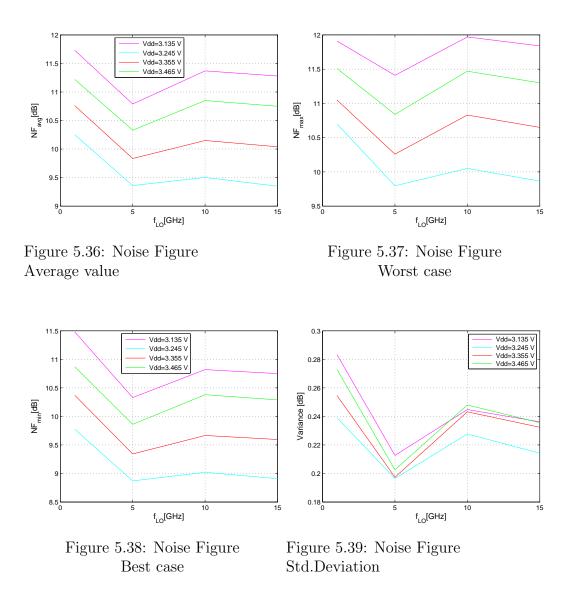

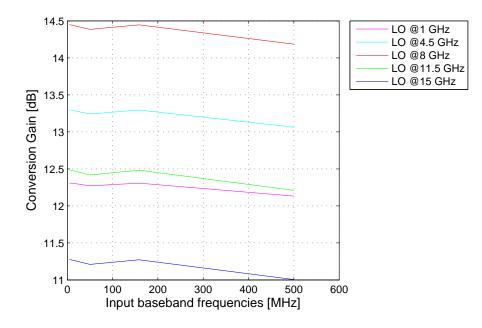

|          | 5.3            | Noise Figure                                 | 125 |

ii

| 6 | Summary |                                              | 145 |

|---|---------|----------------------------------------------|-----|

|   | 5.6     | MultiPath Polyphase Mixer simulation results | 143 |

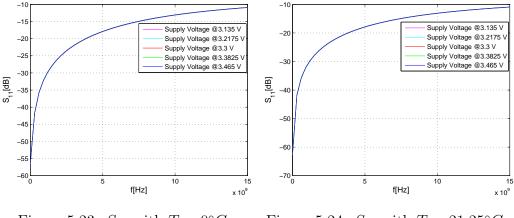

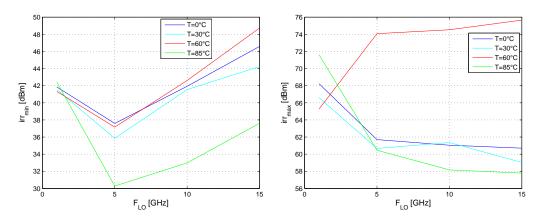

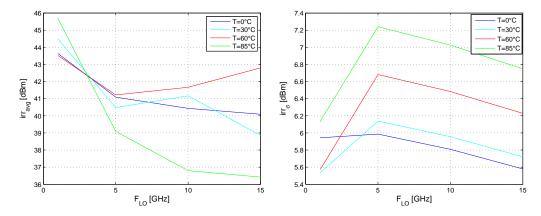

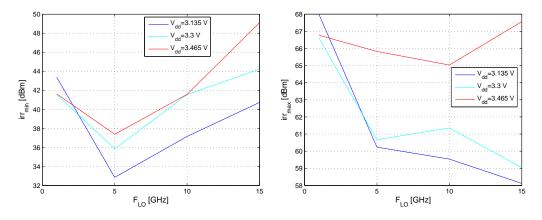

|   | 5.5     | LO feedthrough and Image Reject Ratio        | 138 |

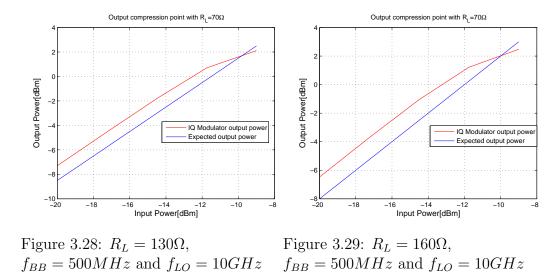

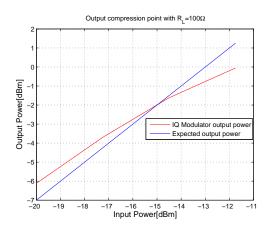

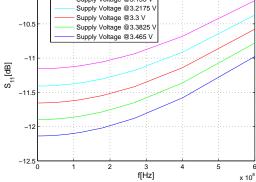

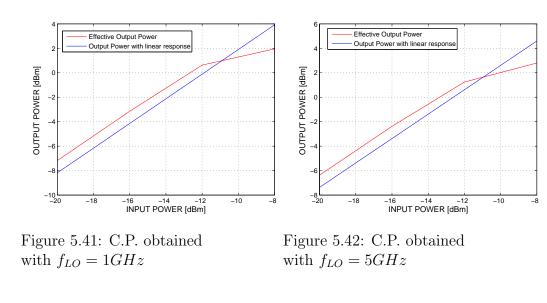

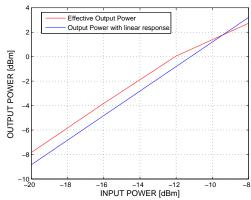

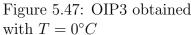

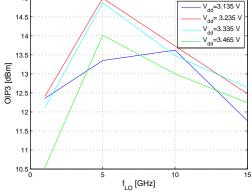

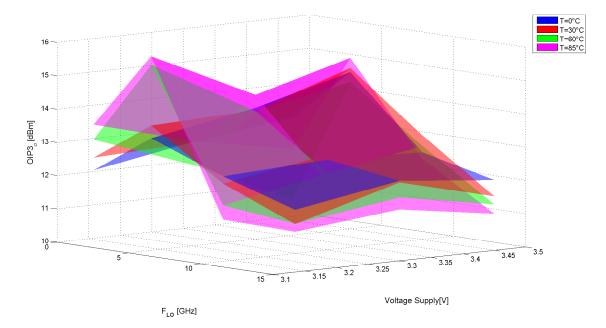

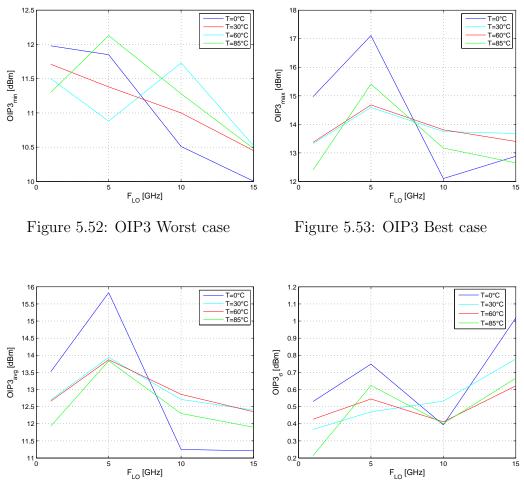

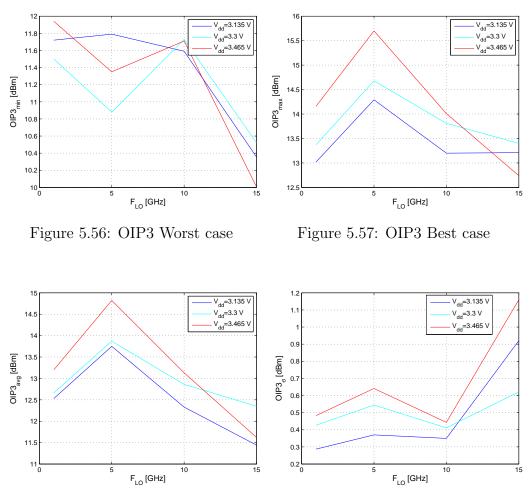

|   | 5.4     | Linearity                                    | 130 |

### CONTENTS

iv

# Acknowledgments

Ringrazio per la grande opportunità offertami in questi ultimi sette mesi, il prof. Andrea Bevilacqua e il Dott. Marc Tiebout.

Un caloroso grazie è rivolto ai miei colleghi e amici Stefan e Daniele, che hanno condiviso con me quest'ultima esperienza a Villach.

D'altra parte voglio esprimere la mia immensa gratitudine per chi mi aspetta a casa in Italia, coloro i quali mi hanno sempre sostenuto su ogni mia scelta, grazie di cuore ai miei genitori Mirna e Riccardo, mia sorella Monia e mio cognato Luca.

Fortunatamente sono circodanto da molti amici, che non mi hanno mai fatto mancare un motivo per sorridere, sarebbe impossibile scrivere tutti i loro nomi, quello che mi resta da fare è dire grazie a voi amici e amiche di ZV, siete una famiglia.

Concludo con chi da un anno a questa parte ha radicalmente cambiato la mia vita, teşekkürler Özgün.

### CONTENTS

vi

## Abstract

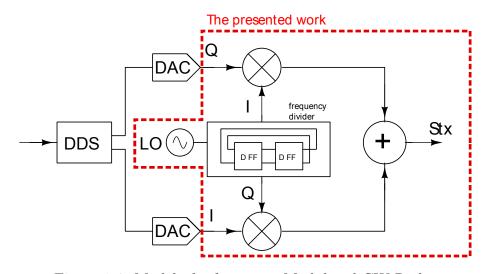

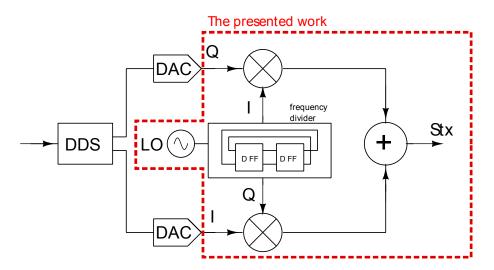

#### The presented work

Mixers and frequency translation are key processes in the wireless systems who have increasingly stringent requirements for transmission of a clean signal with a low noise floor and low intermodulation and harmonic distortion.

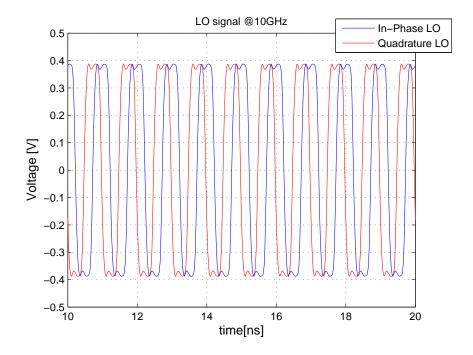

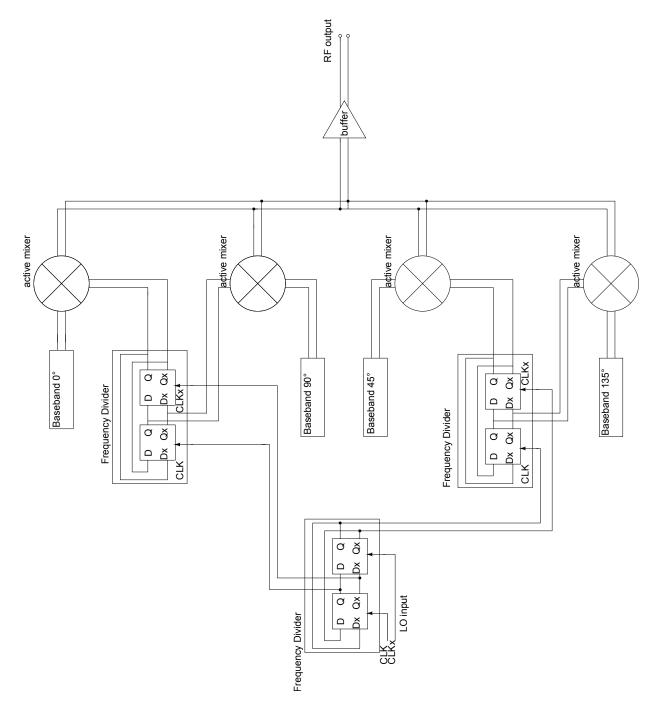

The desired upconverting IQ modulator has to translate a baseband starting at DC ending at 500 MHz, to a radio frequency range between 1 to 15 GHz, fed by a 2 to 30 GHz LO frequency, since the IQ LO signals are provided by a frequency divider driven at the double of the output rate.

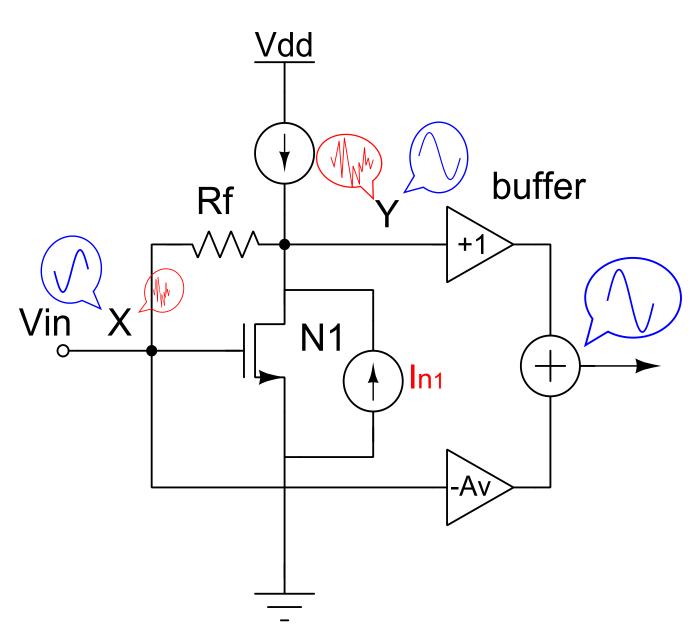

The core of the system is implemented by a couple of active mixers based on the Gilbert cell structure. All the system terminations are differential and have to be matched to the standard  $100\Omega$  equipment lab characterization. The design is oriented to reach a wide output dynamic range, reducing the total noise and ensuring a high linearity. These specifications are pursued taking advantage of the features provided by the SiGe BiCMOS technology. Since the baseband fits with the frequency response of the available CMOS devices, there is the opportunity to use them as linear transconductor of the active mixers. The larger range of linearity held by these devices, improves the intercept point reached by the modulator even without any degenerative topology. The trade-off represented in terms of noise performances, can be reduced by several solutions and the noise cancellation technique is a good candidate [4, 5]. By creating a highly linear and low noise transconductor cell, based on a CMOS noise canceling topology, and merging it with the performances of the

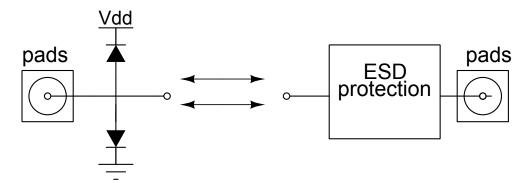

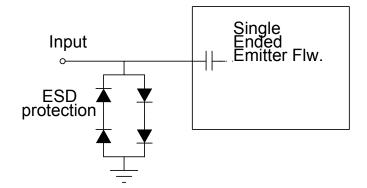

SiGe fast speed bipolar transistors, the designed structure achieves the single side band mixing with a output third order interception point greater than +10 dBm over the complete RF band, while the DSB noise figure is held below 12 dBm . The designed structures have a differential matched termination for all the input and output port, confirmed by a reflection coefficient kept lower than -10 dB. The design is supplied by a 3.3V single voltage and all signal pads are protected by ESD diodes. All the chip is analyzed and checked using Spectre and ADS tools. Hence, the modulator is implemented in a full-custom layout and the parasitic extraction is done. The problem of spurs deriving by the application of a square waveform as LO signal, which consequentially generates an unwanted higher order mixing, is investigated and a Multi-path Polyphase Mixer system is analyzed and simulated in order to indicate a way to suppress this distortion.

# Chapter 1

# Introduction

Nowadays the life has the aspect that we see thanks to the evolution of communications had within the last 20 years. The birth of the information era comes from the opportunity to communicate boundlessly, surpassing the concept of space distance. The exploit had by wireless communication networks, have contributed to the large diffusion of the radio frequency circuit design, which finds application in several areas as Voice and Data Telecommunication ( Cellular System, WiFi, WPAN and UWB), identification/security systems(Transponders, security scanners) and object identification and positioning (GPSs and Radars).

In a day by day more digital world, the analog radio frequency design is an undeniable segment of the communication industry since what we hear and perceive are analogs. But this reality now is assuming a new form, the manufacturers are trying to make digital the most of the signal processing during the communication, limiting the analog circuitry just to the interface with the antenna. Indeed digital circuits are more scalable than the analog counterparts, limiting costs and increasing the integration. Radio Frequency circuits include passive components which are difficult to shrink causing a slower scaling and raising the total chip cost. The research done to enhance the analog design, suppressing its deficiencies, is directed toward the development of new topology able to reduce the area effort and the total cost. Technologies act a fundamental role for the circuit optimization, providing new approaches to solve the aforementioned issues. The SiGe BiCMOS technology merges the proprieties of bipolar and CMOS into a single chip, combining the bipolar highspeed for the analog radio frequency operation with the low power consumption and the robustness of CMOS technology.

The developed modulator has to provide the upconverting translation in a Wideband Continuos-Wave Radar system. In this chapter is presented a first approach to these kind of systems, discussing the main applications and architectures available and analyzing their behaviors.

### 1.1 Radar Systems

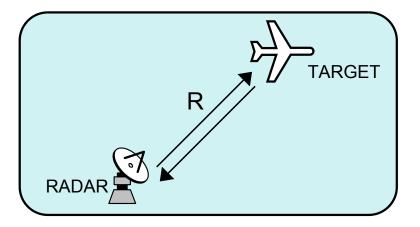

Radar is an acronym for Radio Detection and Ranging, the term radio is referred to the use of EM waves to detect the position and the velocity of a specific target.

Radars can be employed into different applications:

- Air Traffic and Maritime Navigation monitoring: The tracking and the positioning of aircraft and ships can be detected by the use of radar systems.

- Automotive: To reduce traffic fatalities, radar system employ active safety systems as adaptive cruise control, collision warning systems, blind spot detection.

- **Military**: The radar is applied in a manifold of defence and surveillance systems applications.

Two are the macro-typology of a radar system transmission:

- Pulse Radar : Pulses of energy are irradiated in the space. The detection and ranging part are accomplished by timing the delay between transmission of a pulse of radio energy and its subsequent return

Figure 1.1: Radar ranging

- Continuous-Wave radar : emits electromagnetic radiation at all times, irradiating continuous sine wave. CW radar can measure the instantaneous rate-of-change of target's range. This is accomplished by a direct measurement of the Doppler shift of the returned signal. The Doppler shift is a change in the frequency of the electromagnetic wave caused by motion of the transmitter, target or both. For example, if the transmitter is moving, the wavelength is reduced by a fraction proportional to the speed it is moving in the direction of propagation. Since the speed of propagation is a constant, the frequency must increase as the wavelength shortens.

The CW radars provide a greater flexibility than pulse radar, furthermore, it is also possible to use a CW radar system to measure the position instead of the velocity, by frequency modulation, the systematic variation of the transmitted frequency. The simplest way to modulate the wave is to linearly increase the frequency. In other words, the transmitted frequency will change at a constant rate. Frequency Modulated CW Radars (FMCW) measure the frequency of the return signal, compute the differences of the transmitted and received frequency, then the period of the difference is directly proportional to the time delay between transmission and reception, hence the position can be extracted. If R is the distance to detect, by transmitting a signal of frequency  $f_{tx}$ , modulated in a range  $f_1 < f_{tx} < f_2$ , and receiving a signal with frequency  $f_{rx}$ , the time delay between the two waveform is  $\tau = T \frac{f_{tx} - f_{rx}}{f_2 - f_1}$ , where T is the period of sweep from  $f_1$  to  $f_2$ .

The wanted distance is simply computed as  $R = c \cdot \tau/2$ .

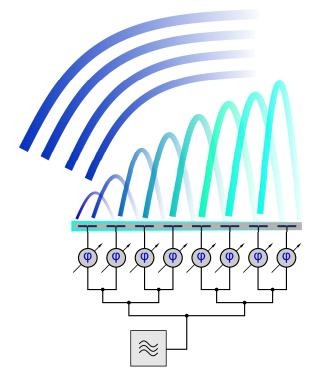

## 1.2 Monostatic Phased Array Radars

The proprieties to have a steerable beam to direct in a defined and narrow direction during the transmission and the reception of an EM wave in a radar system, is reachable without using further mechanical parts, but just installing an array of antennas and controlling it electronically. A linear phased array antenna is a series of equidistant antennas whose effective (summed) radiation pattern can be altered by phasing the signals of the individual elements. By choosing the difference of phase of the signals injected for each antenna, the irradiated beam can be steered providing a fast and programmable antenna target pointing.

Figure 1.2: Model of a phased array antenna

A phased array radar implementing the transmission and the reception of EM waves sharing the antennas in both directions, belongs in the category of monostatic radar, hence the transmitter and the receiver have a common antenna.

## 1.3 WideBand upconverter for tracking radars

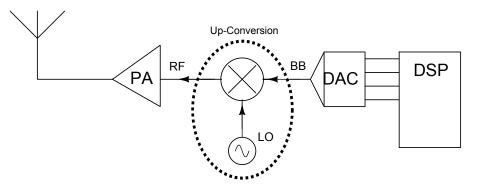

The objective in the design of communication module is to bring digital domain closer to the antenna at the receiving and transmitting ends using software defined radio. The phase shifting in digital beamforming is performed in the digital domain inside the digital signal processing. The module shown here (Fig. 1.3), illustrates how is implemented the signal path in a generic transmission module, which can deliver the phase shifted signal to the antenna array.

Figure 1.3: Model of a transmission module suitable for phased array antenna

The transmitting signal has to be translated in the transmission radio frequency range, by a mixer, this components is commonly followed by a power amplifier which properly boost the signal in order to make it suitable for the wanted transmission.

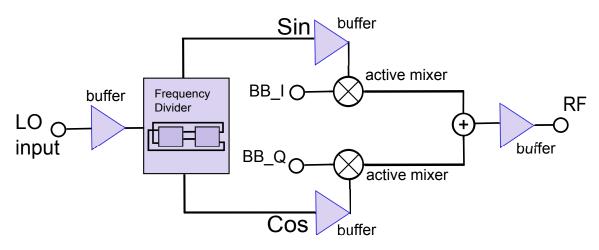

Due to that the modulation of the signal has to perform an important bridge between baseband and radio frequencies processing, ensuring a robust conversion. An available efficient implementation of a modulator is named single side band (SSB) mixer (see Fig. 2.1). The SSB mixer is the aim of this work.

The baseband signals are produced in the digital domain by a couple of DACs, which perform the initial phased delay to provide two IQ baseband signals. The LO signal feeds a frequency divider which generates the two IQ signals driving the couples of mixers employing the SSB upconverting modulation.

Figure 1.4: Model of a frequency Modulated CW Radar

## **1.4 Target Specifications**

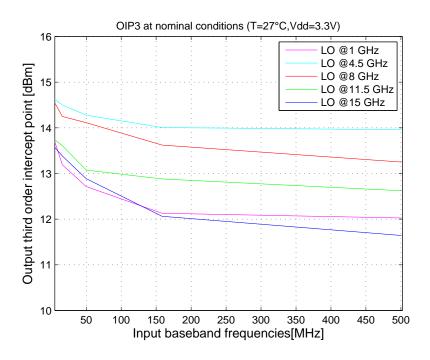

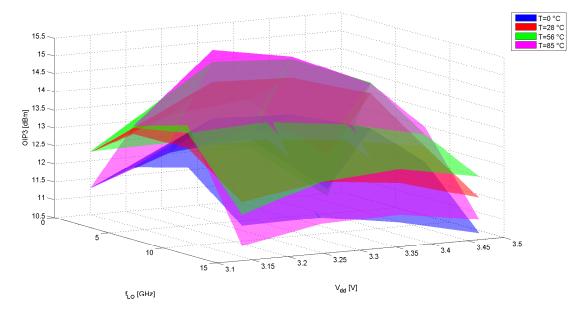

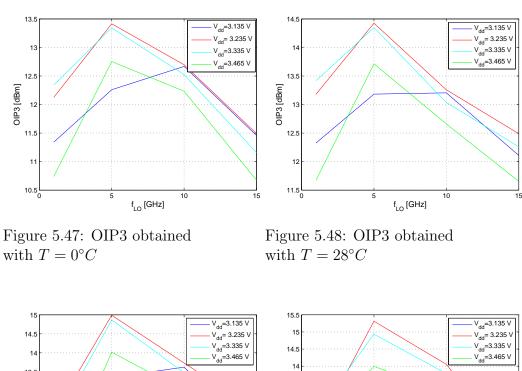

Upconversion mixers are fundamental modules in communication and radar systems converting the low frequency baseband (BB) signal to RF band. The noise figure which identifies the sensistivity of the circuit is a key of permonces of the upconversion mixer, delimiting the lower value of output power deliverable by the system. The compression point determines the maximum signal that the mixer can handle. The desired upconversion mixer has to guarantee a low NF and an high IIP3, describing a large dynamic range. Moreover, as discussed in the next chapter, applying an active mixer structure the focus of the design can not omit to verify an high image rejection and LO suppression.

All the performances for all the input and LO frequencies, have to be satisfied in a range of temperature from  $0^{\circ}$  to  $85^{\circ}$  and the a supply voltage variation of the 5%. Moreover, variations due process and mismatch have to be taken into account.

| Parameters                 | Target Value         |

|----------------------------|----------------------|

| RF Output Frequencies      | 1 15GHz              |

| Baseband Input Frequencies | 0500 MHz             |

| OIP3                       | $> 10 \mathrm{dBm}$  |

| SSB NF                     | < 12dB               |

| IRR                        | > 30 dBc             |

| LO Feedthrough             | $< 30 \mathrm{dBc}$  |

| Technology                 | b11hfc               |

| Supply voltage             | Single 3.3V          |

| Area effort                | Minimal (coils-less) |

## 1.5 Infineon BiCMOS technology

The available technology is a SiGe BiCMOS provided by Infineon Technologies [16], which makes possible to place on the same chip bipolar and CMOS devices. The enhancement is clearly understandable in the analog design when an application, as the wideband modulator is, requires processing of baseband signals and high radio frequencies signal in the same chip. The cost of a BiCMOS process is significantly higher than a normal full bipolar or CMOS technology.

### SiGe homojunction bipolar transistor

The performance advantages of SiGe over pure silicon for RFIC applications are mainly the extremely high cutoff frequencies,  $f_{max}$  and extremely low current-mode logic gate delay. Furthermore, improved power-added efficiency (PAE) at low DC voltages makes SiGe HBTs a good choice for power amplifier applications. SiGe bipolar transistors are bipolar transistors with the presence of germanium in the base region, which reduces the band gap of the SiGe material.

The normal design of a bipolar transistor, presents an higher emitter doping if compared to the base decreasing the emitter junction efficiency, that is the ratio of the electron current in the emitter, to the sum of the electron and hole diffusing across the base-emitter junction.

$$\gamma = \frac{I_{E_n}}{I_{E_n} + I_{E_p}} = \frac{1}{1 + \frac{D_p}{D_n} \frac{W_B}{L_p} \frac{N_A}{N_D}}$$

(1.1)

In order to increase the efficiency mentioned above, this technology does not give the opportunity to decrease the base at the doping without getting lower the transition frequency. Even decreasing the base width maintaining constant the dope density the efficiency cannot be enhanced not increasing the base resistance.

By using the germanium as the base of the bipolar transistor, the doping density at the emitter is decreased, whereas the base doping got lower. This causes an higher transition frequency allowed to the bipolars.

The available bipolars belonging to the SiGe HBT technology have different performances depending on the application which are designed for. High voltage HBT offers an higher collector-emitter drop voltage causing the breakdown at the bipolar junction, on the other hand, low voltage HBT provides an higher speed.

Seven are the available levels of metallization, six of cupper and one of alluminium. The metal stack allows to have short and small connection to the lower levels, being more resistive compared with the top levels. On the other hand, the upper level are used to carry high currents and to implement high Q inductor.

## 1.6 Figures of Merit

This chapter explains the basic figures of merit used during the design to better describe the system performances.

### 1.6.1 Gain and Conversion gain

In a common linear system, the gain referred to the voltage or to the power is the ratio between input and output signal, describing the processing employed by the block to its stimulus.

The gain of mixers and modulator must be carefully defined to avoid misunderstanding. In transmitter it is desiderable to raise the gain and hence the output swings of upconverter mixers.

The voltage conversion gain is the ratio of the rms voltage of the output modulated signal, to the rms voltage of the input modulating signal. The two waveform have different frequency, and it can be computed by applying, for istance in a upconversion mixer, a input cosine at  $\omega_{BB}$  and finding the amplitude of the upconverted component at the desired  $\omega_{RF}$ .

$$A_V = \frac{V_{RF}}{V_{BB}} \tag{1.2}$$

$$A_{V_{[dB]}} = 20log(A_V) \tag{1.3}$$

Traditionally the RF design, is characterized by a "power conversion gain", where the ratio is done on the output and input power signals.

$$G_P = \frac{P_{RF}}{P_{BB}} \tag{1.4}$$

$$G_{P_{[dB]}} = 10log(G_P) \tag{1.5}$$

#### 1.6.2 Distortion

The distortion analysis is a topic of high interest in matter of telecommunication circuits, being the cause of spurious frequencies. Every difference between the shape of the output waveform in the time domain and the input, net after a scaling factor, is a distortion effect. Distortion has as straight forward consequence the phenom of the compression, describing the upper limit of the signals which a system can generate.

The distortion here analyzed is the weak distortion, where the harmonics gradually disappear when the signal amplitude becomes smaller, then, the analysis is limited at the low distortion region where only second and third order distortion components are considered.

The most important case of distortion related to this design, is the nonlinear distortion caused by a system which has a nonlinear characteristic:

$$y = a_0 + a_1 u + a_2 u^2 + a_3 u^3 \tag{1.6}$$

If  $a_0$  represents the dc component and  $a_1$  the linear gain of the nonlinear system, the remaining coefficients reproduces the system distortion. An analytic expression of the output y, can give the  $a_i$  coefficients as:

$$a_i = \frac{1}{n!} \frac{\partial^i y}{\partial u^i} \Big|_{u=0} \tag{1.7}$$

By applying a cosine waveform  $u = U \cos(\omega t)$ , the output becomes :

$$y = \left(a_0 + \frac{a_2}{2}U^2\right) + \left(a_1 + \frac{3}{4}a_3U^2\right)U\cos(\omega t) + \frac{a_2}{2}U^2\cos(2\omega t) + \frac{a_3}{4}U^3\cos(3\omega t) + \dots$$

(1.8)

All the combinations of coefficients deriving from the cosine multiplication proprieties

are part of the distortion.

It is important to understand how much the linear response is compromised by the upper harmonics, thus, how is modified the signal component at the fundamental frequency. The Harmonic Distortion is defined as the ratio of the component of frequency multiple of  $\omega$  to the one at the fundamental.

$$HD_2 = \frac{1}{2} \frac{a_2}{a_1} U \tag{1.9}$$

$$HD_3 = \frac{1}{4} \frac{a_3}{a_1} U^2 \tag{1.10}$$

It is important to note that  $HD_2$  is proportional to the amplitude of the input signal, on the other hand the  $HD_3$  to the amplitude squared. This point spot the higher relevance of the third harmonic distortion in the most of the case.

#### Intermodulation

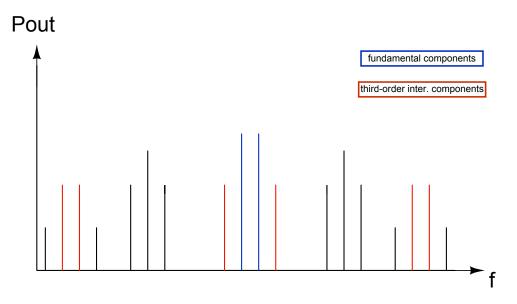

It is important to take into account the issue of two close harmonics as input, reproducing the case of a disturb at the input of the transmission system. Under low-distortion conditions, with two cosine waveforms of frequencies  $\omega_1$  and  $\omega_2$  injected at the input, then the output signal contains all the combinations of these harmonics and their multiples:  $k\omega_1 + m\omega_2$ .

The second-order intermodulation distortion  $IM_2$  is defined by the ratio of the component at frequency  $\omega_1 \pm \omega_2$ . Its third order version  $IM_3$  is detected at the the frequencies  $2\omega_2 \pm \omega_1$  and  $2\omega_1 \pm \omega_2$ .

$$IM_3 = \frac{3}{4} \frac{a_3}{a_1} U^2 = 3HD_3 \tag{1.11}$$

$$IM_2 = \frac{a_2}{a_1}U = 2HD_2 \tag{1.12}$$

The correspondence between third harmonic and intermodulation distortion is a reason why they are more important than the  $HD_3$ , in fact the value of  $IM_3$  is three times larger than the one of  $HD_3$  and this gets it easily measurable. Generally, a further characteristic that makes this distortion attractive in matter of design, is the close occurrence of the tone at  $2\omega_{1,2} - \omega_{1,2}$  to the fundamental tone. In a case of wideband response, this consideration is partially true: from Fig.( 1.5 ) is easily understandable that, more  $IM_3$  takes a more important role if the range of frequencies taken in account is wider. In place of design, is necessary to limit these components and shaping it by the active mixer frequency response.

Figure 1.5: Fundamental harmonics and third order intermodulation components [9].

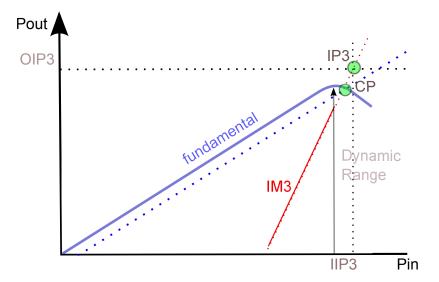

#### Third order intercept point

The point where both components coincide is the IP3, which has multiple correspondences with  $IM_3$ , making easier its computation.

$$IP_3 = \sqrt{\frac{4}{3} \frac{a_1}{a_3}} = V_{IN_{dB}} - \frac{1}{2} I M_{3_{dB}}$$

(1.13)

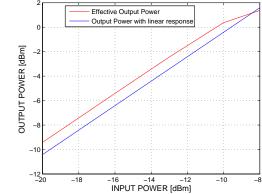

### **Compression** point

An alternative, less accurate way to characterize distortion is the -1 dB compression point, the input/output referred power when the output voltage is compressed by 1 dB. This value can be approximately calculated from (1.3), indeed the compression is caused by the  $a_3$  coefficient. Remembering that 1 dB of reduction is linearly a reduction to 0.122 :

$$V_{in,1dBc} = \sqrt{0.122\frac{4}{3}\frac{a_1}{a_3}} = \sqrt{0.122}IP_3 \tag{1.14}$$

In a dB scale the difference between IP3 and 1dB compression point is estimable of almost 10 dB, defining a wide used rule of the thumb.

Figure 1.6: Fundamental curves explaining the intermodulation distortion.

### 1.6.3 Noise Figure and SNR

The noise is unavoidable, having a intrinsic nature related to the system physic. It is just predictable by using statistics, and it can be reduced and minimized referring to the signal carrying the information. For the reception, elaboration and the transmission of the signal, it is important to measure the relative weight of the noise in comparison with the information carrier, in fact an important figure of merit is the Signal to Noise Ratio, the ratio between the power of the signal carrying the information and the overall power of the noise.

$$SNR = \frac{P_{signal}}{P_{noise}} \tag{1.15}$$

#### Noise in the time domain

Generally, the noise in the time domain can be described as statistic distribution of the instantaneous amplitude, since the noise derives from the superposition of an high number of elementary processes, in first approximation, uncorrelated, the distribution belonging to most of the case of the noise is the Gaussian distribution. The noise so has no first moment (equals to zero) and it is described just by the second moment, so by the root-main-square value and variance.

#### Noise in the frequency domain

Since the noise has to be referred with squared term in the time domain, the same has to be done in the frequency domain. Thanks to the Parseval theorem, the variance has to correspond the spectral power density of the noise:

$$\overline{x(t)^2_{\Delta f}} = \int_0^\infty S(f) df \tag{1.16}$$

The spectral power density is the Fourier transform of the auto-correlation function.

So for a small range of frequencies,  $\Delta f \mapsto 0$ , it is possible to do an acceptable error considering:

$$S(f) = \frac{x(t)_{\Delta f}^2}{\Delta f} \tag{1.17}$$

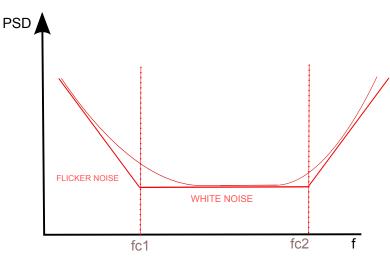

In the most of the cases of interest the spectral density of the noise power has a slope dependent on the frequency.

Figure 1.7: Usual power noise density spectre

At lower frequency the PSD has an  $\frac{1}{f}$  behavior, then a flat slope and then it raises again directly proportional with the frequency.

The flat part, called white noise is delimited by the two noise corner frequencies.

#### Noise response in a linear network

Describing a circuit with the two ports model it is possible to determine the output power spectral density generated by the two ports.

$$S_{out}(f) = \left|G\right|^2 S_i(f) \tag{1.18}$$

Where  $S_{out}$  is the output spectral density power of noise. When the circuits has more than one source, if every source is uncorrelated with the other (assumption applicable with a small error to the most of the cases), the total spectral density is derived by:

$$S_{out}(f) = \Sigma_i S_i(f) \tag{1.19}$$

#### The Noise factor

The most common representation of the magnitude with which the system degrades the signal during the elaboration, is the Noise Factor and the related Noise Figure. This two figures of merit are based on the comparison between the total output noise due to a noisy input termination and the total output noise due to a noise-less input termination. This input termination can not be whatever the designer wants, but has to be a simply and general termination suitable for the case of interest. For the radio frequency systems the common termination is purely resistive with a resistance of 50 $\Omega$  (75 $\Omega$  for the Television applications).

Hence, the Noise Factor is defined as:

$$F = \frac{\text{Total output power}}{\text{Output Power due to the input termination}} = \frac{SNR_i}{SNR_{out}}$$

(1.20)

Finally, the Noise Figure is the conversion of F in a dB scale.

$$NF = 10\log_{10}F\tag{1.21}$$

#### Noise sources

The physical noise sources assumed within the design noise analysis are:

- The thermal noise for resistors and MOSFETs, direct consequence of the fundamental mechanisms due to the energy state of a system.

- The flicker noise generated by the MOSFET, due the trapping-detrapping model describing the carrier fluctuation.

- The shot noise due to the flattening of the charge carriers, strictly related to its granular nature, acting a principal role in the bipolar transitors.

The thermal noise descends from the fundamental equations of the thermodynamic and from the energy quantization. The resistive thermal noise source is observed as the flattening of the voltage among its terminal or the current flowing through it and it can be represented by:

$$\overline{V_n^2} = 4kTR \tag{1.22}$$

$$\overline{I_n^2} = 4KTG \tag{1.23}$$

A MOSFET transistor at the thermal equilibrium is, by its nature, a resistive device and its dissipation is associated to a correspondent thermal noise source between the drain-source channel, modeled as:

$$\overline{I_n^2} = 4kT\gamma g_m \tag{1.24}$$

The coefficient  $\gamma$  takes in account the relation among conductance of the channel and transconductance, dependent of the geometry and the structure of the device. In a real device with short channel that coefficient assumes, in first approximation, values between 1 and 2.

In terms of thermal noise a bipolar transistor comprehends a noise sources for each parasitic resistor at its terminal, dominant is the source due to the base resistor. Further, this kind of device has a shot noise current source between its collector emitter terminations due to the base current:

$$I_n^2 = 2qI_B \tag{1.25}$$

At low frequencies the flicker noise is the most dominant contribution generated by a MOSFET transistor. The equation governing the flicker noise is given by:

$$\overline{V_n^2} = \frac{k}{C_{ox}WLf} \tag{1.26}$$

The complete bipolar shot noise comprehends a factor of proportionality  $\Gamma(f)$ , describing the transmission time of the charge carrier on the collector and the emitter region, which typically  $\Gamma(f) < 1$ . For the analysis it is simply taken into account as white noise.

### **1.6.4** Scattering Parameters

Microwave are preferable measured in term of power quantities than voltage and current, because the measurement of high-frequency voltage and currents in the laboratory are difficult, when a power measure is straightforward [1].

The scattering parameters can be obtained through the measurement of power quantities. A general two-port network can be fully described by the ratio of the incident and reflected waves at the input and output port with different of termination.

Figure 1.8: Two-port network model

The scattering matrix gives a relation the input and output waveform is given by:

$$\begin{bmatrix} b_1 \\ b_2 \end{bmatrix} = \begin{bmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \end{bmatrix}$$

(1.27)

Where the scattering parameters are defined as:

$$S_{ij} = \frac{b_i}{a_j}\Big|_{a_2=0} \tag{1.28}$$

The parameter  $S_{11}$  is the ratio of the reflected and incident waves of the input port, thus it represents the quality of the input matching being the reflection coefficient of the input port.

Equally, the parameter  $S_{22}$  measures the accuracy of the output matching and it is the output port reflection coefficient.

The s-parameters are frequency dependent and they assume complex values, for the overall project they are expressed in units of dB.

$$S_{m,n_{dB}} = 20 \log |S_{m,n}| \tag{1.29}$$

In microwave designs these parameters gives important information about a two-port behavior as matching, gain, isolation and even stability.

Since one requirement of the specifications asks to ensure the opportunity to test the chip once in the laboratory with instruments providing a 100 $\Omega$  differential termination, the input and output port of the system have to limit the reflection coefficient measured by  $S_{11}$  and  $S_{22}$  below of -10dBm, for the frequency range of interest.

$$S_{11} = \frac{Z_{in} - R_S}{Z_{in} + R_S} \tag{1.30}$$

$$S_{22} = \frac{Z_{out} - R_S}{Z_{out} + R_S}$$

(1.31)

#### 1.6.5 Unconditional Stability

For baseband and radio frequency circuits a must to follow during the design is the stability control, no oscillations have to be propagated along the circuit, since they can deteriorate the performances of the system or even compromising the total behavior.

20

By observing into a wide range of frequencies, in the microwave circuits some topology that in a first approximation do not include feedback path, at high frequency when parasitic components introduce further signal branches, can bring back part of the signal to the input, becoming a feedback system potentially unstable.

Several are the method to check the stability of a system, and by using the scattering parameters an intuitive way to explain and define the stable condition is made by observing the output and input reflection coefficients system.

In fact, a system is assumed unconditionally stable if  $S_{11} < 1$  and  $S_{22} < 1$ , for all passive load and source impedances.

A common measure of the unconditional stability can be made by using the Rollet's stability factor, which adds two useful scalar parameters:

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 - |\Delta|^2}{2|S_{12}S_{21}}$$

(1.32)

$$B_1 = 1 + |S_{11}^2 - |S_{22}|^2 - |\Delta|^2$$

(1.33)

Where  $|\Delta| = |S_{11}S_{22} - S_{12}S_{21}|$ , and both parameters are frequency dependent, since they derive from the s-parameters.

The Rollet's stability factors confirm the stability when is verified that K > 1 and  $B_1 > 0$ .

CHAPTER 1. INTRODUCTION

# Chapter 2

# System Blocks

Figure 2.1: Wideband Upconverting IQ Modulator

## 2.1 IQ Modulator

Single Side Band (SSB) Mixer or also called sideband rejection mixer plays a key role in the modern RF communication systems. SSB mixers reduce system cost and

complexity avoiding the need for expensive extra filtering blocks, do not adding more stage to the mixer to perform the filtering, preserving the complexity of the whole system.

These mixers simplify up-converting modulation by separating the up-converted lower sideband (LSB) from the upconverted upper sideband (USB). This separation is made by a phase cancelation technique. Dually, the same is done by the Image Rejection Mixers performing the down-conversion and suppressing the unwanted image band.

#### The Sideband Rejection

The SSBM provides a single-sideband suppressed carrier output. The input of the system consists in a pair of LO signals and of BB signals. The requirements for the input stimulus, the two keys for a good sideband suppression in a IQ modulator are:

- Balanced IQ baseband inputs: equal amplitude and quadrature phase

- Balanced IQ LO signals feeding the two mixers composing the modulator.

No design is perfect, and a certain amount of imbalance of LO and baseband paths is expected.

A conventional double balanced mixer has, as core, a multiplication between two signals in the time domain. If the two signals can be represented as two sines:

$$s_1(t) = A\cos(\omega_1 t + \phi_1) \tag{2.1}$$

$$s_2(t) = A\sin(\omega_2 t + \phi_2) \tag{2.2}$$

The output produced will contains two harmonics: one at the sum of the two frequencies and the other at the difference of them.

$$p(t) = \frac{AB}{2} \Big[ \cos(\omega_1 - \omega_2 + \phi_1 - \phi_2)t + \cos(\omega_1 + \omega_2 + \phi_1 + \phi_2)t \Big]$$

(2.3)

If two mixers are connected to each other, due to the difference of phase among the two paths, a LSB or USB output can be selected by choosing which in-phase port to drive with the base-band signal.

In fact, under ideal balanced conditions, the system work as follows:

- At the top mixer a  $\sin(\omega_{BB}t)$  baseband signal and a  $\sin(\omega_{LO}t)$  LO signal are mixed.

- The output of the top mixer consists of two terms:

- 1.  $\frac{1}{2}A\cos(\omega_{LO}-\omega_{BB})t$  in the lower sideband.

- 2.  $-\frac{1}{2}A\cos(\omega_{LO}+\omega_{BB})t$  in the upper sideband with 180 degrees of shift.

- If the bottom mixer is fed with a LO signal in quadrature of phase referenced to the previous, and a quadrature signal even for the baseband, the mixing result will consist in:

- 1.  $\frac{1}{2}A\cos(\omega_{LO}-\omega_{BB})t$  in the lower sideband.

- 2.  $\frac{1}{2}A\cos(\omega_{LO}+\omega_{BB})t$  in the upper sideband with no shift of phase.

- Hence, if the output of the two mixers is summed:

- 1. The two lower sideband terms are added in-phase and produce the desired low-side output signal

- 2. The two upper components are summed in out-of-phase and canceled.

- If the I and Q components are swapped, the upper sideband terms add in-phase, and the lower sideband terms are canceled.

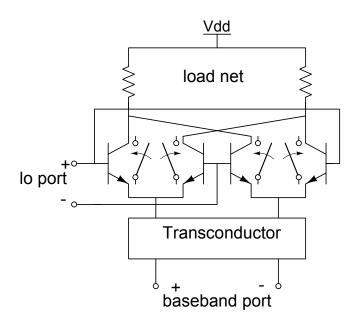

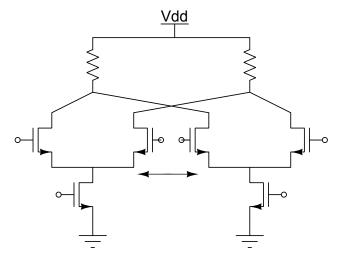

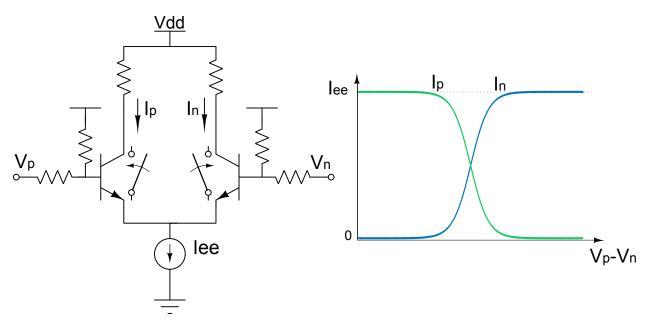

# 2.2 Current Commutating Mixers

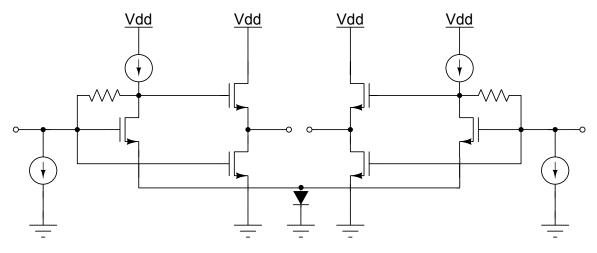

Figure 2.2: Model of a Gilbert Mixer [13]

To achieve high port isolation, gain conversion and low noise an active mixer topology is preferable than a passive mixer, despite it could achieve a better linearity. The double balance active mixer [13] here shown is based on a double crossed differential structure . It is composed by a switching cell driven by the LO signal and acts the modulation by steering the current provided by the driver transconductor stage, performing the conversion of the input voltage signal into a proportional current.

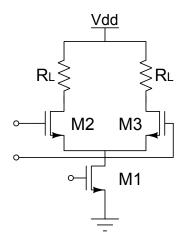

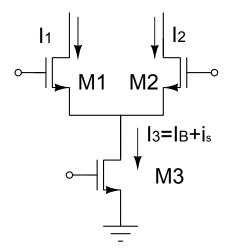

The switching cell is called also Gilbert Cell by the name of the creator of this structure. This topology is born to execute a precision multiplication of the currents flowing through it. Half of a Gilbert Mixer, called single balanced mixer, is here presented in the full CMOS version. The transistor M1 converts the input BB voltage to a current the upper differential pair M2-M3 steers this current to the left and to the right.

Then, this current flows reaching the output network composed by two resistors, converting it in the final modulated output voltage. With the complete structure the

Figure 2.3: CMOS single balanced mixer

BB signal is available in differential form, if the transconductor provides differential output then the active mixer must be modified accordingly. The differential structure implies the advantage of the LO feedthrough suppression.

## 2.2.1 The Conversion Gain

In Fig.2.3 half a mixer is visible. M1 produces a small-signal drain current equal to  $I_{ds_1} = g_{m1}V_{BB}$ , if we assume the presence of an abrupt LO switching, the switching cell acts the multiplication of  $i_{BB}$  by a square wave commuting between 0 and 1, called S(t).

$$I_1 = I_{RF}S(t)I_2 = I_{RF}S\left(t - \frac{T_{LO}}{2}\right)$$

(2.4)

By resolving the DC path starting and closing on the supply voltage comprehending the output voltage:

$$V_{out} = V_{DD} - I_1 R_1 - V_{DD} + I_2 R_2 \tag{2.5}$$

And ensuring the balance with  $R_1 = R_2 = R_{out}$ , the output voltage can be written

as:

$$V_{out} = I_{BB} R_D \left[ S \left( t - \frac{T_{LO}}{2} \right) - S(t) \right]$$

(2.6)

The multiplication of a square wave toggling between 0 and 1 and  $I_{BB}$ , can be represented expanding the square wave by the Fourier series:

$$V_{out} = I_{BB}(t) R_{out} \left[\frac{4}{\pi} \cos \omega_{LO} t....\right]$$

(2.7)

Figure 2.4: Interconnecting two single balance mixer it is possible to obtain the full differential network

Referring now, to the full differential version, the double active mixer if the baseband input signal is a sinusoidal wave form at the frequency  $\omega_{BB}$ , the output signal, in first approximation, will be :

$$V_{RF} \simeq \frac{2}{\pi} g_m R_{out} V_{BB} \Big[ \cos(\omega_{LO} - \omega_{BB}) t + \cos(\omega_{LO} + \omega_{BB}) t \Big]$$

(2.8)

So the voltage conversion gain is therefore equal to:

$$A_{V} = \frac{V_{RF_{p}}}{V_{BB_{p}}} = \frac{2}{\pi} g_{m1} R_{out}$$

(2.9)

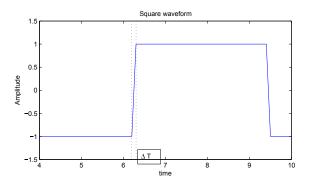

The conversion gain is reduced by the non-ideal toggling computed by the switching cell. If the single-ended Lo waveform during  $\Delta T$  is switching the state the total conversion gain is equal to :

$$A_V = \frac{2}{\pi} g_{m1} R_{out} \left( 1 - \frac{2\Delta T}{T_{LO}} \right) \tag{2.10}$$

A bipolar double active mixer presents the same behavior and the analysis aforementioned can be applied even to it.

### LO Feed-through Suppression

As seen previously, analyzing the single balanced mixer, the switching cell behavior has the consequences of to modulate the transconductor output current by a square wave. Being single-balanced, this topology has the defect to multiply the signal  $V_{LO} \cos(\omega_{LO}T)$  to the current  $i_{BB}(t)$ , which contains even a DC component. The unwanted mixing carries out from the mixer a component at the same frequency of the LO, disturbing the overall transmission. This unexpected output, called LO Feed-through, can be avoided just using a useful feature provided by the doublebalanced Gilbert Cell. In fact this topology has the advantage to provide as output the differences between the resistor voltages, which are equal to :

$$V_{p,n} = \pm \frac{2}{\pi} [\cos(\omega_{LO}t)] \Big[ I_{DC} + g_m V_{BBp,n} \cos(\omega_{BB}t) \Big]$$

(2.11)

The DC component is transported by both branches to the output, as their difference, comes out without LO component.

It is important to clarify that this condition is verified, just when a perfect balancing of the circuit is guarantee.

### Port isolation

Ideal double-balanced mixer means the circuit is perfectly symmetrical without any parasitic effects. In fact the even harmonics of the baseband port are canceled due to the symmetry of the circuit. In this case the LO leakage is in the noise level so it is concluded that there is no LO feedthrough for an ideal double balanced mixer. In the real circumstance, there are no ideal conductors and connections, and they must be considered as resistors and capacitors. Parasitics and non-ideal effects, are the causes of the presence of unexpected components into the output when a real circuit is implemented.

### 2.2.2 Noise analysis

The main target of this project is to ensure the widest dynamic range (D.R.) achievable for the signal transmitted. The lower bound of the D.R. is bounded by the floor noise, thus, referring to the output, the smallest signal at the output generated by amplifying the noise. So the noise gives the limits to the sensitivity of the system, in fact a signal with an amplitude lower than the noise floor can not be distinguished and the system can carry information just having signals with higher amplitudes.

The enhancement of the noise floor and consequentially, of the D.R. could be done, principally by two ways:

- Using noise-less components or low noise architecture

- Using a post-process elaboration of the signal called optimum filtering.

In this up-converter system no inductors are inserted, to save the area of the circuit and further, no additional filtering will be implemented for this full-analog up converting block.

#### Noise in frequency translator systems

A frequency translator system is inherently noisy because noise is transferred from idler frequencies to the output. The input at base-band frequencies, carry an unwanted amount of noise and the frequency shifting, since spreads the input to multiple frequencies, will fold even the input signal PSD into multiple side-bands. The noise figure in a mixer is defined as the SNR at the baseband port (input) divided by the SNR at the RF port (output). In a typical mixer the output signal stands over over two output sidebands. The existence of a double sideband increases the difficulty of the noise figure computation, and this fact in the most of the case lead to defines two different NF definitions.

- When just one side-band carries the useful signal and the other side-band contains just the noise the noise figure computed over the output frequencies is called Single Side Band NF (SSB).

- When the signal exists on both side band frequencies, the NF is called Double Side Band (DSB).

If both sidebands have the same conversion gain through the system the DSB NF is 3 dB lower than the SSB NF.

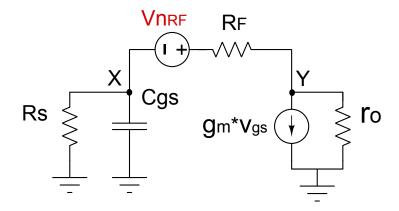

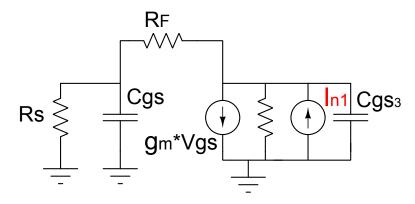

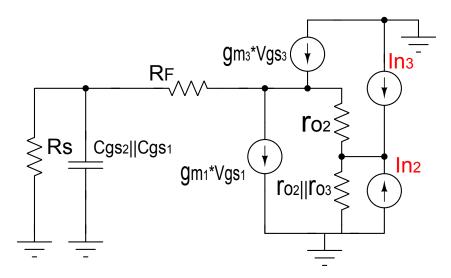

### Noise in Current-Commutating CMOS Mixers

Since frequency conversion means not a linear time invariant behavior, its noise could not be analyzed with conventional circuit techniques. Fast estimation of the noise performances is preferable because this capability facilitates design optimization and accelerated the design steps. The Gilbert cell contains a transconductance stage, which is, in the most of the cases, reported as a differential pair biased at a fixed operating point, anyway this analysis comprehends even more sophisticated kind of transconductors. The Gm-Cell is connected to feed with an output current the switching pairs driven by the LO signal. It is easier and useful to consider half a Gilbert cell, shown in Fig.2.5. The noise

Figure 2.5: Single balance noise analysis

generated by the mixer has a periodically time-varying statistics, because the operating point changes periodically in the time domain and a random process whose statistics are periodic functions of time is called cyclostationary. In this case, the power spectral density is not just function of the frequency but being time variant is function even of the time.

A good approach to understand the mixer noise behavior is to compute the time average PSD and then evaluate the noise figure.

Figure 2.6: LO square waveform driving the switching cell

Considering the thermal noise generated in M1 and M2 assuming that they remain in saturation during the part of the period they are on. Neglecting capacitive effects when M1 or M2 is off the output current is determined by the transconductor output current and the switching block doesn't contribute on the output noise.

During the time interval  $\Delta T$ , which bounds the commutation mode, both M1 and M2 are on and they contribute to the output noise.

IF the LO amplitude  $V_{LO}$  is high during the commutation,  $\Delta \to 0$  this output noise added by the switches is negligible. The flicker noise generated by the switching cell is translated and folded around the DC but not around  $f_{LO}$  [8].

It is important to underline that the same analysis can be applied to a switching cell composed by bipolar.

Referring to (2.5), the transconductor delivers its noise current  $i_n(t)$  to the output, modulated by the effects of the switches driven by the LO voltage.

$$i_{out_n} = i_s(t) \cdot p(t) \tag{2.12}$$

The time average PSD is:

$$S_{out}(f) = \sum_{n=-\infty}^{\infty} |p_n|^2 S_{N3}(f - nf_{LO})$$

(2.13)

Considering the noise source as white for the whole baseband and if the LO has a large amplitude, the modulating signal can be expressed as a square wave form, hence :

$$\Sigma_{n=-\infty}^{\infty} |p_n|^2 = 1$$

$$N_{N3} = \Sigma_{n=-\infty}^{\infty} S_{N3} (f - n f_{LO})$$

Thus  $S_{out}(f) = N_{N3}$ .

The contribution of the different sidebands in the case of the square-wave form

approximation comes for the most percentage from the frequencies between  $f_{LO} \pm f_{out}$ , where  $f_{out}$  is the output frequency.

Finally, a large LO amplitude increases the conversion gain and reduces the noise contribution of the switching pair and the LO port. After a certain value, the conversion gain of the switching pair reaches its maximum value  $\frac{2}{\pi}$  and the noise contribution of the switching pair reaches its minimum. Further, the PSD of the total mixer can be calculated with linear circuit techniques and the total SSB noise figure can be easily computed.

Finally, in an upconverting mixer the flicker noise related to the devices composing the transconductor is up-converted and translated at the beginning of the side-band of interest [23].

## 2.2.3 Linearity assumption

Linearity is a very important issue because it brings many problems as gain compression or intermodulation distortion, phenoms measured by the second-order intercept point (IP2), third-order intercept point (IP3), and 1-dB compression point (P1dB). Therefore, it is a great challenge to achieve high linearity at low power and low voltage [9].

Into the implemented IQ Modulator the two main blocks consist of two mixers, which will act the phase canceling to provide the single sideband signal. It is clear that, these two blocks will limit the overall linearity of the system, and their design will set significantly the performances of the whole circuit.

Any mixer working as frequency converter bases its operation on a generic nonlinearity, consequently the output consists of a large quantity of components and only one is the desired compromising linearity performances and the quality of the mixing.

The employed double balanced active mixer offers as benefit the opportunity to preserve the linearity in terms of LO feed-through which, in case of a perfect balance of the structure, is totally supressed. The linearity is mostly dominant by the transconductance stage, therefore, it is very important to have a linear voltage to current transformation.

A common topology, acting a suitable V-I conversion in the active mixer can be, as widely seen, the differential pair (2.5).

This topology being differential does not present second-order distiortion. The differential output current  $i_{od} = i_1 - i_2$  is twice the ac current of each transistor, and the relative current swing is given by:

$$i = \frac{i_{od}}{I_3} = \frac{v_{id}}{V_{GS} - V_T} \sqrt{1 - \frac{1}{4} \left(\frac{v_{id}}{V_{GS} - V_T}\right)^2}$$

For small value of  $v_{id} < (V_{GS} - V_T)$ , the square root can expanded as a power series:

$$\sqrt{1-x} = 1 - \frac{x}{2} - \frac{x^2}{8} - \frac{x^3}{16}$$

and limiting to the first term the differential output current becomes:

$$I_{odp} = \frac{I_3}{v_{GS} - V_T} \cdot V_{id} = gm_1 \cdot V_{Id}$$

(2.14)

Assuming the  $\frac{V_{idp}}{V_{GS_3}-V_T}$  and  $i_p$  as output the coefficients of the nonlinear response are:  $a_3 = -\frac{1}{8}$  and  $a_1 = 1$ .

Finally, the IM3 can be expressed as:

$$IM_3 = 3HD_3 = \frac{3}{32} \left(\frac{V_{idp}}{V_{GS_3} - V_T}\right)^2$$

(2.15)

and

$$IP_3 = 4\sqrt{\frac{2}{3}}(V_{GS3} - V_T) \tag{2.16}$$

The IP3 of a common-source transistor rises with the overdrive, eventually reaching a relatively constant value.

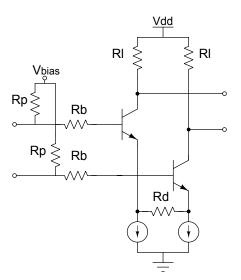

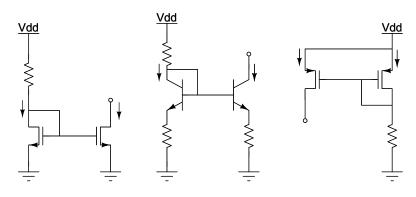

## 2.3 Frequency division

The static frequency divider is a fundamental block for various applications, within mobile or satellite communication systems and multiple optic fiver systems. The high speed needed to achieve this duties is released by the Current Mode Logic frequency dividers, that unfortunately exhibits an high static power consumption.

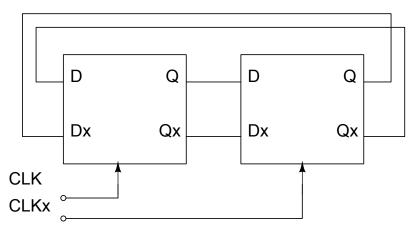

Figure 2.7: The frequency divider implemented by a master slave flip-flop topology

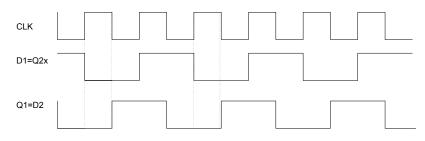

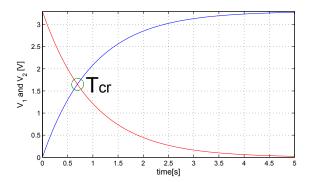

The common frequency divider is based on a flip-flop circuit architecture implementing a counter, as shown in Fig.2.7. This architecture is primarily a master-slave flip flop with a negative feedback. This circuit works by continually toggling the output state per each clock cycle. The mechanism effectively causes the output to commute between one and zero at the rate of half the input clock. In this way frequency division is achieved. The Fig.2.8 shows the clock pulses and the output from each of the latches explaining the circuit action. In high speed master-slave configurations the slave behaves as the dual of the master so that they can be both driven by a single clock. To do that, the divider utilizes two identical latches that are driven by complementary clocks CLK and CLKx.

### 2.3. FREQUENCY DIVISION

Figure 2.8: Clock and Flip Flop based divider operation

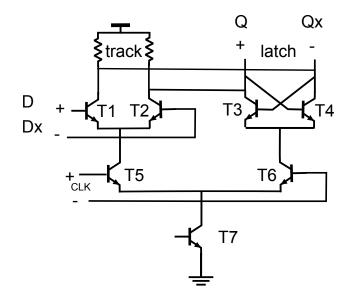

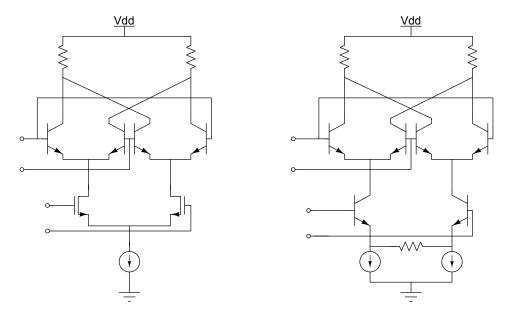

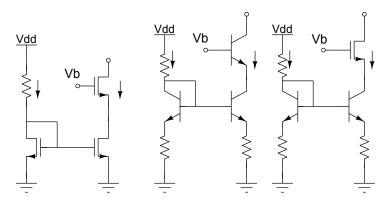

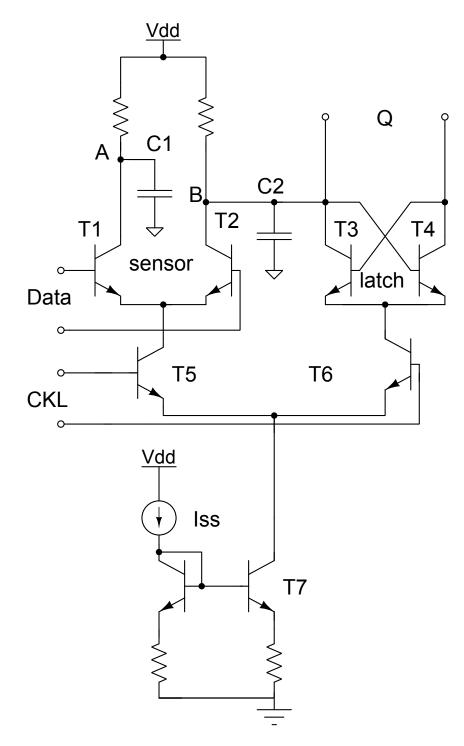

The high speed D flip flop are designed using current-mode logic circuits Fig. 2.9. In the conventional CML latch topology, the track and the latch modes are determined by the clock signal, driving a second differential pair. When the signal CLK is 1, the circuit operates in the tracking mode, where the current from T7 flows entirely through the tracking differential pair T1 and T2, thereby allowing  $V_{out}$  to track  $V_{in}$ . During the latch-mode, the signal  $V_{CLK}$  is held low and the tracking stage is disabled. Further, the latch pair is enabled storing the logic state at the output. This topology is suitable to work at frequencies of various GHz.

Figure 2.9: CML D Flip Flop

## 2.4 WideBand spurs issues

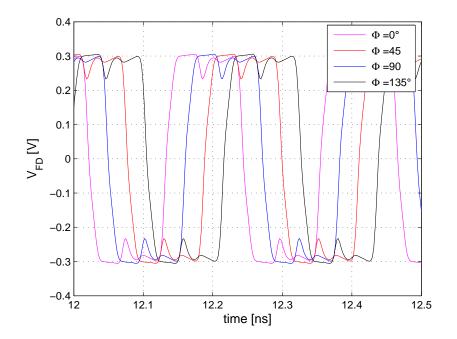

As repeatedly observed in the previous sections, the Gilbert Mixer can be used as a flexible tool to achieve the frequency translation, thanks to some assumptions making it easily analyzable, even if it is strictly based on a nonlinear time variant system. If noise and linearity designs are closely related to the transconductor behavior, neglecting further parts of the topology, is direct consequence of the hard switching acted by the Gilbert cell. An hard driven commutation is verified if the LO signal assumes a square waveform, with negligible toggling time. By observing the system performances in a wideband range, it is important to take into account the spectre belonging to the square waveform. In fact, it is composed by an infinite series of odd harmonics, responsible of a related series of wanted and unwanted mixing, with the baseband signals. The unwanted mixing, even if has a lower harmonic amplitude, degrades the linearity of the IQ Modulator, adding spurs upon the output band of interest with the lower LO signal frequencies: for instance, it is clear how a 3GHz LO signal, can produce a further mixing close to the 9GHz harmonic disturbing the overall transmission. So it is useful to fix these further spurs, avoiding the addition of extra components but rather reusing blocks already available. A filterless polyphase modulator can be performed by a parallel wideband mixers interconnection.

# 2.5 Multipath Polyphase Filtering

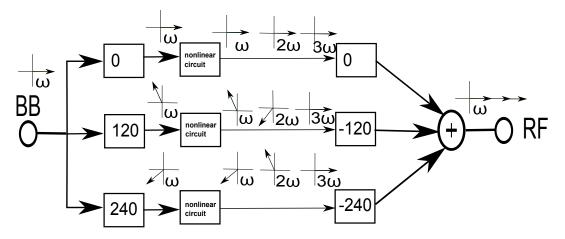

As mentioned, unwanted spectral components can be canceled by a polyphase multipath technique. The basic idea is to split an input signal into N paths [10]. Each branch contains a phase shifter followed by a nonlinear circuit and an additional phase shifter. The nonlinear circuits are identical, on the other hand, the phase shifts differs for every path. All the output of the different branches are added to get the output signal.

This structure allows a constructively addition of the wanted signal if the desired

signal paths have equal phases before the summing node. The undesired signals (results of various distortion products) should have a different phase at the end of every path and the phase differences between the paths should be chosen in such a way that the unwanted signals are canceled.

Harmonics suppression technique

Figure 2.10: Multipath Polyphase harmonics suppression technique [10].

By combining the phase shifts of all the phase shifters into the vector:

$$\varphi = [\varphi_1, \varphi_2, ..., \varphi_N] \tag{2.17}$$

All the phase of the signals after the first phase shifters are  $\underline{\varphi}$ , and the nonlinear circuits generates harmonics of these signals.

By assuming that the circuits are weakly nonlinear, and if all the nonlinear circuit input can be represented as  $x_i(t) = \cos(\omega t + \varphi_i)$ . It is easily demonstrable [10] how the fundamental harmonic component, before the last phase shifter, is a scaled version with the same phase of the input  $x_i(t)$ , but the unwanted components cause by the nonlinear circuit, having a frequency multiple of the fundamental, have phases following the relation:

$$\underline{\varphi}_{nonlinear_n} = n\underline{\varphi} \tag{2.18}$$

The phase shifters after the nonlinear circuits set the phase of the desired signal back to zero, consenting the constructive addition. The higher harmonics take the same phase shifting, and their phases before the adder become:

$$\underline{\varphi}_{s,n} = (n-1)\underline{\varphi} \tag{2.19}$$

These components can be canceled. Indeed, by setting the first phase shifting equidistant between each paths:

$$\underline{\varphi} = [0 \cdot 360/N, 1 \cdot 360/N, ..., (N-1) \cdot 360/N]$$

(2.20)

then the (2.19) can be rewritten as:

$$\underline{\varphi}_{s,n} = \frac{n-1}{N} [0 \cdot 360/N, 1 \cdot 360/N, ..., (N-1) \cdot 360/N]$$

(2.21)

This equation shows that whenever  $n = p \cdot N + 1$ , the phase in every path will be a multiple of 360° leading to constructive addition. It can be shown that in all cases when  $n \neq p \cdot N + 1$ , the phases are distributed equidistantly over 360°, leading to cancellation.

| Phase of $\underline{s}$ | 0        |               | $\pm 2\omega$  | $\pm 3\varphi$           | $\pm 4$                    | -50            | $\pm 6$        | $\pm7\varphi$     |

|--------------------------|----------|---------------|----------------|--------------------------|----------------------------|----------------|----------------|-------------------|

| Ν                        | <u>U</u> | $\pm \varphi$ | $\pm 2\varphi$ | $\frac{\pm 3\varphi}{2}$ | $\underline{\pm 4\varphi}$ | $\pm 5\varphi$ | $\pm 6\varphi$ | $  \pm i \varphi$ |

| 2                        |          | С             |                | С                        |                            | С              |                | С                 |

| 3                        |          | С             | С              |                          | С                          | С              |                | С                 |

| 4                        |          | С             | С              | С                        |                            | С              | С              | С                 |

| 5                        |          | С             | С              | С                        |                            |                | С              | С                 |

Table 2.1: Table indicates whether harmonics are canceled ("C") or not (blank), depending on their phase from eq. (2.19) (columns) and number of path rows(N)

Table (2.1) can be used to see if a harmonic with this phase is canceled or not by a certain number of paths.

#### **Canceling of Intermodulation Products**

The canceling of intermodulation products can be analyzed in the same way as the canceling of the harmonics. It can be shown [10], that an intermodulation product at  $k\omega_1 + m\omega_2$ , with k and m positive or negative, will have a phase of  $(k+m) \cdot \underline{\varphi}$ , after the nonlinear circuits and a phase of  $(k+m-1)\varphi$  before the adder. Therefore, if the  $n^{th}$  harmonic is canceled, even the intermodulation products at  $k\omega_1 + m\omega_2$  with k + m = n will be canceled.

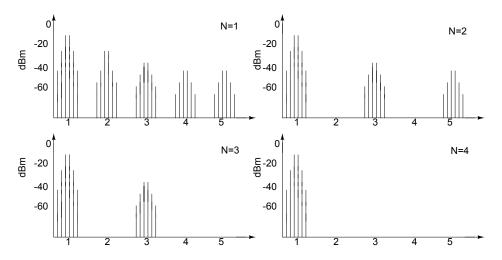

Figure 2.11: Output spectra of a polyphase multipath circuits several paths (two-tone test) [10].

# 2.6 Multipath Polyphase Mixer

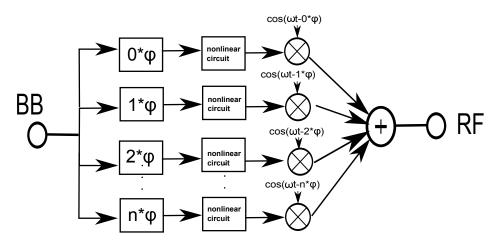

Figure 2.12: Multipath Polyphase Mixer [10].

An important point to guarantee a wideband perfomance, is to ensure a constant phase shifting over all band. After the nonlinear circuit the band of interest is greater than before it.

RLC filters, often implemented as phase shifters, but present difficulties in order to work over a wide band spectre with a constant phase shift.

The already discussed Gilbert Mixers, can in princible implement the needed phase shifters, making an active wideband filtering. The mixer will introduce even the required frequency shifting, completing the IQ Modulator with polyphase path structure.

Finally, the harmonics of the LO signal will also be mixed, as previously anticipated, gives an extra spectral components that can be included to the undesired harmonics to delete.

It is possible to create a straight forward correspondence of what already seen in matter of delectable harmonics with all spurs that an active mixer can produce. If the desired signal is in the upper sideband, while a positive n means that the  $n^{th}$  harmonic is in the upper sideband and a negative n means the the  $n^{th}$  harmonic is

### 2.6. MULTIPATH POLYPHASE MIXER

in the lower sideband, (2.19) changes to :

$$\underline{\varphi}_{s,j,n} = \begin{cases} (n-j) \cdot \underline{\varphi}, & n \ge 0\\ (-n+j) \cdot \underline{\varphi}, & n < 0 \end{cases}$$

(2.22)

So, to delete a spectral component at  $j\omega_{LO} + n\omega_{BB}$  with at  $\omega_{BB}$  the input baseband signal and  $j\omega_{LO}$  an undesired LO harmonic component, is necessary to create a polyphase multipath mixer of N paths, with N verifying:

$$n = j + p \cdot N \tag{2.23}$$

| n<br>j | -5                     | -4                     | -3                    | -2                     | -1                    | 0                      | 1                      | 2                      | 3                      | 4                      | 5                      |

|--------|------------------------|------------------------|-----------------------|------------------------|-----------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| 0      | $5\underline{\varphi}$ | $4\underline{\varphi}$ | $3\varphi$            | $2\underline{\varphi}$ | $1\varphi$            | 0                      | $1\underline{\varphi}$ | $2\underline{\varphi}$ | $3 \varphi$            | $4\underline{\varphi}$ | $5\underline{\varphi}$ |

| 1      | $6\varphi$             | $5\varphi$             | $4\varphi$            | $3\varphi$             | $2\varphi$            | $-\varphi$             | 0                      | $1\varphi$             | $2\varphi$             | $3\varphi$             | $4\varphi$             |

| 2      | $7\varphi$             | $6\varphi$             | $5\varphi$            | $4\varphi$             | $3\varphi$            | $-2\varphi$            | $-\varphi$             | 0                      | $1\varphi$             | $2\varphi$             | $3\varphi$             |

| 3      | $8\varphi$             | $7\varphi$             | 6                     | $5\varphi$             | $4\varphi$            | $-3\varphi$            | $-2\varphi$            | $-\varphi$             | 0                      | $1\varphi$             | $2\varphi$             |

| 4      | $9\overline{\varphi}$  | $8\overline{\varphi}$  | $7\varphi$            | $6\overline{\varphi}$  | $5\overline{\varphi}$ | $-4\overline{\varphi}$ | $-3\overline{\varphi}$ | $-2\overline{\varphi}$ | - <u>φ</u>             | 0                      | $1\overline{\varphi}$  |

| 5      | $10\overline{\varphi}$ | $9\overline{\varphi}$  | $8\overline{\varphi}$ | $7\overline{\varphi}$  | $6\overline{\varphi}$ | $-5\overline{\varphi}$ | $-4\overline{\varphi}$ | $-3\overline{\varphi}$ | $-2\overline{\varphi}$ | $-\varphi$             | 0                      |

Table 2.2: Phase of the  $n^{th}$  harmonic of input signal mixed with  $j^{th}$  harmonic of LO signal just before addition in a polyphase multipath circuit with mixers as second phase shifters

As before, the intermodulation distortion products, can be deleted including them in the previous equation as k + m = n.

# Chapter 3

# Design

# 3.1 Design Overview

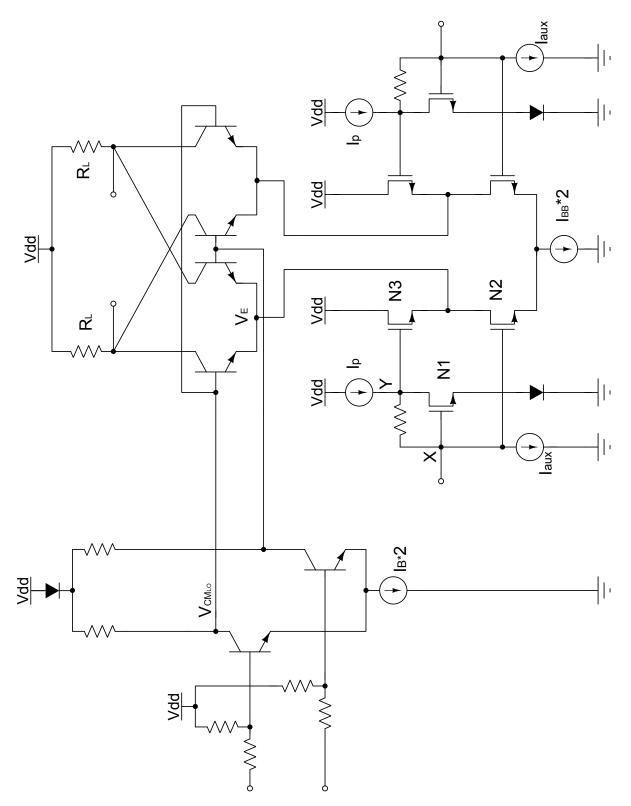

The targets of this project (See table 1.1) are directed to achieve a dynamic range as wide as possible for the upconverting IQ Modulator, hence the noise generated by the system, degrading the sensitivity of the mixing at lower output and input powers, has to be properly limited. The output referred interception point and the relative compression point needs to be increased, allowing an high output power to be produced meanwhile the input and output voltage follow a linear trend defined by the conversion gain.

The degradation of the signal to noise ratio strongly depend on the noise produced by the input port, represented by the transconductor stage of the two mixers implemented. The design of them has to be conveyed toward the lower possible noise generation. Equally the voltage to current conversion employed by the same stage, needs to reduce the production of distortion, which has the straight forward consequence to generate and spread spurs over the output frequency range getting worse the linearity of the transmission. Moreover, the mixer are followed by an output buffer, which has to conserve the linearity of the mixing avoiding additional spurs

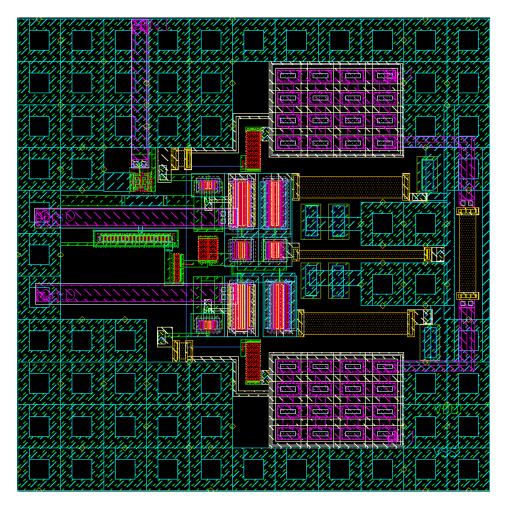

Figure 3.1: The complete IQ Modulator block chain

injection, but not decreasing the third order intercept point referred at the output port.

The active mixer of the upconverter needs to be interfaced with DACs, delivering a quadrature baseband signal in the current domain, a 50 $\Omega$  input impedance provided by the transconductor can avoid to add an extra DAC interface to match the two blocks.

At the output port a differential  $100\Omega$  impedance needs to be provided, allowing measures with the standard radio-frequency laboratory equipment.

The core of the system is the active mixer, defining most of the proprieties aforementioned. Having the opportunity to use a SiGe BiCMOS technology two macrotopology of mixers can be considered:

- Active mixer with bipolar transconductor : The presented mixer, is composed by a bipolar transconductor simpled made by a differential pair.

- Pros:

- \* A bipolar transconductor can achieve an high transconductance.

- \* The thermal noise produced by these devices is smaller than the MOS-

FET counterpart.

- Cons:

- \* A bipolar device offers a linearity directly proportional to the current flowing trhough it. To enhance the linearity of a bipolar differential pair is possible to place degeneration resistors, but decreasing their gain, increasing the noise and spending an higher current to bias it [15].

- Active mixer with CMOS transconductor : Since the frequency translation to assolve is the upconverting, the input signal is located at the baseband frequency range and so even no high speed devices can employ the voltage to current conversion. Due to that a MOSFET transconductor is taken into account

- Pros:

- \* A MOSFET transistor is a device with a greater intrinsic linearity than a bipolar, proportional to the overdrive voltage instead of the biasing current.

- \* A MOSFET differential pair provides an higher IP3 than the bipolar counter part even without degeneration [21].

- **Cons:** MOSFETs are more noisy than bipolar.

In both solutions here shown, the switching cell is composed by two cross coupled differential pair implemented by bipolar technology, indeed the bipolar switching cell fits with the input LO frequency request ensuring , furthermore, a really high port isolation.

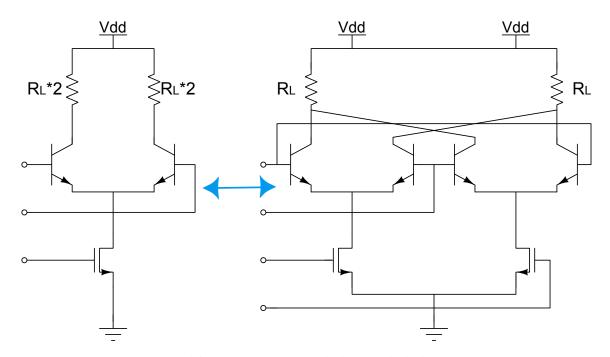

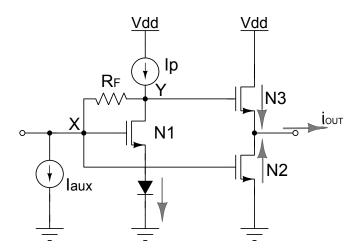

If a technique to reduce the noise figure is implemented the MOSFET transconductor

Figure 3.2: Compared structures

version becomes the most attractive solution, by taking in advantage of their intrinsic linearity proprieties. Due to that the presented design is based on full BiCMOS mixing topology directed to ensure the specified target performances.

## 3.2 The buffers

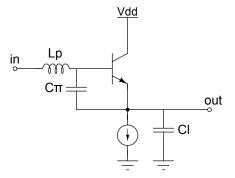

## 3.2.1 The input buffer

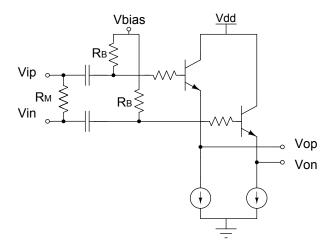

The input buffer, has to interface the local oscillator with the frequency divider. The input port of this stage is AC coupled, placing two coupling capacitors in series to the input termination. Moreover, to avoid any kind of reflection and oscillation to its port, ensuring the maximum power transfer from the input source to the stage, the input matching has to be achieved. The input voltage source provides frequencies in a wideband, so the match needs to be verified for the whole band.

At the input a couple of bias resistor are placed in parallel to the common collector

Figure 3.3: Emitter Follower

amplifiers and biased at the proper voltage  $V_{bias}$ .  $R_M$  is the matching resistor, in fact being in parallel with the input impedance of the common-collector amplifier  $r_{\pi}(1 + g_m R_{out_{mirror}})$  and the biasing resistors  $R_B$ , having both couples an high resistance value, it is the predominant and describe the input impedance. Due to that, the differential port is matched when  $R_M = 100\Omega$ . The couple of series capacitors connected at the input, complete the ac biasing. On the other hand the intrinsic output buffer resistance is given at low frequencies by:

$$R_{OUT} = \frac{1}{g_m}$$

The biasing network is implemented by a couple of current tail mirrors, that offers a stable current and an high output resistance seen from its collector. This impedance is higher, when these current mirrors contain a degeneration resistance which increases the  $r_o$  by a factor equals to the loop gain  $T = (1 + g_m R_E)$ .

The output load of this circuit is the input impedance of the frequency divider. At the frequencies of interest it has a resistive predominant value slightly below  $1k\Omega$ . The input signal applied has a differential 3dB power ( $\simeq 600mV$ ). Due to this values not an high current is needed to bias the stage, and this and it is set to 2mA for each branch.

## 3.2.2 Wideband Input Matching

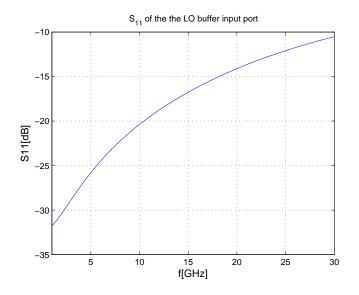

The input matching has to be guaranteed over a range of frequencies up to  $f_{MAX} = 2f_{LO_{MAX}} = 30GHz$ , since the local oscillator driving the frequency divider, works at the double of the RF frequency commuting the active mixer.

This limit is strictly correlate with the parasitic components nested in the couple of emitter followers. At high frequencies the input impedance becomes:

$$Z_{in} = \frac{r_{\pi}}{1 + sr_{\pi}C_{\pi}} (1 + gmR_L) \tag{3.1}$$

$C_{\pi}$  is the principal contributor of the degradation of the input impedance seen at the base of the emitter follower. Indeed, at higher frequency the impedance becomes purely capacitive, and its low value, connected in parallel with input impedance, increases the total reflection at the input port. By limiting the geometry size of the transistor it is possible to get lower parasitic effects due to  $C_{\pi}$ , achieving the required  $S_{11}$  even at high frequencies.

### Stability check

The emitter follower topology, having the output taken from the emitter of the common collector amplifier and the input applied to its base, suffers of a tendency to oscillate. Carefully watching its structure, considering layout parasitic including load capacitors and series inductors, its structure reclaims the widely known topology named Colpitts Oscillator.

The parasitic inductance is negligible when the wire connecting the input to the base of the bipolar amplifier is shorter. The capacitive divider composed by  $C_{\pi}$  and

Figure 3.4: The  $S_{11}$  seen at the input port of the buffer

Figure 3.5: Intrinsic Colpitts oscillator

the sum of the capacitors nested to the output node  $C_L$ , if preceded by an inductor generates an unwanted oscillation.

All these parasitic components, get the input buffer oscillating close to the frequency :

$$f_o = \frac{1}{2\pi\sqrt{L_p \frac{C_\pi C_L}{C_\pi + C_L}}}$$

The unconditional stability is checked up to 200GHz, a wide band range including even  $f_o$ .

The design has to consider and fix this issue, indeed to reduce it, it is possible during the layout, to decrease the input track connecting the local oscillator to the input of this buffer, reducing the parasitic inductor, but this solution is not always available and does not ensure the unconditionally stability robustness.

A more efficient way to the avoid this problem is represented connecting in series at the base of the buffer a resistor, suppressing the Q of the inner tank.

Furthermore, by observing the stability of the circuit even without inductors, oscillations can occur even not including any parasitic tank. An additional analysis can explain how it is possible, concerning the relation between instability and Sparameters. In a two-port by considering the reflection coefficients, seen from the input and the output port and represented by  $S_{11}$  and  $S_{22}$ , if they assume an absolute value greater than one, the injection of a signal in the relative port can cause an unstable behavior of the circuit. This situation is verified when:

$$\frac{Z_S - Z_{IN}}{Z_S + Z_{IN}} > 1$$

If  $Z_S = R_S$  this expression can be verified when the input impedance assumes negative values. Indeed by considering the parasitic capacitance, already objects of discussion, the input resistance seen looking at the base of the common-collector transistor can assume negative value [3].

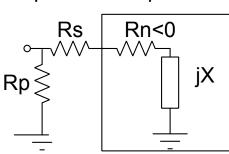

As already seen, this negative resistor can get positive just with an additional resistor

Figure 3.6: Input impedance small signal model

connected in series at the base increasing  $R_b$ .

The trade-off of a supplementary series resistor, is represented in additional losses, but the magnitude of this leakages cause negligible consequences for the overall performances of the system, reminding that the input power of the local oscillator is set at the standard of 3dBm, largely sufficient to drive the frequency divider.

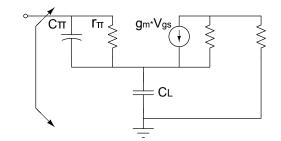

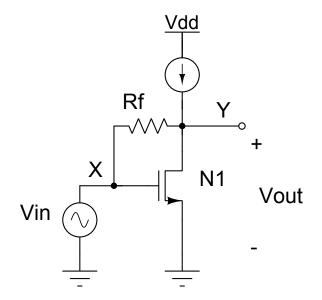

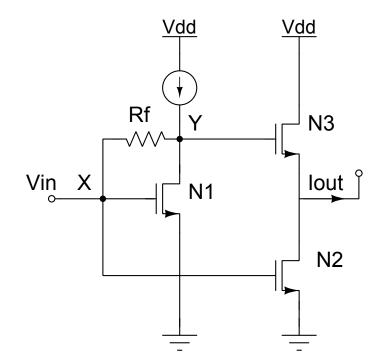

## 3.2.3 The output buffer

The summation of the current signals, produced by the two active mixers has to be delivered to the external environment through a buffer interface. Most likely the output buffer will be connected to a further power amplifier, then connected to a transmitter antenna. So, the output buffer has to deliver the modulated signal providing a matched output impedance of  $50\Omega$ .

On the other hand this circuitry has an important role for the linearity issue. In fact, the OIP3 can be computed as follows:

$$OIP3 = P_{out_{[dBm]}} - IM3_{[dB]} \frac{1}{2} = P_{in_{[dBm]}} + Gain_{[dBm]} - \frac{1}{2}IM3_{[dB]}$$

(3.2)

To set an high OIP3, it is important to guarantee along the system, an adequate gain to the fundamental output harmonics. Moreover, the specification to ensure the output impedance matching causes an unavoidable loss of 3dB. On the other hand, increasing its voltage gain, means to introduce distortion decreasing the linearity of the whole Modulator.

Two solution are here compared:

- An emitter follower topology.

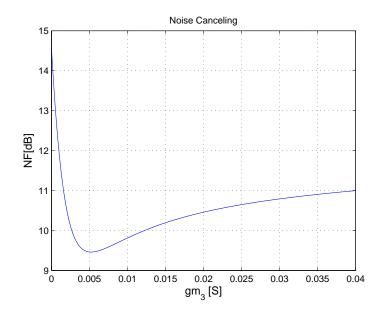

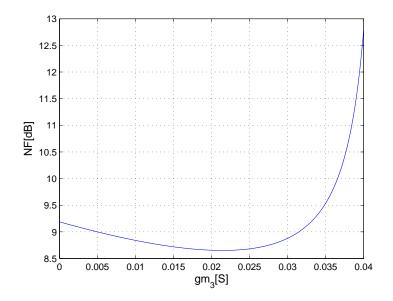

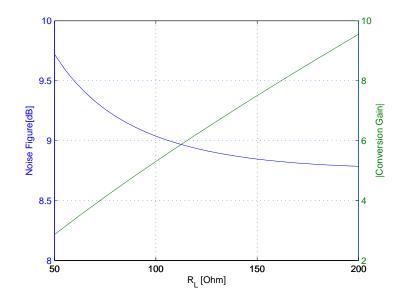

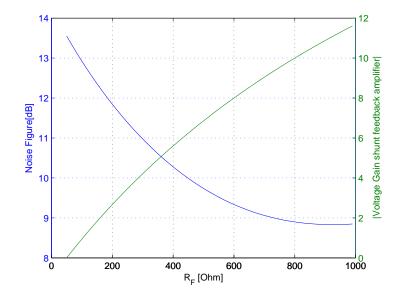

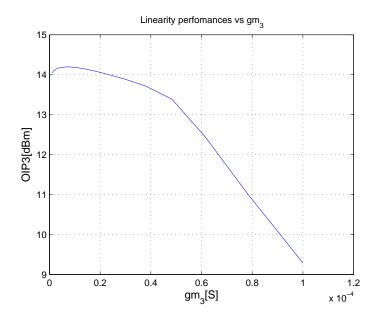

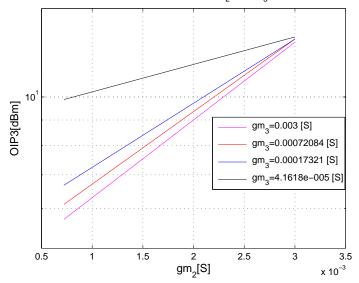

- Pros: