## UNIVERSITA' DEGLI STUDI DI PADOVA

## Dipartimento di Ingegneria Industriale DII

Corso di laurea in Ingegneria dell'Energia Elettrica

# Characterization and optimization of a fast converter to control plasma instabilities in JT-60SA $\,$

Relatore: Prof. Paolo BETTINI Correlatore: Ing. Alberto FERRO

Ferdinando Gasparini

Matricola 1090346

Anno Accademico 2015/2016

ii

## Contents

| Abstract         1 JT-60SA         1.1 Introduction         1.2 JT-60SA main parameters         1.3 Magnet systems         1.4 Heating systems         1.5 Electric systems         1.6 Supervisory control system and data acquisition system         1.7 Research phases         2 The Resistive Wall Mode control in JT-60SA         2.1 Introduction         2.2 Control of RWM         2.3 Coils design and characterization | vii             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 1.1       Introduction          1.2       JT-60SA main parameters          1.3       Magnet systems          1.4       Heating systems          1.5       Electric systems          1.6       Supervisory control system and data acquisition system          1.7       Research phases          2       The Resistive Wall Mode control in JT-60SA         2.1       Introduction          2.2       Control of RWM              | ix              |

| 1.2       JT-60SA main parameters                                                                                                                                                                                                                                                                                                                                                                                                 | 1               |

| 1.3 Magnet systems                                                                                                                                                                                                                                                                                                                                                                                                                | 1               |

| 1.4       Heating systems                                                                                                                                                                                                                                                                                                                                                                                                         | 2               |

| <ul> <li>1.5 Electric systems</li></ul>                                                                                                                                                                                                                                                                                                                                                                                           | 2               |

| 1.6       Supervisory control system and data acquisition system                                                                                                                                                                                                                                                                                                                                                                  | 4               |

| 1.7 Research phases                                                                                                                                                                                                                                                                                                                                                                                                               | 6               |

| 2 The Resistive Wall Mode control in JT-60SA<br>2.1 Introduction                                                                                                                                                                                                                                                                                                                                                                  | 8               |

| 2.1       Introduction                                                                                                                                                                                                                                                                                                                                                                                                            | 9               |

| 2.2 Control of RWM                                                                                                                                                                                                                                                                                                                                                                                                                | 11              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11              |

| 2.3 Coils design and characterization                                                                                                                                                                                                                                                                                                                                                                                             | 12              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12              |

| 2.4 Cables                                                                                                                                                                                                                                                                                                                                                                                                                        | 12              |

| 2.5 PS and control main requirements                                                                                                                                                                                                                                                                                                                                                                                              | 14              |

| 2.6 Plasma induced back-EMF                                                                                                                                                                                                                                                                                                                                                                                                       | 14              |

| 3 RWM power supply                                                                                                                                                                                                                                                                                                                                                                                                                | 17              |

| 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                  | 17              |

| 3.2 AC/DC front-end                                                                                                                                                                                                                                                                                                                                                                                                               | 17              |

| 3.3 DC-link nominal voltage                                                                                                                                                                                                                                                                                                                                                                                                       | 18              |

| 3.4 DC-link capacitor bank                                                                                                                                                                                                                                                                                                                                                                                                        | 18              |

| 3.5 Fast converter                                                                                                                                                                                                                                                                                                                                                                                                                | 19              |

| 4 The dummy load                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>21</b>       |

| 4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                  | 21              |

| 4.2 Dummy load characterization                                                                                                                                                                                                                                                                                                                                                                                                   | 21              |

| 5 The fast converter                                                                                                                                                                                                                                                                                                                                                                                                              | 23              |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                  | 23              |

| 5.2 Power semiconductors                                                                                                                                                                                                                                                                                                                                                                                                          | $\frac{23}{23}$ |

| 5.3 Input capacitor bank                                                                                                                                                                                                                                                                                                                                                                                                          | $\frac{23}{24}$ |

| 5.4 Output filter                                                                                                                                                                                                                                                                                                                                                                                                                 | $\frac{24}{24}$ |

| 5.5 Control board                                                                                                                                                                                                                                                                                                                                                                                                                 | 24<br>26        |

| 5.6 Voltage slope limits                                                                                                                                                                                                                                                                                                                                                                                                          | $\frac{20}{27}$ |

| 5.7 Thermal limits                                                                                                                                                                                                                                                                                                                                                                                                                | $\frac{21}{27}$ |

| 6  |              | e converter model                                | 29         |

|----|--------------|--------------------------------------------------|------------|

|    | 6.1          | Introduction                                     | 29         |

|    | 6.2          | The Simulink $(\mathbb{R})$ fast converter model | 29         |

|    | 6.3          | The Simulink® control model                      | 29         |

|    | 6.4          | The load model based on Cauer cells              | 32         |

|    | 6.5          | The load model based on convolution              | 32         |

|    | 6.6          | The Simulink® implementation of the load model   | 33         |

|    | 6.7          | The load characterization                        | 34         |

|    | 6.8          | Precision of the convolution-based model         | 35         |

|    | 6.9          | Cauer cell vs convolution model comparison       | 36         |

|    | 6.10         | The discrete shift register                      | 37         |

| 7  | DT           | compensation                                     | 39         |

|    | 7.1          | Introduction                                     | 39         |

|    | 7.2          | DT compensation method                           | 39         |

|    | 7.3          | MatLab Simulink (R) implementation.              | 40         |

|    | 7.4          | MatLab Simulink (R) results                      | 42         |

| Q  | DI a         | antimization                                     | 43         |

| 8  |              | optimization                                     | <b>43</b>  |

|    | 8.1          | Introduction.                                    |            |

|    | $8.2 \\ 8.3$ | Particle Swarm Optimization                      | 43         |

|    | 8.4          | Results                                          | $44 \\ 45$ |

|    | 0.4          | Results                                          | 40         |

| 9  | Con          | troller modifications                            | <b>49</b>  |

|    | 9.1          | Controller modification                          | 49         |

|    | 9.2          | Delayed integral branch                          | 49         |

|    | 9.3          | C code implementation                            | 50         |

| 10 | One          | en loop current control                          | 53         |

| 10 | -            |                                                  | 53         |

|    |              | The deconvolution algorithm                      | 53         |

|    |              | Results with ideal converter                     | 54         |

|    |              | Conclusion                                       | 59         |

|    |              |                                                  |            |

| 11 | -            | perimental setup                                 | 61         |

|    |              | Introduction                                     | 61         |

|    |              | Power supply                                     | 61         |

|    |              | Capacitor discharge circuit                      | 61         |

|    | 11.4         | Grounding                                        | 64         |

| 12 | Moo          | del validation with experiments                  | 65         |

| _  |              | Introduction                                     | 65         |

12.2 Voltage step response .....

12.3 Frequency characterization

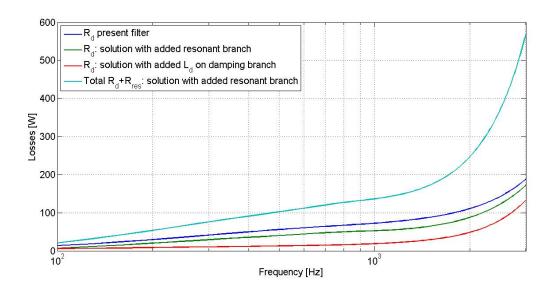

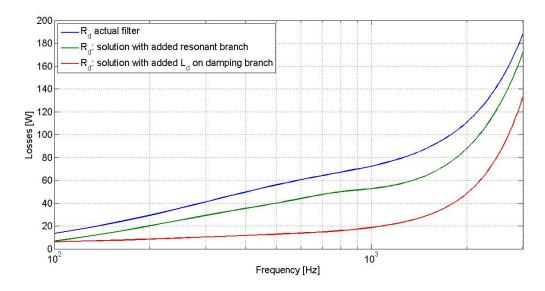

13.4 RLC damping branch

13.5 RLC resonant branch

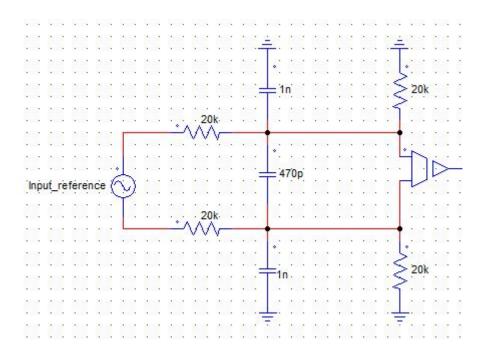

13.6 Filter on analog reference

**13** Filter optimizations

| 1 | v |

|---|---|

| <b>14</b>    |      |                                     | 79 |

|--------------|------|-------------------------------------|----|

|              | 14.1 | Introduction                        | 79 |

|              | 14.2 | Model results with snubber          | 79 |

|              | 14.3 | Causes                              | 31 |

|              | 14.4 | Dynamics of the phenomena           | 81 |

|              | 14.5 | Possible solution                   | 34 |

|              | 14.6 | The supervisor controller           | 34 |

| 15           | And  | omalous voltage oscillations        | 87 |

|              | 15.1 | Introduction                        | 87 |

|              |      | Initial measurements                |    |

|              |      |                                     | 89 |

|              |      | Parasitic turn-on phenomena         | 90 |

| 16           | Con  | nclusions                           | 93 |

|              | 16.1 | Main results                        | 93 |

|              |      | Future developments                 |    |

| $\mathbf{A}$ | Mat  | $tlab(\mathbf{\hat{R}}) codes$      | 95 |

|              |      | Code to find the impulsive response | 95 |

|              |      | PSO-MO Matlab® code                 |    |

## Riassunto

L'obiettivo finale di questo lavoro di tesi è di studiare il comportamento di un convertitore veloce, progettato per alimentare gli avvolgimenti per il controllo dei cosiddetti Resistive Wall Modes (RWM) in JT-60SA. La macchina oggetto degli studi è stata progettata dall'azienda Equipaggiamenti Elettronici Industriali EEI s.p.a. e un suo prototipo è già stato prodotto e testato. Durante suddetti tests sono emerse varie problematiche che l'Autore ha analizzato e risolto durante il lavoro di tesi. Quindi, durante il lavoro, l'Autore ha ottenuto un buon livello di esperienza sul campo ed ha avuto la possibilità di sviluppare alcune idee e soluzioni originali, grazie anche alla solida preparazione teorica ottenuta durante gli studi universitari.

JT-60SA è una macchina per fusione nucleare dotata di magneti superconduttori, sviluppata grazie ad una collaborazione tra Europa e Giappone, che inizierà ad operare all'inizio del 2019. Uno dei sui scopi principali è studiare la stabilizzazione attiva degli RWM. Essi sono instabilità magneto-idrodinamiche che tendono a distorcere velocemente la colonna di plasma. Tuttavia, esse possono essere rallentate, grazie a delle pareti conduttive stabilizzanti, e, quindi, controllate attivamente. Una delle possibilità di controllo è proprio quella di utilizzare delle bobine in rame stabilizzatrici: ne saranno, infatti, posti 18, 6 nella direzione toroidale per 3 in quella poloidale. Per produrre i campi necessari alla stabilizzazione sono richiesti 300 A e 240 V di picco.

Per ottenere la massima flessibilità nel controllo degli RWM, ogni avvolgimento avrà un proprio convertitore indipendente. Sono, quindi, previsti 18 convertitori monofase a quattro quadranti e ponte intero da 72 kVA ciascuno. Inoltre, essi dovranno avere una dinamica molto veloce, infatti le specifiche prevedono 50  $\mu$ s di massima latenza e 3 kHz di banda passante. Di conseguenza sono richieste alte frequenze di commutazione con modulazione unipolare, raggiungibili, nella configurazione a ponte ad H, solo grazie alle moderne tecnologie di IGBT ibridi in Carburo di Silicio (SiC), dove solo il diodo in antiparallelo è effettivamente prodotto in SiC. Grazie a ciò le perdite di commutazione vengono fortemente ridotte e si possono raggiungere 30 kHz di frequenza di commutazione, che diventano 60 kHz equivalenti sul carico. Infine, ogni convertitore sarà dotato di una scheda di controllo molto veloce, basata su DSP e FPGA. A causa della bassa impedenza di carico e delle alte frequenze di commutazione, è stato, infine, necessario introdurre un filtro in uscita di tipo LC, abbinato ad un ramo trasversale RC smorzatore.

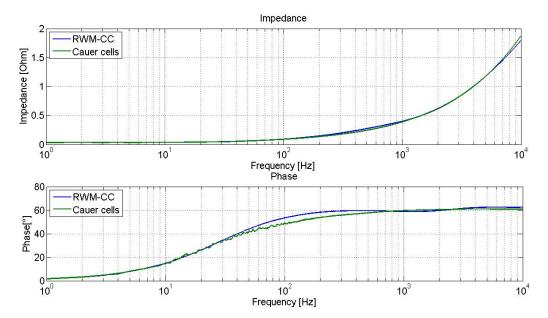

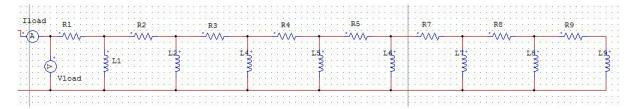

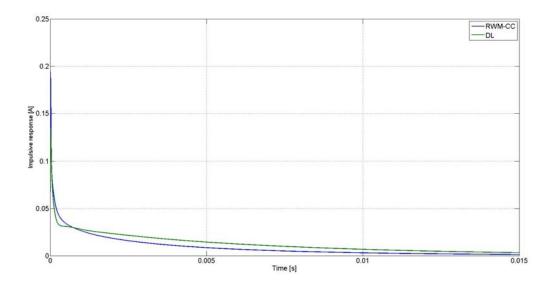

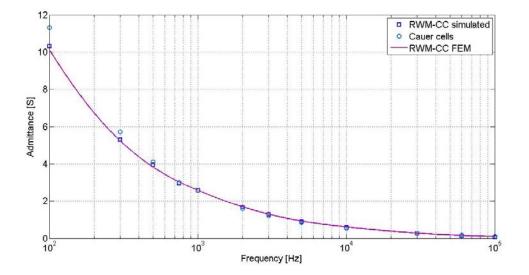

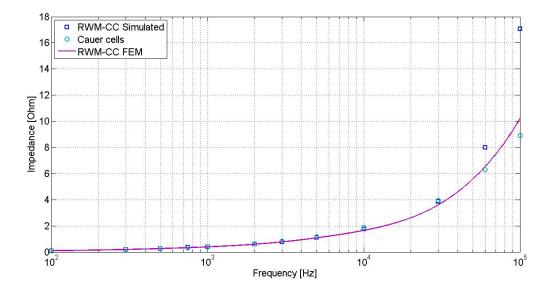

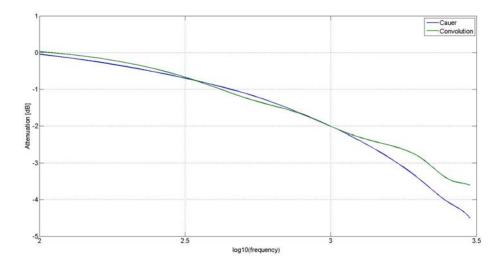

Poiché il carico ha resistenza ed induttanza variabile con la frequenza, a causa di effetti pelle, di prossimità e schermatura, è stato necessario procedere con un'ottimizzazione del controllore PI dell'anello di corrente tramite l'uso di un modello numerico del carico. Due modelli, quindi, sono stati sviluppati: il primo, sviluppato dalla EEI, è basato sulle celle Cauer, ossia reti di dipoli RL, che ricreano con precisione l'impedenza del carico fino a frequenze superiori ai 3 kHz; il secondo, basato su un'idea dell'ing. Ferro, prevede la convoluzione tra la forzante (la tensione imposta sul carico) e la risposta impulsiva del carico (l'anti-trasformata di Fourier dell'ammettenza). Quest'ultimo modello, come mostrato dall'Autore, funziona poiché, per ogni sistema lineare tempo-invariante (LTI), una sua evoluzione particolare può essere trovata facendo la convoluzione nel tempo tra la forzante e la risposta impulsiva del sistema stesso.

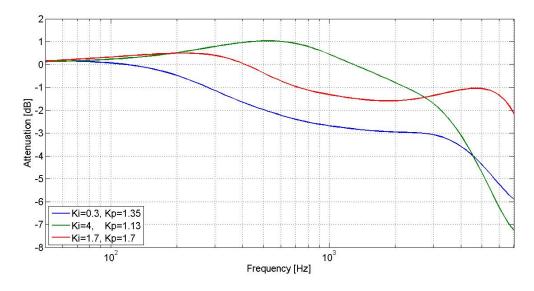

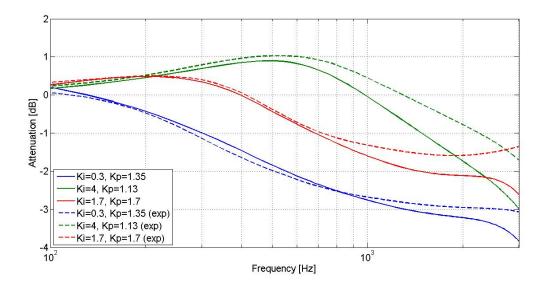

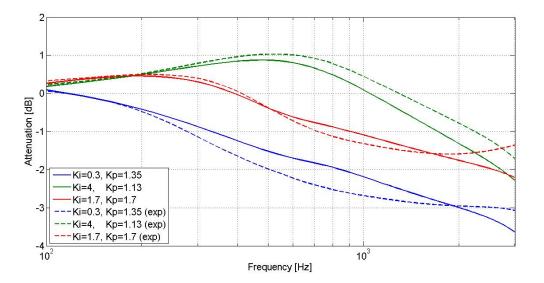

Quindi, l'Autore, utilizzando come base un codice pre-esistente, ha sviluppato un codice di ottimizzazione stocastico multi-obiettivo basato sulla teoria della Particle Swarm Optimization (PSO) ed il Fronte di Pareto. Utilizzando il modello a convoluzione, la procedura di ottimizzazione ha messo in evidenza alcuni limiti del controllore PI usato. Dunque, l'Autore ha sviluppato due possibili soluzioni originali che consentono di migliorare le prestazioni dinamiche: la prima e più promettente prevede l'aggiunta di un ulteriore ramo integrale al controllore PI, che include un certo ritardo regolabile rispetto al PI originale; la seconda è, invece, una soluzione "predittiva" basata sul modello a convoluzione, che utilizza, in realtà, la deconvoluzione. Essa cerca di ricavare la tensione necessaria a rispettare il riferimento di corrente sul carico deconvolvendo la risposta impulsiva e la tensione stessa (calcolata nei passi precedenti).

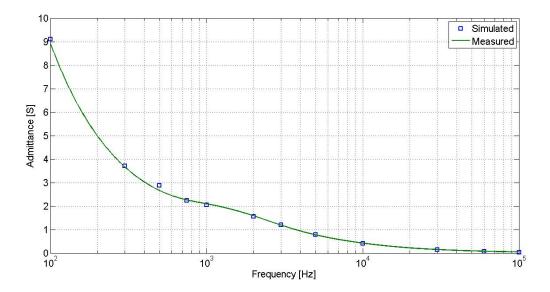

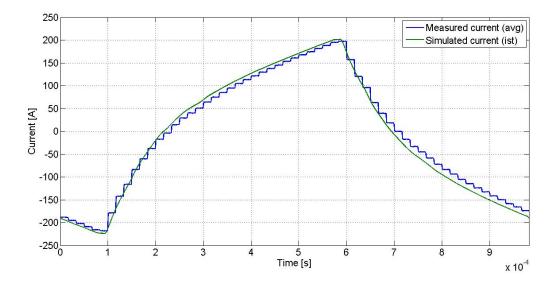

Dopodiché è stata fatta la validazione del modello a convoluzione tramite i primi test sperimentali. Due tipi di prove sono state eseguite: nella prima è stata misurata la risposta di corrente sul carico ad un gradino di tensione. Lo stesso test, con proprio lo stesso input di tensione, è stato poi replicato nel modello, ottenendo una quasi perfetta sovrapposizione dei risultati. Nella seconda prova, invece, è stata fatta una caratterizzazione in frequenza del controllo di corrente e i risultati ottenuti hanno evidenziato una buona sovrapposizione con il modello per frequenze fino ad oltre 1 kHz.

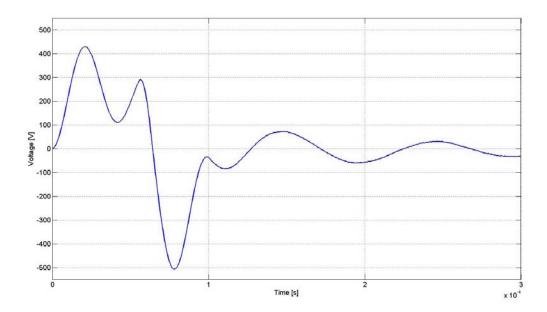

Fatto ciò, si è passati all'analisi degli overshoot di tensione dovuti alla dinamica del filtro d'uscita, i quali possono raggiungere picchi di 550 V. Una volta replicato il fenomeno sul prototipo, l'Autore ha eseguito degli studi per modifiche del filtro che permettessero di ridurre il picco di tensione, sviluppando una soluzione originale al problema, basata su un ramo risonante posto al posto del ramo RC smorzatore. Questa nuova topologia, inoltre ha permesso una buona riduzione delle derivate di tensione sul carico.

Inoltre è stata approntata un'approfondita analisi del sistema di correzione dei tempi morti (Dead Times, DT). Ciò ha portato allo sviluppo da parte dell'Autore di un modello che è riuscito a ricreare con sufficiente precisione delle anomale oscillazioni di corrente, le quali erano state effettivamente misurate durante i tests. Grazie a questo lavoro, l'Autore è riuscito ad identificare dettagliatamente la dinamica e la causa delle suddette oscillazioni ed, inoltre, ha elaborato delle possibili soluzioni al problema.

L'ultima parte del lavoro è consistita nella caratterizzazione di alcune anomale oscillazioni di tensione, osservate soprattutto ad alte correnti (300 A) e basse frequenze (100 Hz). Dopo vari test sperimentali, è risultato che queste oscillazioni sono dovuti a brevi, ma comunque dannosi, cortocircuiti in una gamba del ponte ad H. L'Autore, analizzando i dati ottenuti, ha quindi cercato di chiarirne le cause, escludendo eventuali effetti parassiti.

## Abstract

The final and primary aim of this work is to study the behavior of a fast mono-phase converter, designed to feed the Resistive Wall Modes Control Coils (RWM-CC) in JT-60SA, and, eventually, to find possible solutions to the main issues that came out during initial testing of its prototype. The main points to be investigated were: the optimization of the frequency response of the current closed loop control, current oscillations due to a voltage errors compensation algorithm, high voltage overshoots and derivatives on the load due to the output filter behavior and, lastly, some anomalous voltage oscillations. With this aim, a deep analysis of a the system has been pursued with the help of advanced numerical models and tools. Then, the obtained model results were tested experimentally on the real prototype. Thank to this procedure, the Author slightly improved the frequency response with a controller modification, based on a original idea. Then, he understood the causes of the current and voltage oscillations problems. Lastly, the Author found a possible solution to improve the filter behavior. Therefore, during this work, the Author gained a certain level of experience on complex system analysis and debugging. Then, he managed, thanks to his theoretical framework obtained during his University studies, to develop some valid and original solutions to such problems, as will be further explained in the subsequent paragraphs.

## JT-60SA

## 1.1 Introduction

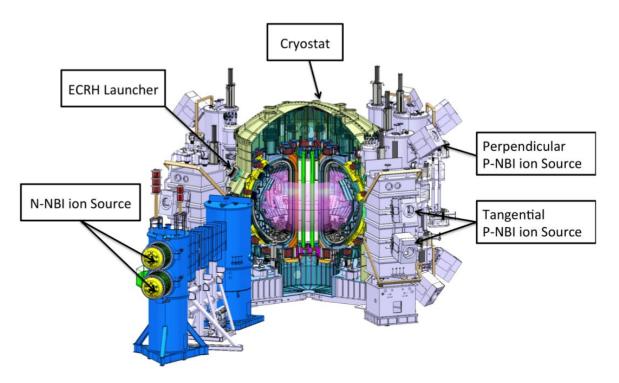

JT-60SA, (Fig. 1.1<sup>1</sup>), is a new superconducting tokamak that is being built in Naka, Japan and it will start to operate in 2019. It is a combined project of the JA-EU Satellite Tokamak Programme, that will support the exploitation of ITER and research towards DEMO [1, 2].

Figure 1.1: An overview of the tokamak JT-60SA.

Its main aim is to study:

- 1. Operation regimes;

- 2. MHD stability and control;

- 3. Transport and confinement;

- 4. High energy particle behavior;

<sup>&</sup>lt;sup>1</sup>All the figures in this chapter are taken from [1]

- 5. Pedestal and edge physics;

- 6. Divertor and plasma-wall interaction;

- 7. Fusion engineering;

- 8. Theoretical model and simulation codes validation.

One of the most important goal is to contribute to a practically acceptable DEMO plasma design. In-fact one of the most important feature of JT60-SA will be its steady-state regime performance and its real time control capability.

#### 1.2 JT-60SA main parameters

JT-60SA is expected to produce a break-even equivalent class high temperature deuterium plasma and to maintain it for a typical time of 100s. The plasma will have a maximum current  $I_p = 5.5$  MA with high density of the order of  $10^{20}$  m<sup>-3</sup>.

To achieve these results, the machine will have a plasma volume of  $120-130 \text{ m}^3$  contained in a torus with a major radius of 2.95 m and a minor one of 1.15 m circa. The plasma will be confined by a toroidal magnetic field of about 2.2-2.3 T.

The plasma will be heated by both positive (24 MW) and negative (10 MW) neutral beam injectors (NBI) and by electron cyclotron resonance heating (ECRH, 110 GHz and 138 GHz, 7 MW total), producing up to 41 MW of total input power.

Another important component of the tokamak is the divertor. The JT60-SA divertor has to handle up to 15  $MW/m^2$  for the entire plasma pulse length.

The active feedback control system will include:

- two independently controllable coils for position control: Fast Plasma Position Control Coils (FP-PCC);

- 18 Resistive Wall Mode Control Coils (RWM-CC);

- 18 Error Field Control Coils (EFCC);

- high power heating, current-drive and momentum-input systems.

All these systems are coupled with 26 plasma diagnostics with high spacial and time resolution, needed not only by the control system, but also for conducting all the physics research.

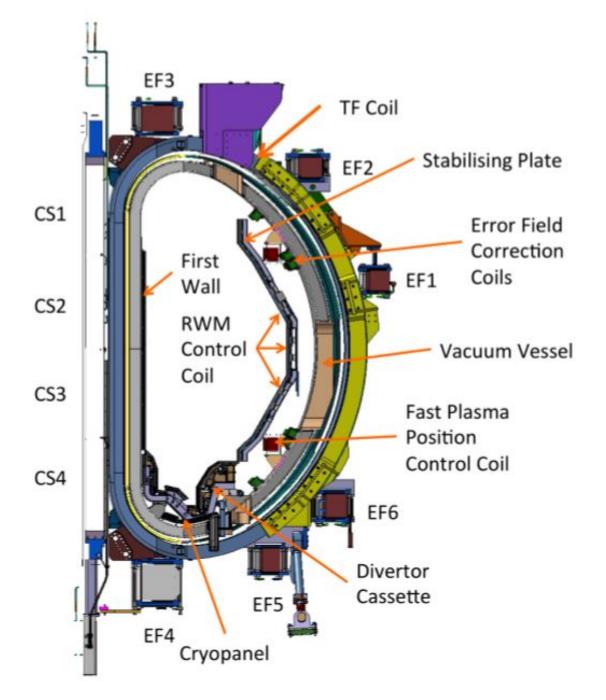

#### **1.3** Magnet systems

**Toroidal Field coils.** These are 18 NbTi superconducting coils cooled by supercritical Helium at 4.4 K.They will produce a 5.65 T B-field at the conductor surface, while absorbing 25.7 kA.

Central Solenoid System (CS). It uses a Nb<sub>3</sub>Sn superconductor, always cooled at 4.4 K by supercritical Helium. They will sustain a maximum coil current of 11 MAturns while having an operating current of 20 kA and a nominal peak B-field of 8.9 T. The CS system will be composed by 4 modules with a total number of turns of 549.

**Equilibrium Field coils (EF).** Located, as shown in Fig. 1.2, just outside the TF coils, they will be composed of NbTi superconductors and they will be rated for 20 kA nominal current. They will produce peak B-field between 4.8 and 6.2 T, depending on their position. In total there will be 6 EF coils.

Fast Plasma Position Control coils (FPPCC). This system is composed by two copper coil sets that provide independent control of vertical and horizontal fields. They will sustain 80 kAturns for each set, but the number of turns has not yet been specified.

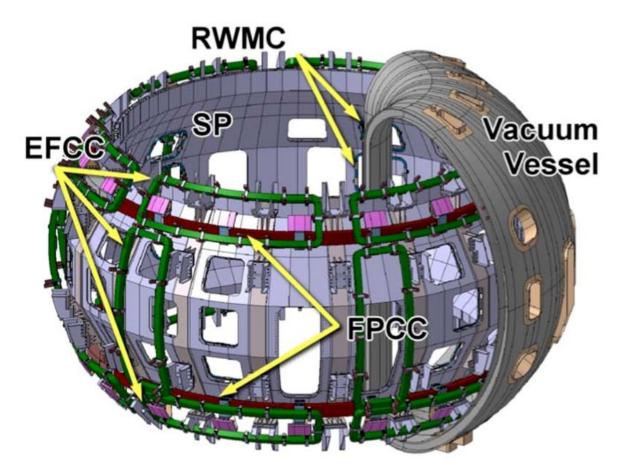

Error Field Correction coils (EFCC). There will be 18 coils: 6 will form the upper coil set, 6

Figure 1.2: The JT-60SA magnet system.

the lower set and the last 6 the middle set. Each coil will be rated for 30 kAturns, with 35 turns per coil.

**RWM Control coils (RWM-CC).** These are 18 coils divided in 6 groups, distributed symmetrically along the toroidal direction, each group being composed of 3 coils along the poloidal one. Each coil will have 8 turns, leading to a 2.2 kAturns current. FPPCC, EFCC and RWM-CC are positioned as shown in Fig. 1.2 and 1.3.

Figure 1.3: Layout of JT-60SA EFCC, RWM-CC, FPPCC and stabilizing plate.

## 1.4 Heating systems

JT-60SA will have both ECRH and NBI plasma heating systems, with a total peak requested power from the power supplies (PS) of 128 MW.

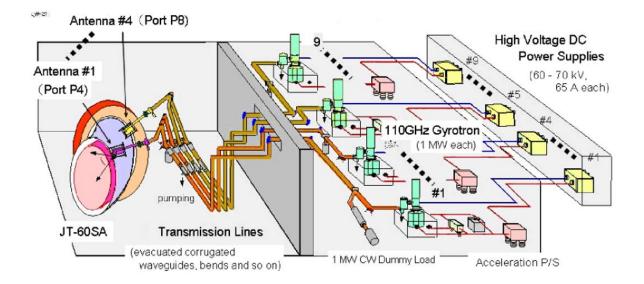

**ECRH system.** This system, pictured in Fig. 1.4, is mainly composed by: high voltage PS, high power gyrotron sets, transmission lines and launcher (antenna) systems. In the initial research phase there will be two sets that will inject 3 MW of heating power for less than 5 s in order to help the plasma start-up, then there will be other two sets that will inject 1.5 MW for all the plasma pulse duration (100 s). During the subsequent integrated research phase, other 5 sets will be added, taking the final input power up to 7 MW. All the sets will work at 110 GHz gyrotron frequency, but also a dual frequency gyrotron at 138 GHz is under intensive R&D.

**NBI system.** During the extended research phase, the injected power will be 34 MW for 100 s. Before it will be 20 MW and 30 MW for the integrated research phase I and II. There will be 12 positive-ion-based NBI (P-NBI) at 2 MW each and one negative-ion-based NBI (N-NBI) rated at 10 MW. All the NBI

Figure 1.4: A schematic view of th ECRF heating systems.

systems will be an upgraded version of the ones used by JT-60U, where the main upgrade will be made on the PS systems and, only on the N-NBI, on the voltage handling capability.

#### **1.5** Electric systems

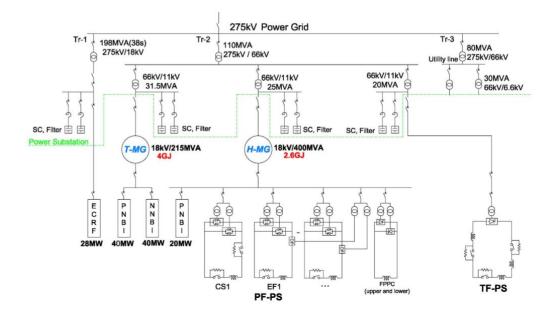

**Pulsed power electrical network.** The pulsed loads, as displayed in Fig. 1.5, will be fed by the 275kV commercial power grid. The voltage will be lowered by step-down transformer. The ECRH heating system will be directly fed by a 275/18 kV transformer, while the other system (NBI,PF and TF coils) will have a first step-down to 66 kV and then three different transformers will bring the voltage to 11 kV. In addition, two motor generator will be connected to the 11 kV stage: the T-MG will be a 215 MVA synchronous machine that will provide the requested active and reactive power to one of the P-NBI and to the N-NBI, while the H-MG will be a 400 MVA synchronous machine, driven also by an induction machine, and it will feed the last P-NBI, all the PF coils and the fast plasma position control coils (FPPCC).

Figure 1.5: The JT-60SA pulsed power electrical network.

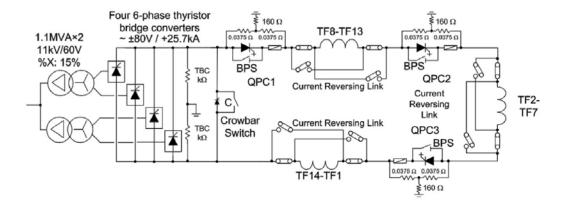

**TF** coils power supply. These coils will be fed by a water cooled two quadrants AC/DC thyristor converter, that will fed the 25.7 kA DC current continuously. The converter AC stage will be connected to a dedicated 11 kV line. Finally, the converter will be able to charge and discharge the full magnet current in about 25 minutes, operations that will be made only once a day. The TF PS circuit is shown in Fig. 1.6.

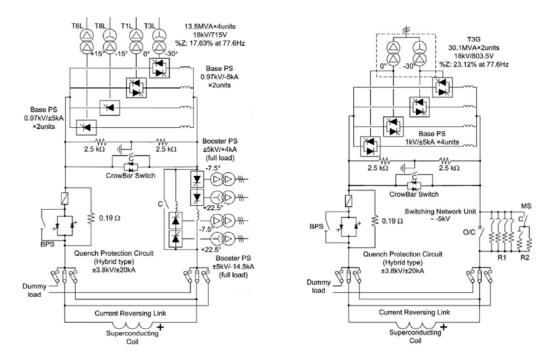

**PF** coils power supplies. There will be three series-connected basic components for each PF system: a "Base power supply (PS)", a "Booster PS" or a Switching Network Unit (SNU) and a quench protection circuit (QPC). Each CS module will have a separate PS that will feed the module with the requested 20 kA. The EF coils will also feature separate PS for each coil, also because EF1, EF2, EF5 and EF6 will have asymmetric current ratings (-20 kA to 10 kA), due to expected operational space. The SNU will be used to induce high plasma voltage to obtain its break-down. It will consist of a DC current interrupter and a tunable resistor added into each CS PS and EF3 and EF4 PS. The PF and EF circuits are displayed in Fig. 1.7.

Quench protection circuit (QPC). In case of superconducting coil quench or a failure inside the PS, a system the can extract rapidly all the magnet stored energy is required in order to protect the coils and shut-down the plasma operation. The QPC is composed by a DC current interrupter, a current dump resistor and a pyro-breaker. In particular, the DC interrupter is composed by both a mechanical switch and a static one: the first conduct the continuous current, while the other is needed for circuit interruption.

FPPC coils power supply. These copper coils will have the function of control vertical and hori-

Figure 1.6: The JT-60SA TF power supply circuit.

Figure 1.7: The JT-60SA EF (left) and CS (right) power supply.

zontal position of the plasma against small perturbation. The PS will consist of a 4 quadrant thyristor converter for each coil with small delay time .

**RWM control coils power supply (RWM-PS).** It consist of 18 independents voltage source converters, rated for  $\pm 300$  A and  $\pm 240$  V with low latency and fast current dynamics.

**Error Field correction coils power supply.** It has been proposed to use multi-phase PWM inverters, but the case is currently under study.

## **1.6** Supervisory control system and data acquisition system

The Supervisory control system and data acquisition system (SCSDAS) has the following roles:

- 1. plant monitoring and machine state management;

- 2. discharge sequence management;

- 3. real-time plasma control;

- 4. device protection and human safety;

- 5. discharge result data management;

- 6. remote experimentation.

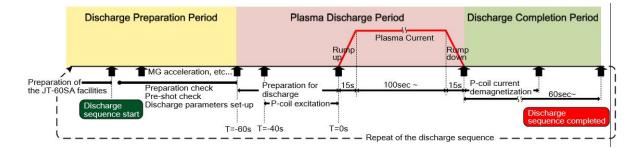

The discharge sequence can be divided, as in Fig. 1.8, in three main time steps:

- 1. discharge preparation period;

- 2. plasma discharge period;

- 3. discharge completion period;

Figure 1.8: The main time steps of the discharge sequence.

During the first phase SCSDAS collects, and in case edits all the discharge condition data and feeds the compiled results to each sub-system. Then it performs a sub-systems condition check.

After all, SCSDAS starts the discharge period: firstly it controls the magnetization of all the PF coils (the TF ones are magnetized only once a day) and it will take up to 60 s, then there will be the plasma current rump-up (15 s), followed by the steady-state operation (up to 100 s), at the end of this there will be the plasma current rump down period (about 15 s).

Then the last phase begins the discharge completion period. During this step SCSDAS commands the PF coils demagnetization and saves all the experimental data.

In addition, during the plasma discharge period the real-time control system takes a primary role. It makes the reconstruction of the plasma shape from magnetic sensor data, calculates the coil currents/voltages necessary to keep the plasma in the reference shapes, generates the control commands for all the actuators. Critical to the operation of the real-time control is the data exchange between all the subsystems: this will be managed by a reflective memory network, that will distribute all the commands, actuator status, measured and processed data.

The real-time control system will have a main control cycle duration of about 10 ms.

#### **1.7** Research phases

Three main research phases are foreseen for JT-60SA:

- 1. initial research;

- 2. integrated research;

- 3. extended research.

**Initial research phase.** Firstly only hydrogen plasmas will be produced, as needed to prepare deuterium operations and for the integrated commissioning of the machine. Then there will be the deuterium phase, in which neutron production, nuclear heating and radiation safety will be commissioned. This will lead to the characterization of operational boundaries and experimental flexibilities, by producing only relatively short pulse discharges. The injected heating power will be 10 MW from N-NBI, 20 MW from P-NBI and max 3 MW from ECRF at 110-138 GHz.

**Integrated research phase.** In this phase long plasma pulses of up to 100s will be finally produced. Due to the higher neutron production (up to  $10^{21}$  neutrons/year), the remote handling system must have completed its commissioning before this phase. The total NB injected power will be 20 MW for 100 s or 30 MW for 60 s, while the ECRF injected power will be increased to 7 MW for 100 s. Also, the divertor will work at its nominal full load of 15 MW/m<sup>2</sup>.

**Extended research phase.** In this phase the heating power will be increased to 41 MW, but this is currently under investigation. Also, the divertor will be upgraded to a metallic one with an advanced shape, based on the progress of tokamak research worldwide.

So, JT-60SA will, hopefully, produce its first plasma in the first half of 2019. Then, as shown in Fig.1.9, every single research phase will last about 2 to 3 years, so that the integrated research phase will end somewhere between 2027 and 2030.

It is to be noted how JT-60SA will start its operations well before ITER, which will produce its first hydrogen plasma maybe in 2025 (the ITER schedule is presently under review). In addition, the ITER Q=10 long pulse D-T operation will not start before 2035, because it requires sufficient exploration of the key physics issues and operational techniques in satellite devices, such as JT-60SA.

| JT-60SA (I)      | 2019 | 2020 | 2021 | 2022 | 2023 | 2024 | 2025 | 2026 | 2027 | 2028 | 2029 | 2030 | 2031 | 2032 | 2033 | 2034 | 2035 |

|------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

|                  | 2010 | 2020 | 2021 | LULL | 2023 | 2024 | 2023 | 2020 | LULI | 2020 | 2020 | 2030 | 2031 | LUJL | 2000 | 2034 | 2000 |

| CASEI            |      |      |      |      |      |      |      |      | -    |      |      |      |      |      |      |      |      |

| Initial - I (H)  | _    |      | -    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Initial - II (D) |      |      |      |      | -    |      |      |      |      |      |      |      |      |      |      |      |      |

| Integrated-I     |      |      |      |      |      | _    | -    |      |      |      |      |      |      |      |      |      |      |

| Integrated-II    |      |      |      |      |      |      |      |      | _    |      |      |      |      |      |      |      |      |

| Extended         |      |      |      |      |      |      |      |      | _    |      |      |      | -    | _    |      |      |      |

|                  |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| JT-60SA (II)     | 2019 | 2020 | 2021 | 2022 | 2023 | 2024 | 2025 | 2026 | 2027 | 2028 | 2029 | 2030 | 2031 | 2032 | 2033 | 2034 | 2035 |

| CASE II          |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Initial - I (H)  |      |      | -    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Initial - II (D) |      |      | _    |      |      | -    |      |      |      |      |      |      |      |      |      |      |      |

| Integrated-I     |      |      |      |      |      |      |      |      | -    |      |      |      |      |      |      |      |      |

| Integrated-II    |      |      |      |      |      |      |      |      |      |      |      | _    |      |      |      |      |      |

| Extended         |      |      |      |      |      |      |      |      |      |      |      | _    |      |      |      |      |      |

Figure 1.9: The two possible time schedules for JT-60SA exploitation.

## The Resistive Wall Mode control in JT-60SA

## 2.1 Introduction

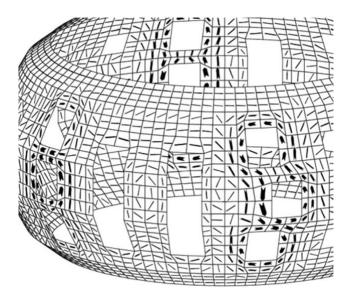

Resistive Wall Modes (RWM) are magneto-hydro-dynamic (MHD) instabilities that arise from the interaction between plasma and the mechanical boundaries, i.e. the first wall. Because these structures are usually made with conductive materials, plasma current or B-field variations could induce asymmetrical eddy currents inside them, with a pattern similar to the one shown in Fig. 2.1. As is it well known, each induced current in turn will create a counter-induced magnetic field that will oppose the variation in the inducing field. This effect, then, will highly reduce the growing rate of external kink modes, i.e. the expansion of the external magnetic field towards the confinement wall. Being these structures resistive, this expansion is not stopped, but only slowed down, making RWM an unstable mode.

Figure 2.1: Eddy-current pattern on the stabilizing plate of JT-60SA [3].

RWMs occur especially at high-pressure  $(\beta_N)$  plasmas. Therefore RWMs set, also, a limit on the achievable  $\beta_N$  in tokamak advanced scenarios.

## 2.2 Control of RWM

**Ideal wall.** One theoretical possibility, that should control RWM, is to have a perfectly conducting wall near the plasma boundary. In-fact the penetration of the B-field variation is fully stopped by the skin effect of an ideal conductive material and so the mode cannot expand. Obviously this is unfeasible and other control techniques have to be implemented.

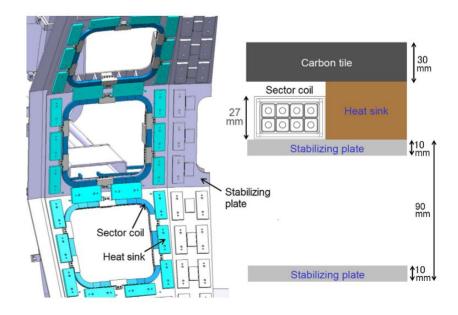

**Stabilizing plate (SP).** While a superconducting wall is not feasible, it is possible, however, to place inside the vacum vessel a conducting wall: the so called stabilizing plate. It cannot totally contain the B-field expansions, but, at least, it can slow them down to acceptable grow rate, making them much easily controllable. In JT-60SA, the SP, made of SS316LI, will be covered with composite carbon fiber (CFC), positioned over copper heat sinks, that are water cooled. So, the SP can slow down the growth time till 1 to 10 ms, making possible to control RWMs through active feedback control.

Active control. The active control, typically, needs a set of coil, positioned near the plasma, each one controlled independently by its own PS. JT-60SA, in-fact, will feature 18 RWM copper control coils (RWM-CC0), distributed symmetrically along the torus [1, 2]. The feed-back system needs pick-up coils in order to detect the magnetic flux. The MHD controller will take the feed-back signal from the sensors and then calculates in real-time the current that the correction coil must apply in order to suppress the kink expansion. Simulations, made with VALEN code [4], show that in JT-60SA the active control allows achieving a  $\beta$  limit near to the ideal-wall  $\beta$ . By the way, a strong coupling between plasma and coils is needed in order to obtain higher control efficiency, i.e. to minimize the current required to effectively suppress RWMs.

**Plasma rotation.** In DEMO, due to the high neutron production, it is not convenient to put coils inside the vacuum vessel, such as RWMCC. So, another control technique has been developed: rotational stabilization. In-fact, a rotational plasma can increase the shielding effectiveness of the SP. Typically, a toroidal plasma rotation of the first spatial harmonic is induced thanks to the NBIs and a 100 krad/s pulsation is reached [5]. This translates to an equivalent frequency of the B-field seen by the SP of 15 kHz. Hypothesizing that the SP is only made of copper, a 0.5 mm of depth of penetration is obtained. This method will be further tested in JT-60SA.

## 2.3 Coils design and characterization

At the present configuration of the system each coil will be placed on the inner side of the stabilizing plate (SP), as pictured in Fig. 2.2, so that each coil will require only 2.2 kAturns maximum because they will be close to the plasma and far less shielded by the SP. Each coil will have 8 turns, leading to a total absorbed current of 275 A. The square conductors will be disposed on 2 layers, each one containing 4 turns. They will be made of copper and they will be water cooled [6]. The insulator will be organic and must withstands the high temperatures. The coil will have a mean dimension of its sides of 0.85 m [7]. The coil can be seen as an ohmic-inductive load, in which the resistance and the inductance vary with frequency. In particular, the resistance increases with frequency due to skin and proximity effects, but also due to eddy current in passive surrounding structures. Instead, the inductance decreases with frequency due to the shielding effects. The coils will be connected to the respective power supply with coaxial cables (max length 88 m) and vacuum feeders (across and inside the vacuum vessel). The impedance of the load (including also cable and feeder) is shown in Table 2.1. The estimation has been obtained with FEM analysis (for coils and feeders) and from data-sheet (for cable).

As it can be noted, the load impedance is low. This is critical for the current ripple and control. In-fact with low impedance loads, the current tends to go out of control easily.

## 2.4 Cables

The converter is connected to the RWM-CC using a single coaxial cable, that is seen from the converter itself as part of the load. In order to minimize the voltage drop on the cable a 100mm<sup>2</sup> will be adopted. The length of the cable will be between 55 to 88m [9], different for each RWM-CC.

Figure 2.2: The design of RWM-CC of JT-60SA [8].

| Freq [Hz] | R [m $\Omega$ ] | L $[\mu H]$ | Impedance $[m\Omega]$ | Phase [degrees] |

|-----------|-----------------|-------------|-----------------------|-----------------|

| 1         | 52.6            | 143         | 52.6                  | 1.0             |

| 3         | 52.7            | 143         | 52.8                  | 2.9             |

| 10        | 53.3            | 140         | 54.0                  | 9.4             |

| 30        | 56.6            | 130         | 61.7                  | 23.4            |

| 100       | 72.4            | 107         | 98.8                  | 42.9            |

| 300       | 117             | 80.2        | 191                   | 52.3            |

| 1000      | 221             | 50.7        | 388                   | 55.2            |

| 3000      | 397             | 35.1        | 772                   | 59.0            |

| 10000     | 824             | 22.7        | 1650                  | 60.0            |

Table 2.1: RWMCC system main characteristics.

The main characteristics of the coaxial cable are listed in Table 2.2, while the estimated resistance and inductance as a function of frequency are listed in Table 2.3, considering the maximum length of 88m [10].

| Parameters                       | Values            |

|----------------------------------|-------------------|

| Rated Voltage                    | 600v              |

|                                  | 320A at 1kHz      |

| Rated Current                    | 295A at $5kHz$    |

|                                  | 165A at $10kHz$   |

| Cross-section (for conductor)    | $100 \text{mm}^2$ |

| Outside diameter (for conductor) | $15.4\mathrm{mm}$ |

| Insulator thickness              | 2.0mm             |

| Sheath thickness                 | $30\mathrm{mm}$   |

| Outside diameter (for cable)     | $30 \mathrm{mm}$  |

| Approximate wight                | 2200  kg/km       |

| Test voltage                     | AC3000V, 1 min    |

Table 2.2: Main characteristics of the cable.

| Frequancy (Hz) | AC loop resistance $(\Omega/\text{km})$ at 90°C | Inductance (mH/km) | Impedance $(\Omega/\mathrm{km})$ |

|----------------|-------------------------------------------------|--------------------|----------------------------------|

| 1              | 0.476                                           | 0.1143             | 0.476                            |

| 3              | 0.476                                           | 0.1143             | 0.476                            |

| 10             | 0.476                                           | 0.1143             | 0.476                            |

| 30             | 0.476                                           | 0.1143             | 0.476                            |

| 100            | 0.476                                           | 0.1143             | 0.481                            |

| 300            | 0.476                                           | 0.1143             | 0.523                            |

| 1000           | 0.460                                           | 0.0957             | 0.757                            |

| 3000           | 0.486                                           | 0.0824             | 1.63                             |

| 10000          | 0.670                                           | 0.0721             | 4.58                             |

Table 2.3: Frequency characterization of the cable.

## 2.5 PS and control main requirements

RWM will be controlled at frequencies up to 1 kHz [4], so the 3dB bandwidth of the control system has to be at least 3 kHz. Also, the system will have a very low allowable latency, less than 50  $\mu$ s. The 1 kHz limit is given by the need not to increase excessively the mode exponential growth, so that the required current is limited too. At that frequencies, the induced field is not so shielded by the surrounding structures, thanks to the position of the RWM-CC, towards the plasma.

Considering that 275 A are required in order to produce the stabilizing magnetic field and considering a certain margin, the PS should be able to feed the coil with a 300 A current. By the way, at 3 kHz there is a 3 dB attenuation, resulting in a 212.4 A peak current. In order to achieve this current value at 3 kHz, taking the load impedance, the voltage requested is 226 V. So, considering some voltage attenuation and physics uncertainties, the inverter should be rated for 240 V [6].

## 2.6 Plasma induced back-EMF

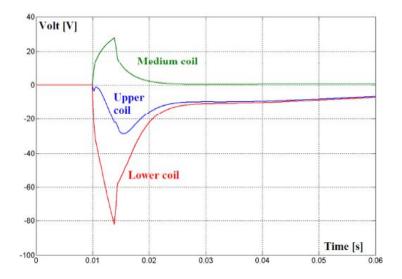

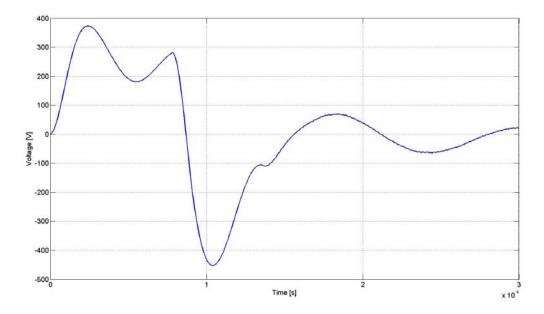

Then, we have to take in account the possible back-electromotive force (back-EMF) induced on the load by plasma current variation. The worst scenarios are plasma disruptions and vertical displacement events (VDE) happening when the plasma initially has the nominal current of 5.5 MA and with the minimum current decay time during disruptions of 4 ms. Simulations gave a resulting induced voltage, as shown in Fig. 2.3. With some margin,  $\pm 170$  V for 15 ms has been considered for the design of the system. When this back-EMF appears, the fast converter has to limit the possible consequent over-current below 30% of 300 A: this requires applying in few  $\mu$ s a counter voltage higher than the induced one, through a dedicated fast over-current protection [6].

Figure 2.3: Induced voltage in the sector coils during plasma disruption [6].

Table 2.4 summarizes the main specifications of the fast converters for RWM control [9].

| Description                                                         | Value                        |

|---------------------------------------------------------------------|------------------------------|

| Nominal output voltage at the inverter output terminals             | 240V                         |

| Maximum peak of a sinusoidal output current                         | 300A, continuously           |

| Nominal output current in dc operation                              | >100A                        |

| Maximum output current ripple                                       | $\pm 30 A$                   |

| Max. pulsed voltage induced into the load                           | $\pm 170$ V for 15 ms        |

| Bandwidth of the current at -3 dB (with current control loop)       | 3kHz                         |

| Maximum operation duty                                              | 100s/1800s                   |

| Maximum latency (between step reference and output voltage change)  | $50 \ \mu s$                 |

| Type of reference                                                   | Arbitrary, range $\pm 100\%$ |

| Accuracy of the load current in steady-state, up to 100 Hz          | $\pm 2\%$ of full scale      |

| Max. voltage/current overshoot with step variation of the reference | $\pm 15\%$                   |

| Max. current overshoot during induced voltage pulse                 | $\pm 30\%$                   |

| Dc-link operational range                                           | $50 \div 100\%$              |

| Maximum dc-link voltage variations in normal transient conditions   | $-15\% \div +10\%$           |

| Dc-link overcurrent during induced voltage pulse                    | +30%                         |

| Max ambient temperature                                             | 40°C                         |

| Max instantaneous differential voltage at the coil terminals        | $\pm 550 V$                  |

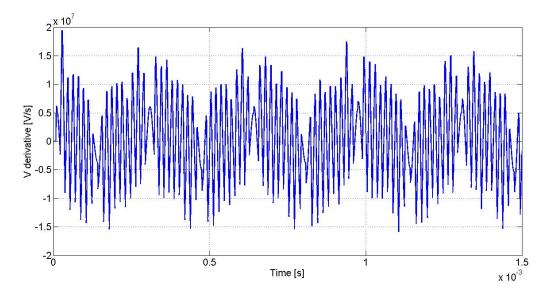

| Max dV/dt at the coil terminals                                     | $<\!20 \text{ MV/s}$         |

Table 2.4: Main specifications of the fast converters for RWM control.

## RWM power supply

#### 3.1 Introduction

The RWM-PS system is now under construction and it will be delivered in 2018. The system will be provided by EEI Equipaggiamenti Electronici Industriali S.p.a.

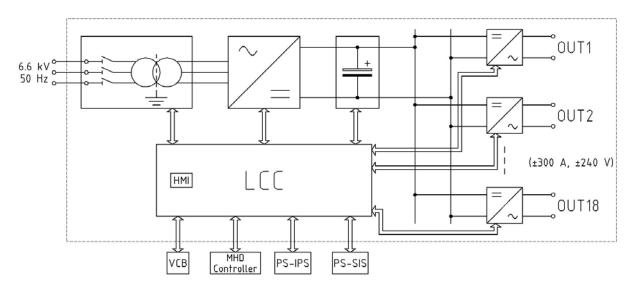

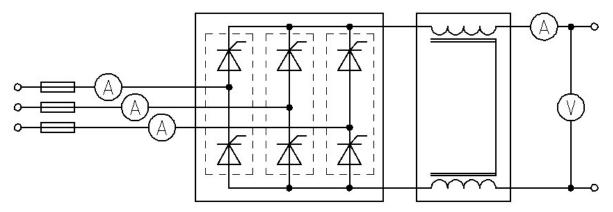

Every RWM-CC will be fed by its own four quadrant converter (full H-bridge topology). All the 18 fast converters are then connected to the same DC-link, as shown in Fig. 3.1, which will be supplied by a single three-phase AC/DC thyristor converter. This converter will be lastly connected to a step-down 50 Hz transformer. The transformer will be a 6.6 kV/290 V Dyn11, rated for 100 kVA nominal continuous power and a 200 kVA peak power (at least maintained for 100 s) [9]. The 6.6 kV three phase line will be provided by the existing electrical network in Naka.

Figure 3.1: Overview of the overall RWM-PS electrical scheme (courtesy of EEI).

Note that the 290 V secondary voltage is due to the DC-link chosen voltage, rated for 300 V. Furthermore, upstream the transformer there will be a manually-operated AC disconnector, provided by EEI, and a vacuum circuit breaker, provided by the customer.

## 3.2 AC/DC front-end

The aim of the AC/DC front-end is to convert the 290 V three phase AC voltage to a 300 V DC one. This will be made with a full bridge rectifier that, also, will have the capability to compensate voltage fluctuations within  $\pm 10\%$  of the nominal voltage. Because the energy regeneration towards the AC grid is

not requested, a thyristor based converter has been chosen, as the most economical and simple solution. Due to the needed 670A DC-current and 550 A AC-current, the rectifier topology will be the 6-pulse one, with 2 thyristor per branch, as pictured in Fig. 3.2. A smoothing choke will be placed at the converter downstream.

Figure 3.2: The AC/DC converter topology (courtesy of EEI).

The main specifications of the rectifier are listed in Table 3.1.

| Description                                                                             | Value                         |

|-----------------------------------------------------------------------------------------|-------------------------------|

| Nominal AC voltage (RMS)                                                                | 290 V                         |

| Nominal DC voltage                                                                      | 300 V                         |

| Nominal AC current (RMS)                                                                | 670 A                         |

| Nominal DC current                                                                      | 550A                          |

| Output power                                                                            | 200 kW                        |

| Range of operation of the voltage reference                                             | $60 \div 100\%$ of $V_{DC,n}$ |

| Maximum error between average dc-link voltage and reference voltage                     | $\pm 3\%$                     |

| Maximum rise time                                                                       | 5 s                           |

| Maximum dc-link voltage variations in normal transient conditions                       | $-15\% \div +10\%$            |

| Maximum dc-link overvoltage in case of pulsed electromotive force induced into the load | +20%                          |

Table 3.1: Main specifications of the rectifier.

## 3.3 DC-link nominal voltage

The nominal DC-link voltage ( $V_{DC,n}$ ) has to be chosen so that at 85% of  $V_{DC,n}$ , the required current control bandwidth (-3 dB at 3 kHz) can still be achieved. Knowing that the load impedance at 3 kHz is 397 m $\Omega$  and 35.1  $\mu$ H with 212.4 A<sub>pk</sub> (considering also the attenuation), the load peak voltage is 163.4 V. Then, adding the voltage drops on the output filter and on the fast converter switches (around 4V), it results a minimum DC-link voltage of 261V. So, taking some margin, the nominal DC-ink voltage is set to 300 V by EEI [9].

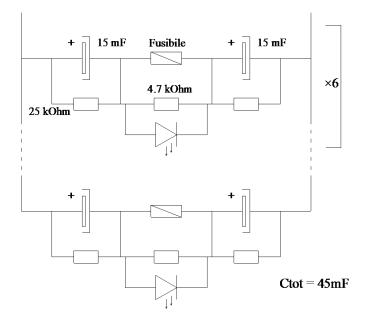

#### **3.4** DC-link capacitor bank

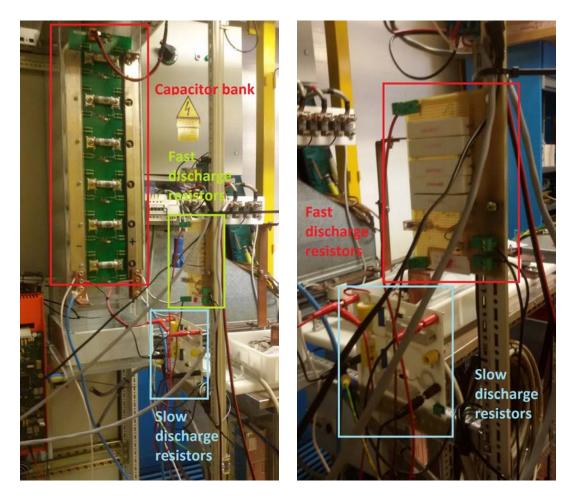

The capacitor bank is needed to aid the rectifier to regulate the DC-link voltage. Because the most demanding design criteria is the maximum DC-link over-voltage (20%) during plasma induced back-EMF, it has been identified the maximum energy fed back to the DC-link. This happens when each of the 18 inverters are feeding their RWMCC with the nominal 300A current and then a 170V back-EMF voltage appears on the load. So a  $170 \cdot 300 \cdot 18 = 918$ kW of power is fed back for 15ms, leading to a energy of 13.5kJ.

Imposing that all this energy goes in the capacitors, then a 0.68F total capacitance is required in order to

#### 3.5. FAST CONVERTER

limit the over-voltage within the  $\pm 20\%$  of 300V. In the end, considering a certain margin, a 1F electrolytic capacitor bank has been chosen by EEI [9].

## 3.5 Fast converter

Downstream the capacitor bank there is, finally, the fast converter. It is basically composed by 3 stages: input filter, H-bridge, output filter. It will be discussed in the next chapters.

## The dummy load

#### 4.1 Introduction

Because the real load to which the converter will be connected is not available yet, in order to test the prototype, a dummy load (DL) was provided by OST with a frequency characteristic as far as possible similar to the real one. In particular it is important that the dummy load will have the same impedance of the real one at 1 kHz and 3 kHz.

## 4.2 Dummy load characterization

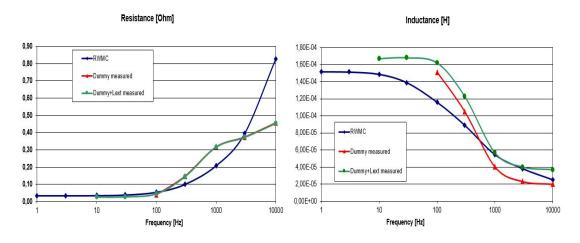

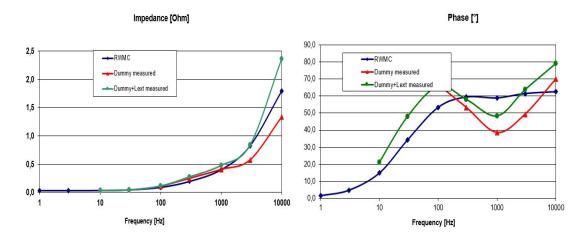

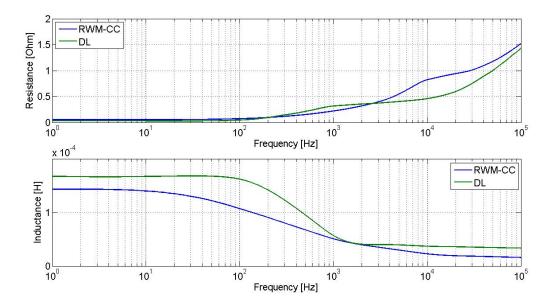

The dummy load is made of a massive copper coil, without any ferromagnetic core, that is wrapped around a stainless steel cylinder. The cylinder is necessary in order to reproduce the impedance characteristic of the real RWM-CC as function of frequency. By the way, the coil itself didn't match the requested specification so three series inductances have been added downstream the dummy load, that have 16.9  $\mu$ H and 3.5 mΩ.

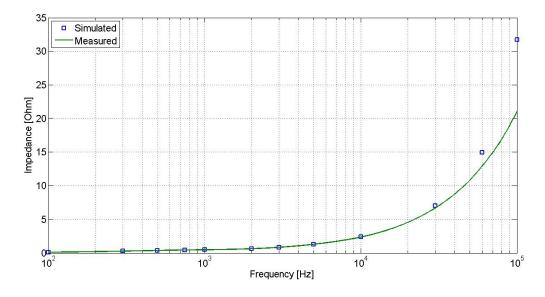

So, the final characteristic is as illustrated in the subsequent Table 4.1 and graphs in Fig. 4.1 and 4.2. However the resistance and phase at 1 kHz are different from the real RWM-CC, so its current response at those frequencies is different in CCM.

| Frequency [Hz] | R dummy $[\Omega]$ | L dummy $[\mu H]$ | Impedance $[\Omega]$ | Phase [°] |

|----------------|--------------------|-------------------|----------------------|-----------|

| 1              | 2.69E-02           | 167.1             | 2.69E-02             | 2.2       |

| 10             | 2.69E-02           | 167.0             | 2.89E-02             | 21.3      |

| 30             | 2.85E-02           | 168.0             | 4.26E-02             | 48.0      |

| 100            | 4.6E-02            | 162.0             | 1.12E-01             | 65.7      |

| 300            | 0.144              | 122.8             | 2.73E-01             | 58.0      |

| 1000           | 0.3167             | 56.7              | 4.77E-01             | 48.4      |

| 3000           | 0.3728             | 40.0              | 8.41E-01             | 63.7      |

| 10000          | 0.459              | 36.9              | 2.37                 | 78.9      |

| 20000          | 0.596              | 35.9              | 4.56                 | 82.48     |

| 30000          | 0.751              | 35.2              | 6.68                 | 83.55     |

| 40000          | 0.891              | 34.7              | 8.78                 | 84.17     |

| 50000          | 1.00               | 34.3              | 10.83                | 84.69     |

| 60000          | 1.11               | 34.1              | 12.92                | 85.07     |

| 70000          | 1.20               | 33.8              | 14.93                | 85.38     |

| 80000          | 1.29               | 33.6              | 16.96                | 85.65     |

| 90000          | 1.36               | 33.5              | 19.02                | 85.89     |

| 100000         | 1.43               | 33.4              | 21.06                | 86.11     |

Table 4.1: The measured R and L with the addition of the external inductance.

Figure 4.1: The DL resistance and inductance.

Figure 4.2: The DL impedance and phase.

Figure 4.3: The dummy load.

## The fast converter

## 5.1 Introduction

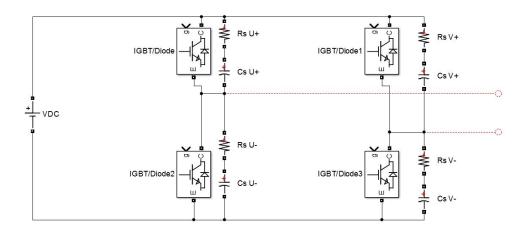

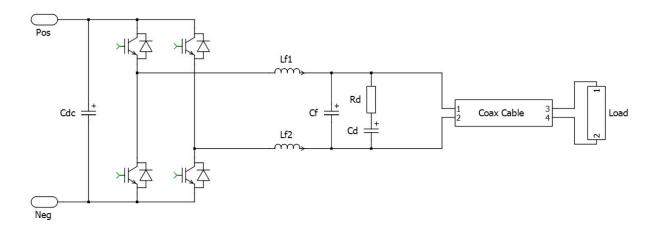

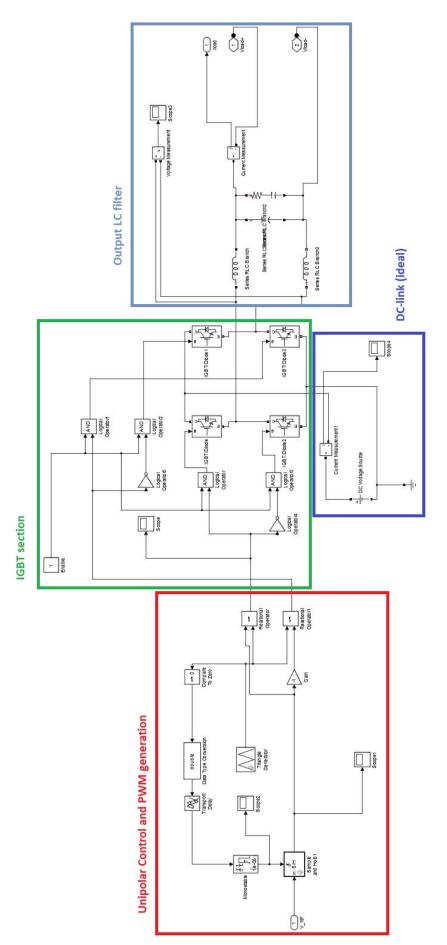

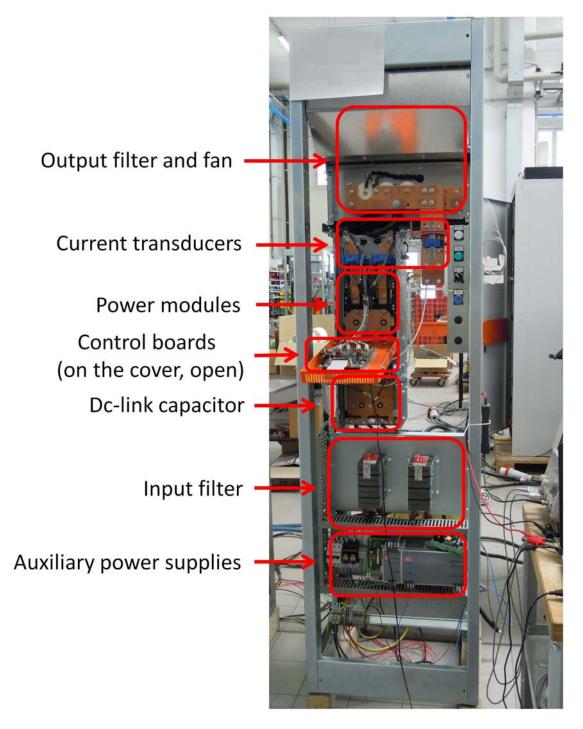

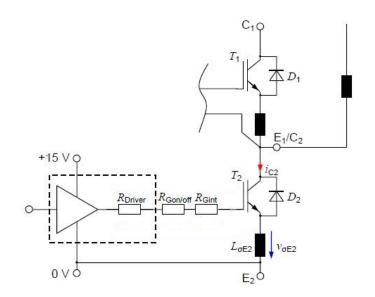

The RWM-PS system will include 18 identical four quadrant fast converters. The topology is the one shown in Fig.5.2. Each converter will have its own control board. A PWM unipolar modulation is adopted, due to its capability to double the output frequency.

Furthermore, a prototype has been built in order to verify the feasibility of the dynamic requirements by using commercially available components with reasonable prices.

## 5.2 Power semiconductors

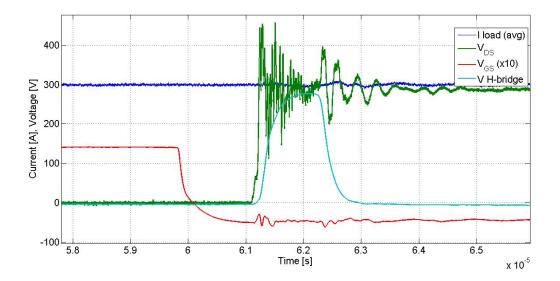

Considering the 3 kHz bandwidth, an output frequency between 40 to 60 kHz is needed, that means a switching frequency of 20 to 30 kHz, too high for Si-based IGBT modules, using the H-bridge topology. Anyway, such frequencies can be achieved with hybrid Si-SiC IGBTs modules, where only the anti-parallel diodes are made of SiC. These diodes have a lower reverse recovery current than Si diodes, thus reducing commutation losses.

An Infineon FF600R12IS4F IGBT module is used for each leg has been chosen by EEI [9]. The module is composed of two Si IGBTs (Infineon fast IGBT2 technology, 600 A, 1200 V) and two antiparallel SiC diodes (360 A, 1200 V) and it is suitable for high switching frequency applications.

With these components a 30kHz switching frequency has been reached on the prototype, thus an output frequency of 60kHz.

In addition, in order to reduce commutation stresses on the IGBT, RC parallel snubbers ( $R_s = 1.65 \Omega$ ,  $C_s = 20 \text{ nF}$ ) have been adopted by EEI for each switch. The composition of the H-bridge with the snubbers can be seen in Fig. 5.1.

Figure 5.1: The topology of the H-bridge with the snubbers.

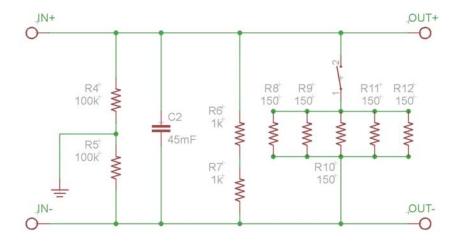

#### 5.3 Input capacitor bank

Film capacitors are installed close to the H-bridge at input side. In combination with a couple of differential-mode inductance, they form an input filter against the high-frequency components of the input current. The most critical requirements are their current rating and high frequency performance, required to filter out the current harmonics (60kHz and multiples). Also, they are subjected to a current frequency that is twice the fundamental load current frequency.

6 off DUCATI energia DC85C series (650  $\mu$ F each, 900 Vdc) have been chosen by EEI for the prototype because readily available. They are characterized by reasonably low self inductance (<60 nH each) and series resistance (3.5 m $\Omega$  each), and sufficient rated rms current (40 A each).

#### 5.4 Output filter

An output filter is required in order to:

- 1. reduce the current ripple;

- 2. avoid overvoltages on the coaxial cable,

- 3. uniform the load impedance, that may vary due to different cable lengths;

- 4. reduce electro-magnetic-interference (EMI) produced by voltage rising/falling fronts.

About the cable overvoltage problem, one must considers that the rise/fall  $\tau_r$  time of the voltage at the switches end is about 100 ns: so the propagation effects along the cable must be considered. Firstly the dielectric constant of the cable must be calculated using the formula:

$$\varepsilon_r = \frac{\ln(D/d) \cdot C}{2\pi\varepsilon_0 \cdot l} \tag{5.1}$$

where D is the return shield diameters, d is the internal core diameter, C/l is the cable capacitance and it results  $\varepsilon_r = 4$ . Then it is possible to calculate the critical length, defined as the cable length at which voltages up to twice the DC-link voltage can be expected at load terminals:

$$l_c = \frac{\pi \cdot c \cdot \tau_r}{4\sqrt{\varepsilon_r}} \tag{5.2}$$

which yields a critical length of 12m. The use of PWM with high carrier frequencies in association to cable length higher than the critical length may lead to overvoltage up to two to three times the DC-Link voltage at the load terminals [9, 11].

From the requirements, a maximum  $\pm 30$ A of current ripple is imposed, that is 10% of the nominal 300A current. Considering that the ripple frequency is at 60kHz and choosing an LC filter, that give a -40 dB/dec attenuation after the resonance frequency, it should be placed 0.5 decades before the switching frequency, leading to a 20kHz resonance frequency.

The filter inductance has been chosen by EEI keeping in mind that the higher the inductance, the lower the filter current ripple, but the higher the required DC-Link rated voltage to provide the required performance. So, from the requirements, the current on the inductance should not increase more than 60A during the time interval in which the full DC-link voltage (300 V) is applied on the load. Assuming to have the nominal voltage on the capacitance (240V), when the H-bridge applies 300 V at the output, 60 V are applied on the inductance. Because in order to maintain 240V on the load the required duty cycle is 0.8, the full 300V voltage is maintained for  $\Delta t=0.8/60000=13.33 \ \mu s$ . So, from the formula:

$$\Delta I = \frac{V_L}{L} \cdot \Delta t \tag{5.3}$$

Imposing  $\Delta I=60A$  and  $V_L=60V$ , it is L=13.3  $\mu$ H. Given the sizes available in the market, 2 inductances of 6  $\mu$ H have been chosen by EEI.

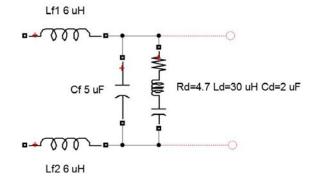

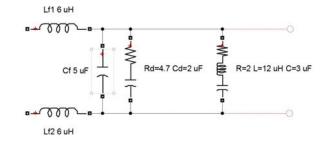

To obtain the chosen resonance frequency a 5  $\mu$ F capacitance is then required. By the way, a damping RC branch is needed to reduce the resonance peak of the transfer function and it is made with a 4.7  $\Omega$  resistor and a 2  $\mu$ F capacitance. That results in two parallel branches: one with the RC series and one

Figure 5.2: The fast converter and output filter topology (courtesy of EEI), where Lf1=Lf2= 6  $\mu$ H, Cf=4  $\mu$ F, Cd=2  $\mu$ F, R=4.7  $\Omega$ .

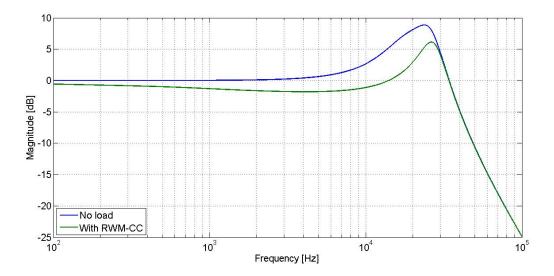

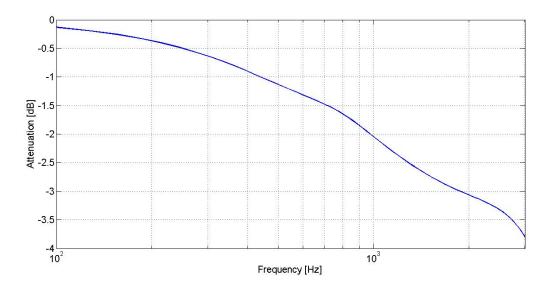

Figure 5.3: Attenuation of the filter with the RWM-CC connected (green) and without it (blue).

with a 4  $\mu$ F capacitance, as shown in Fig. 5.2. Fig. 5.3 shows the voltage attenuation of the filter; note how with the RWM-CC connected the resonance peak is lower and, also, there is a certain attenuation of the voltage at lower frequencies, while without the load the filter is virtually transparent to the voltage.

#### 5.5 Control board

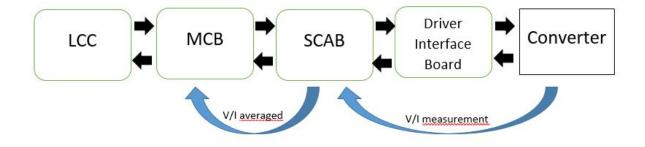

The converter control system has to be very fast in order to satisfy the dynamic requirements, such as the low latency. In addition to that the control boards will feature a complete set of communication ports, which include Ethernet ports, digital and analog ports. These are needed in order to communicate with the SCSDAS, through the local control cubicle (LCC). Also, all the I/O signals have to be safely galvanic insulated from the power section.

So, the control boards of the prototype have a master/slave configuration, in which:

- a slave control board (SCAB) is designed with an Altera Cyclon V FPGA, with a 4ns resolution (245 MHz clock), that manages all the feedback measurements and can actively modify the PWM gate pulses;

- a master control board (MCB) is made with a Texas Instruments (TI) 32-bit 60MHz ARM microcontroller that supervises and controls the operation of the entire converter.

All the acquired signals are in the analog  $(\pm 10 \text{ V})$  form, while parameters (alarms and values) exchange between the converter control boards and the LCC are made via Ethernet.

So, the SCAB acquires both the load current and voltage with two fast (3 Msps) 12-bit ADCs with SPI interface. Then it averages them with a 16-sample or 32-sample per each half PWM period average and it sends these signals to the MCB by converting the obtained digital signals to analog ones. Then the MCB samples the feed-back signals and executes the main control routine. A qualitative scheme of the control sistem can be seen in Fig. 5.4.

Figure 5.4: A simple scheme of the control board.

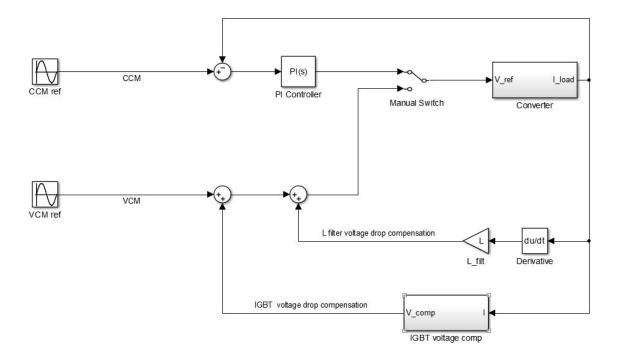

Two control schemes are available:

- 1. Mode 1: Current Control Mode (CCM), that is a closed-loop scheme;

- 2. Mode 2: Voltage Control Mode (VCM), that is an open-loop and a faster control scheme.

In CCM the current is regulated by a simple PI controller with anti-windup function, that is executed with a 60kHz rate (around every 16.67  $\mu$ s). It receives the averaged feed-back current by the SCAB, then it executes the PI algorithm and generates the unipolar PWM switching pattern. The chosen execution rate and PWM frequency yield a worst-case latency between reference step and duty-cycle variation of less than 50  $\mu$ s as required.

In VCM, voltage drops both on the switches and the output filter inductances have to be compensated. For the switches, a numerical characteristic is implemented, while, for the inductances, the voltage drops are compensated by calculating the derivative of the current at each PWM cycle. Both these compensations are directly implemented in the main control routine. The resulting control scheme can be seen in Fig. 5.5.

Figure 5.5: A scheme that shows the main control blocks.

#### 5.6 Voltage slope limits

The nominal dV/dt limit is 20 MV/s, but it would be better if the effective voltage slope on the load was reduced toward 10 MV/s to improve the voltage distribution among coil turns against capacitive effects. The voltage slope strictly depends on the output filter. In the prototype, the filter guarantees a maximum dV/dt that is between 15 and 20 MV/s. So, additional analysis have been started out by the Author in order to further reduce the voltage slope.

#### 5.7 Thermal limits

Firstly it is to be noted that the actual prototype is only air-cooled, while the final product will be water-cooled. This is because the air cooling is sufficient in order to reach the objectives the prototype is meant for. In particular, the maximum pulse length for the prototype has been set to 2 s.

From the IGBTs data-sheets, 1.9kW losses have been calculated by EEI with 300 A peak at 500Hz, with a worst-case junction temperature of 125°C. In DC operation, due to the fixed current sign, on each switch only the IGBT or the diode conduct. This lead to a worsening of the operating condition: in-fact simulations show greater losses on the switches, up to 2.76kW with  $300A_{DC}$ . By the way, the converter prototype was able to run safely and indefinitely with a load current of at least 100  $A_{DC}$ . In addition, the water-cooled converter will exceed the performance of the prototype and will be able to provide a 300 A peak sinusoidal waveform indefinitely. In any case, the converter has to be capable to provide 300  $A_{DC}$  until the switch junctions are in thermal regime with the respective case, without damages. It is acceptable that, after some time, the thermal protection, based on the NTC sensor embedded with the case, intervenes.

## The converter model

#### 6.1 Introduction

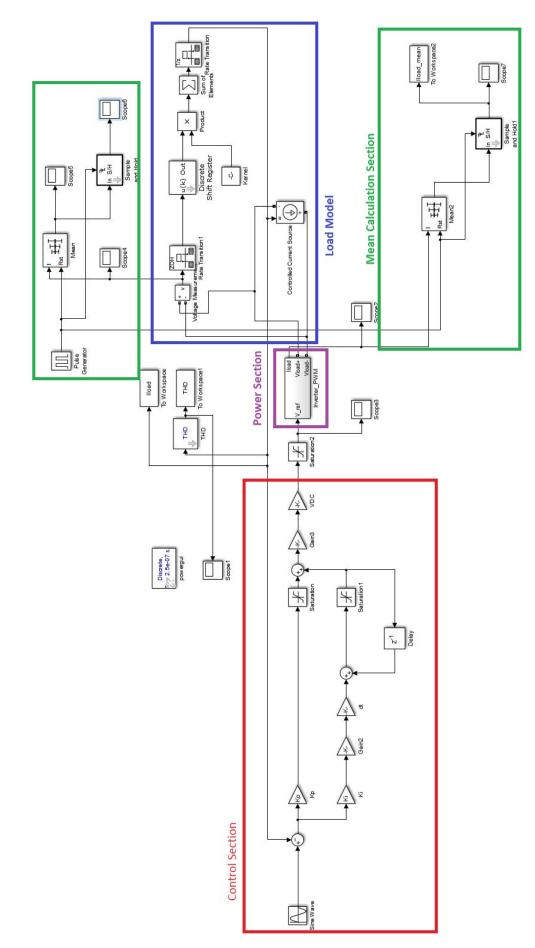

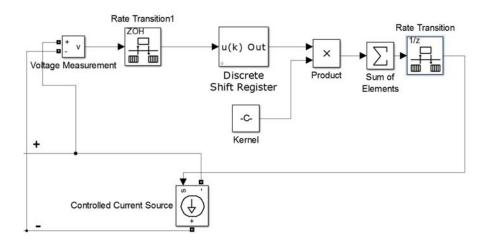

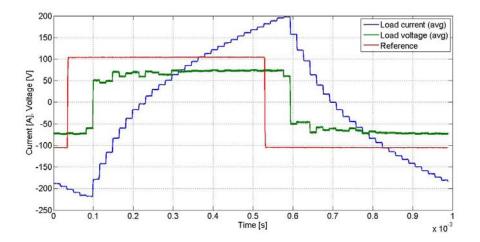

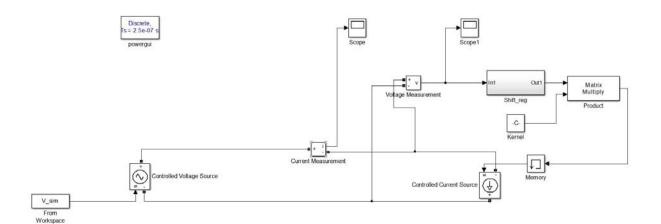

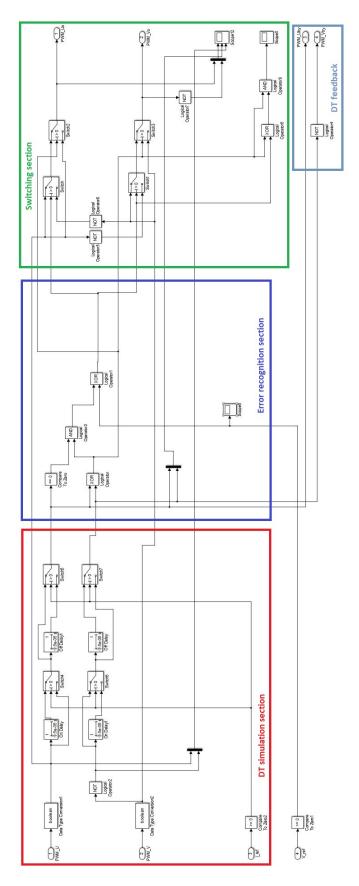

In order to optimize and study the PS behavior, a mathematical model of the system is needed. The model has been implemented both with PSIM( $\mathbb{R}$ ) and Matlab Simulink( $\mathbb{R}$ ). The load, with its particular impedance, was initially modeled with Cauer cells by EEI using PLECS( $\mathbb{R}$ ), then researchers at Consorzio RFX ported the model in the PSIM( $\mathbb{R}$ ) platform and also they modeled it with a convolution-based one. While the Cauer model replicates the quasi-exact impedance of the load for frequency up to 3 kHz, the convolution-based one could replicate the behavior also at much higher frequencies, also beyond the switching frequency, allowing to see the effects on the load of PWM frequency. By the way, this model needs further validations of its results, that is one of the objectives of this thesis. Note that the original convolution-based model developed by Consorzio RFX is made with the SimCoupler S-function: a Simulink( $\mathbb{R}$ ) block that interfaces Simulink( $\mathbb{R}$ ) itself and PSIM( $\mathbb{R}$ ). In-fact, the whole H-bridge and control section was originally developed on the PSIM( $\mathbb{R}$ ) platform by Consorzio RFX. Then the Author made the porting of the whole power and control section in Simulink( $\mathbb{R}$ ) obtaining a half of the initial simulation time. The final model is shown in Fig. 6.1.

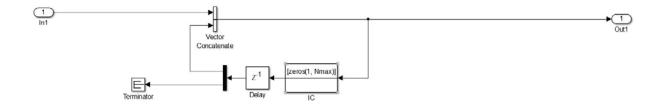

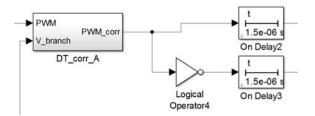

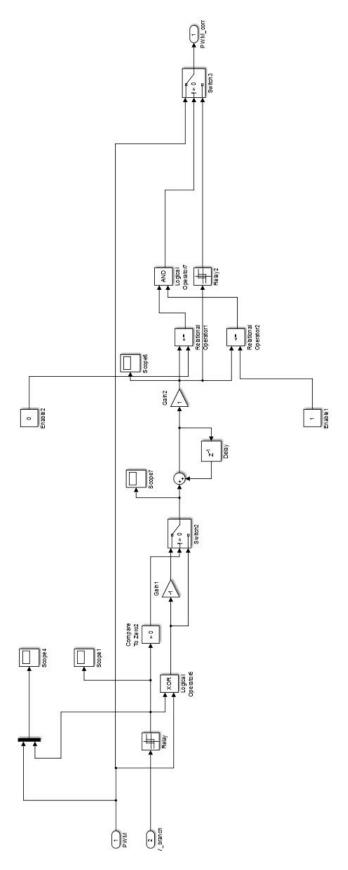

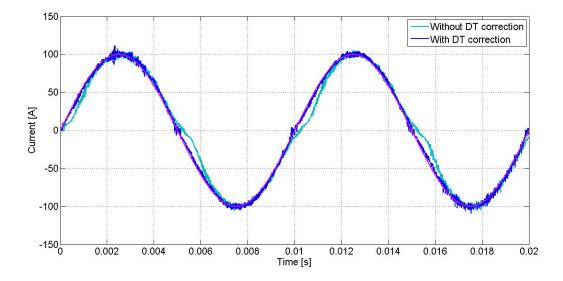

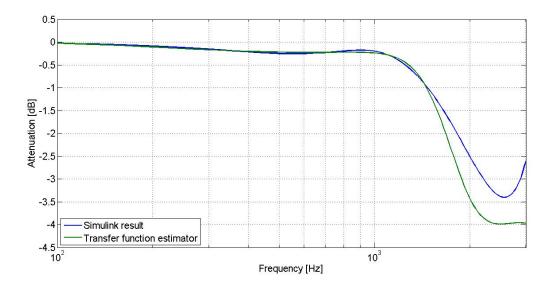

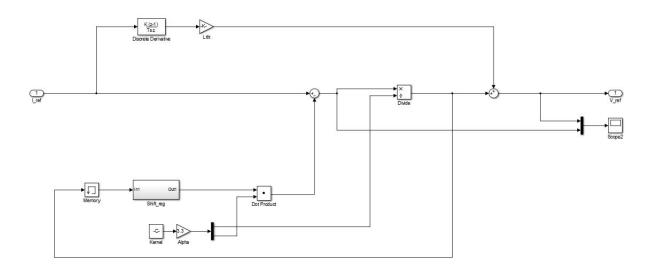

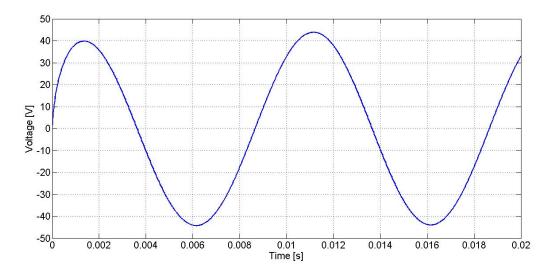

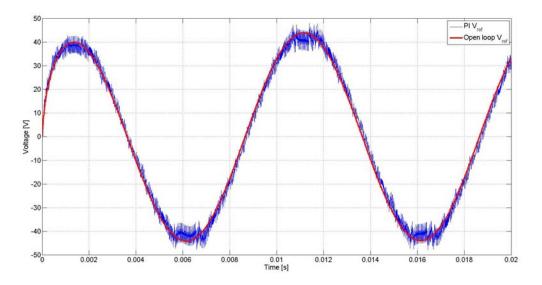

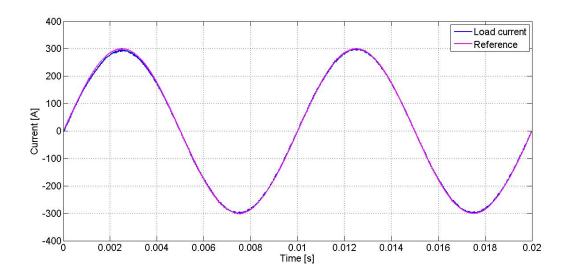

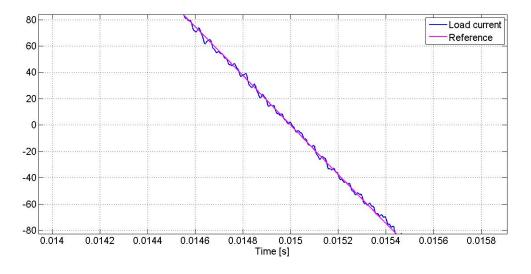

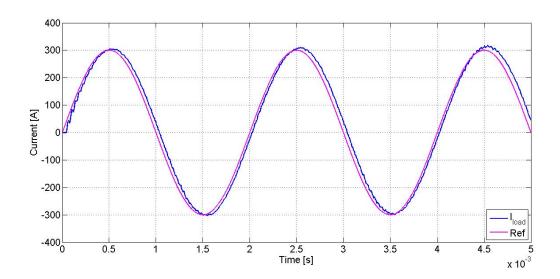

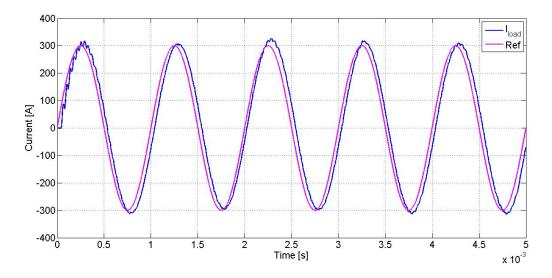

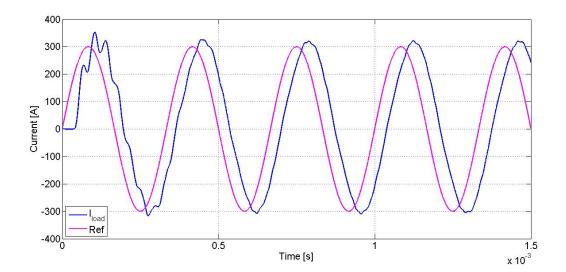

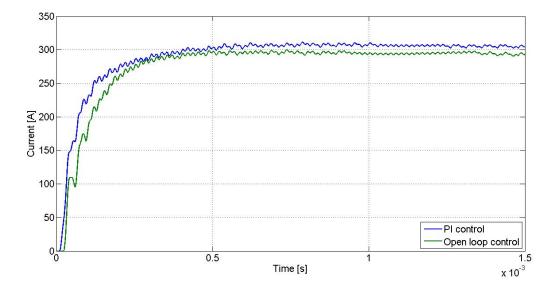

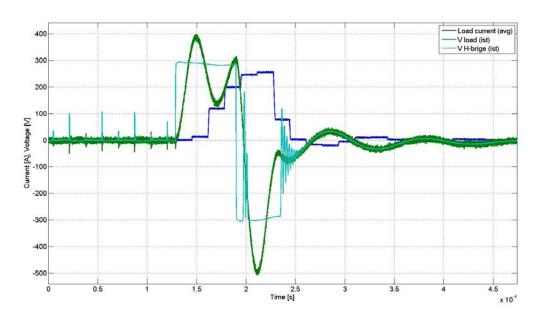

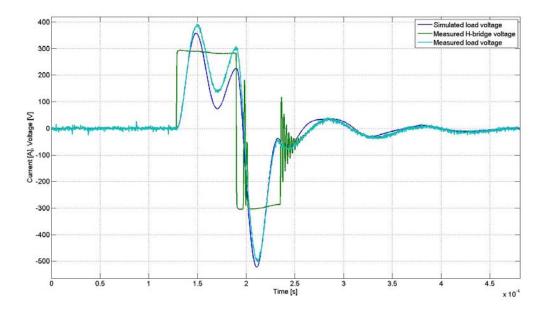

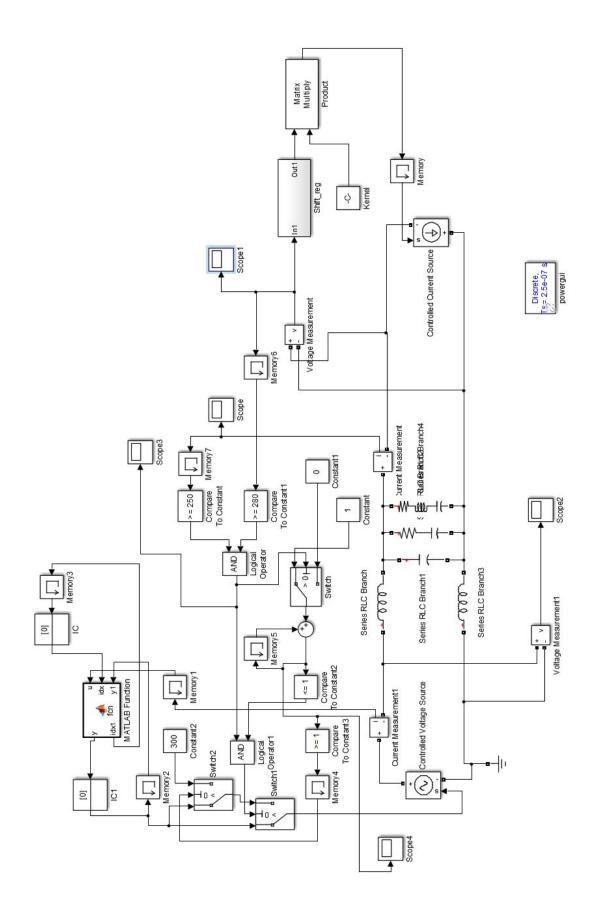

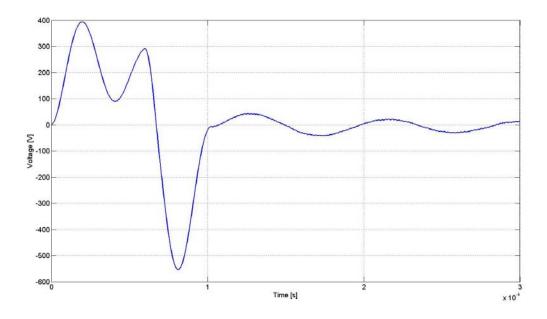

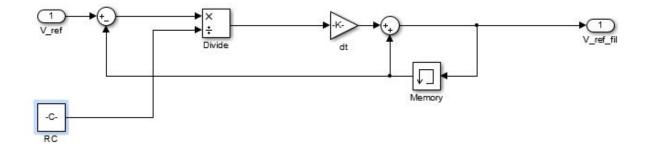

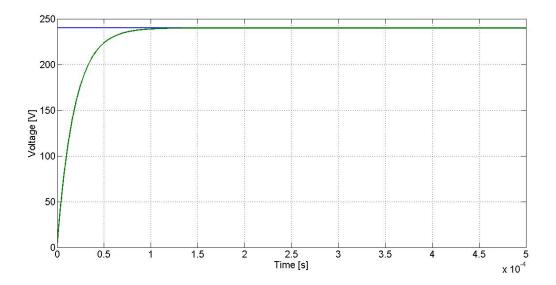

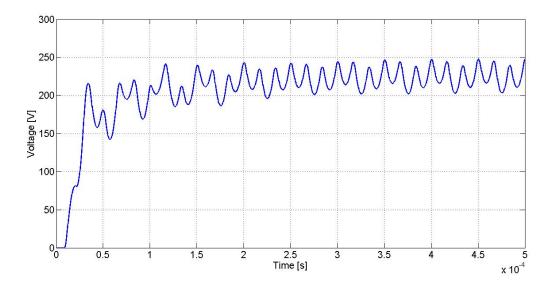

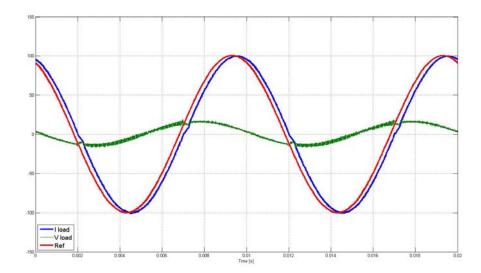

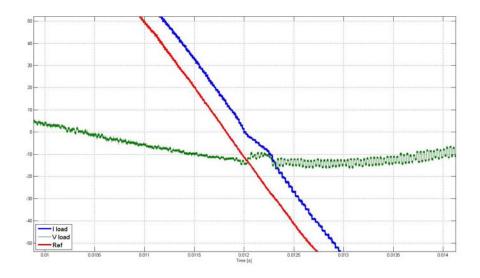

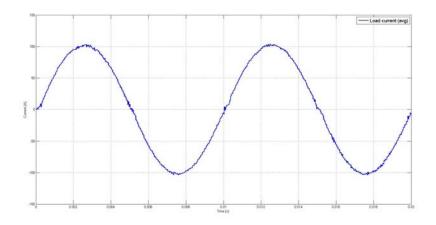

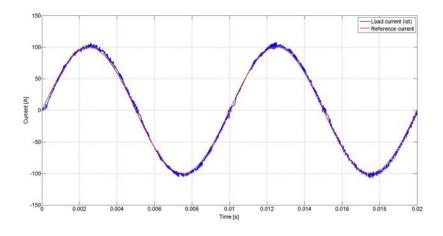

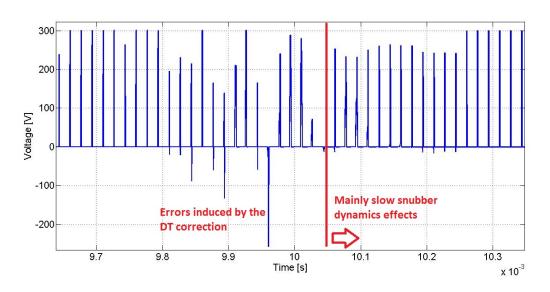

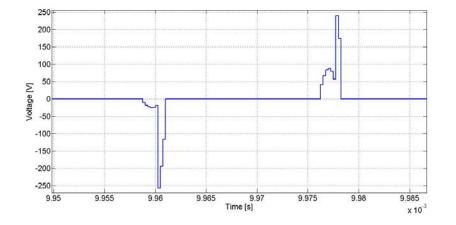

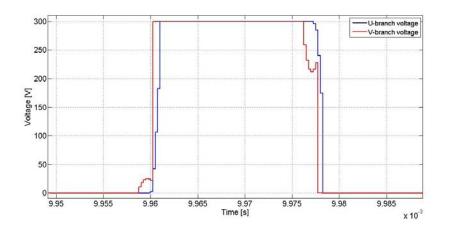

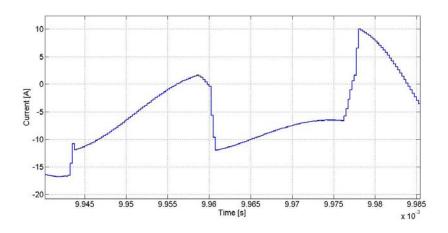

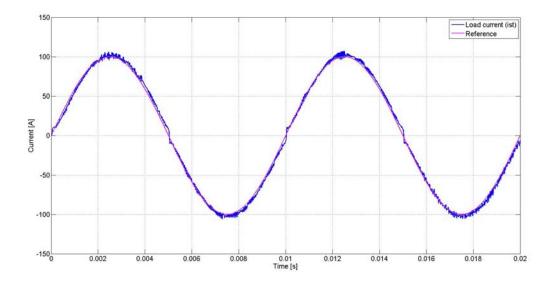

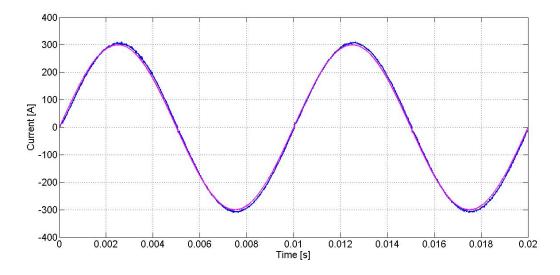

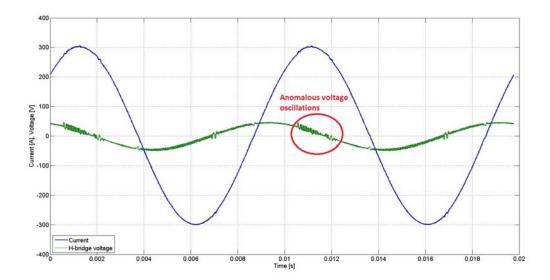

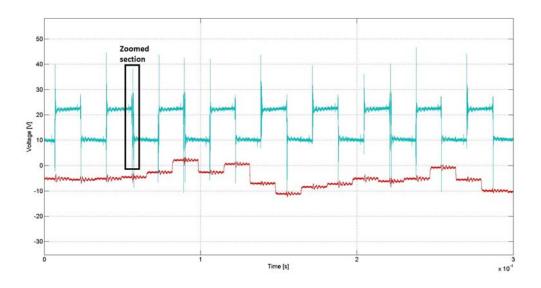

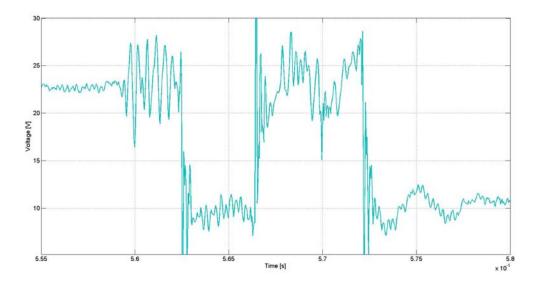

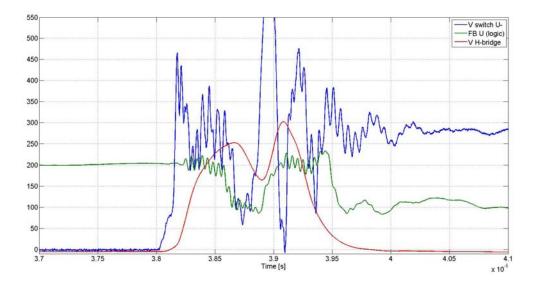

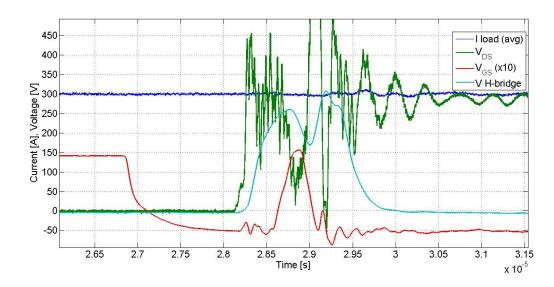

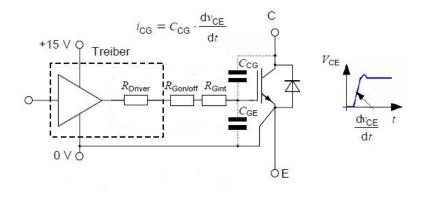

#### 6.2 The Simulink® fast converter model