## UNIVERSITÀ DEGLI STUDI DI PADOVA Dipartimento di Ingegneria dell'Informazione

Corso di laurea magistrale in Ingegneria Elettronica Tesi di laurea magistrale

# Progettazione di un amplificatore di potenza in classe J in tecnologia CMOS

Laureando

Thomas Stefanello

ANNO ACCADEMICO 2016/2017

#### Sommario

In letteratura sono proposte diverse classi di funzionamento per un amplificatore, caratterizzate da particolari configurazioni circuitali che danno luogo alcune ad elevata efficienza ed altre ad una buona linearità. Applicazioni innovative come lo standard 5G per la rete mobile, richiedono specifiche in tal senso non indifferenti, e una classe di amplificatori che può soddisfarle è la classe J. In particolare, lo standard di quinta generazione per le comunicazioni mobili necessita di amplificatori di potenza usati per pilotare schiere di antenne a larga banda, che permettano di avere una buona linearità, e che siano efficienti senza sacrificare la potenza di uscita. Questo deve essere realizzato per una frequenza di centro banda compresa tra 10GHz e 73GHz.

In questa tesi verrà presentato un amplificatore di potenza in classe J basato su una tecnologia CMOS da 130nm, allo scopo di verificare l'effettiva possibilità di realizzare questo tipo di PA con dispositivi CMOS. Inoltre saranno stimate le prestazioni che si riescono ad ottenere per permettere un confronto con altre soluzioni che usano tecnologie più performanti ma dal costo maggiore. Le specifiche che si cercheranno di rispettare riguardano la potenza di uscita fissata a 20dBm, e la frequenza di funzionamento pari a 10GHz. Verrà infine testata l'efficacia di un metodo per la riduzione della conversione AM-to-PM.

## Indice

| In | trod | uzione                             | vii |  |  |  |  |  |

|----|------|------------------------------------|-----|--|--|--|--|--|

|    | Stat | o dell'arte                        | xii |  |  |  |  |  |

|    | Con  | tributo e struttura della tesi     | XV  |  |  |  |  |  |

| 1  | Ric  | hiami teorici                      | 1   |  |  |  |  |  |

|    | 1.1  | Serie di Fourier                   | 1   |  |  |  |  |  |

|    | 1.2  | Figure di merito                   | 2   |  |  |  |  |  |

|    | 1.3  | Parametri di scattering            | 4   |  |  |  |  |  |

|    | 1.4  | AM-PM conversion                   | 6   |  |  |  |  |  |

|    | 1.5  | Classi di funzionamento per PA     | 7   |  |  |  |  |  |

|    |      | 1.5.1 Classe A                     | 8   |  |  |  |  |  |

|    |      | 1.5.2 Classe B                     | 9   |  |  |  |  |  |

|    |      | 1.5.3 Classe AB                    | 10  |  |  |  |  |  |

|    |      | 1.5.4 Classe C                     | 10  |  |  |  |  |  |

|    |      | 1.5.5 Classe D                     | 12  |  |  |  |  |  |

|    |      | 1.5.6 Classe E                     | 12  |  |  |  |  |  |

|    |      | 1.5.7 Classe F                     | 13  |  |  |  |  |  |

|    |      | 1.5.8 Classe J                     | 14  |  |  |  |  |  |

|    | 1.6  | Trasformatori                      |     |  |  |  |  |  |

| 2  | Pro  | gettazione circuitale              | 21  |  |  |  |  |  |

|    | 2.1  | Rete di carico                     | 21  |  |  |  |  |  |

|    | 2.2  | Dimensionamento dei transistor     | 26  |  |  |  |  |  |

|    | 2.3  | Circuito di polarizzazione         | 27  |  |  |  |  |  |

|    | 2.4  | Miglioramento AM-to-PM conversion  | 30  |  |  |  |  |  |

|    | 2.5  | Rete di adattamento in ingresso    | 32  |  |  |  |  |  |

| 3  | Ris  | ultati di simulazione              | 35  |  |  |  |  |  |

|    | 3.1  | Circuito con trasformatore teorico | 37  |  |  |  |  |  |

|    | 3.2  | Trasformatore di uscita            | 44  |  |  |  |  |  |

|    | 3.3  | Circuito con trasformatore reale   |     |  |  |  |  |  |

| 4  | Cor  | Conclusione 53                     |     |  |  |  |  |  |

|    | 4.1  | Sviluppi futuri                    | 54  |  |  |  |  |  |

## Introduzione

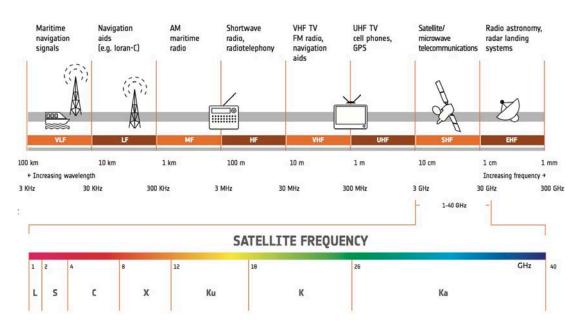

Con il termine banda radio si indica l'insieme di tutte le possibili frequenze delle radiazioni elettromagnetiche adibite per le comunicazioni radio, ovvero senza fili. Essendo un mezzo trasmissivo condiviso e non dedicato, l'utilizzo di questo spettro è ben regolamentato, allo scopo di non creare conflitti ed interferenze tra i diversi segnali. Come mostrato in figura 1, ogni applicazione fa riferimento ad uno specifico range di radio frequenze (RF).

Figura 1: Ripartizione della banda radio (da 3KHz a 300GHz) riferita ai diversi campi di utilizzo con in dettaglio la suddivisione della banda da 3GHz a 300GHz.

Per quanto riguarda le comunicazioni mobili, tutti gli attuali sistemi usano la banda denominata  $Ultra\ High\ Frequency\ (UHF)$  che parte da 300MHz e termina a 3GHz. Il rapido aumento del numero di smartphone e di altri dispositivi mobili connessi, unito allo svilupparsi dell' $Internet\ of\ Things\ (IoT)$  per mezzo del quale anche gli oggetti più comuni saranno collegati alla rete, stanno portando il traffico mobile ad una crescita senza precedenti. Così come questa crescita avanza, si ha che lo spettro UHF risulta sempre più popolato. Per questo motivo, negli ultimi anni, lo studio di dispositivi e sistemi operanti a frequenze superiori ai 3GHz si è

intensificato. Il range 3-30GHz è generalmente indicato come banda SHF (Super High Frequency), mentre il range 30-300GHz è conosciuto come EHF (Extremely High Frequency) o banda millimetrica con riferimento alla lunghezza d'onda. Viste le caratteristiche di propagazione simili che accomunano questi due range di frequenze, spesso con il termine "onde millimetriche", abbreviato in mm-wave, ci si riferisce all'intero intervallo 3-300GHz. Fortunatamente la banda millimetrica risulta ancora scarsamente sfruttata ed alcuni sistemi di comunicazione punto-punto già sviluppati, che lavorano a 60GHz, hanno dimostrato la possibilità di raggiungere elevate velocità di trasferimento dei dati su distanze di qualche chilometro. Tuttavia questi sistemi sono costituiti da dispositivi, come amplificatori, mixers ed antenne, caratterizzati da dimensioni e consumi proibitivi per l'impiego nelle comunicazioni mobili. Si presenta quindi la sfida ingegneristica di creare componenti elettronici con bassi consumi, alta efficienza e di dimensioni contenute in modo da poter essere impiegati nei futuri sistemi di comunicazione.

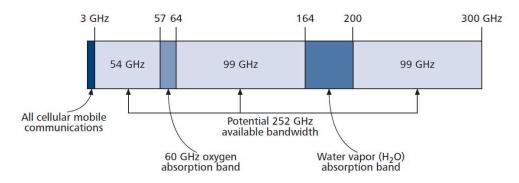

Dell'intero spettro delle onde millimetriche, più di 250GHz possono teoricamente essere impiegati nelle communicazioni, come mostrato in figura 2. Alcuni intervalli di frequenze non sono presi in considerazione a causa di particolari fenomeni come l'assorbimento di energia elettromagnetica da parte delle molecole di ossigeno tra i 57GHz e i 64GHz che porta ad un'attenuazione di circa 15dB/km. Anche l'acqua presente in atmosfera può causare un'attenuazione di decine di dB per chilometro nel range 164 - 200GHz. Se si considera anche la volontà di lasciare libero circa un 40% dello spettro rimanente per sviluppi futuri, resta comunque una banda di 100GHz disponibile per le nuove comunicazioni mobili, più di 200 volte lo spettro correntemente allocato per questo scopo [1].

Figura 2: Spettro delle onde millimetriche.

Un errore diffuso riguardante le reti wireless è quello di considerare l'attenuazione di spazio libero dipendente solo dalla frequenza, così facendo si ha che trasmissioni nell'ordine dei GHz sono meno performanti di quelle a frequenze più basse. Questo risulta vero sotto l'assunzione restrittiva di utilizzare un'unica antenna con apertura effettiva che aumenta con la lunghezza d'onda e cala con la frequenza. Infatti, in tali condizioni, un'antenna con maggiore apertura ha un guadagno più alto rispetto ad una di dimensioni effettive più contenute. Tuttavia, lavorando con le onde

millimetriche, più antenne possono essere disposte nella stessa area occupata da un ricevitore o trasmettitore che opera a lunghezze d'onda maggiori cancellando gli apparenti svantaggi dovuti all'attenuazione di spazio libero. Inoltre, l'alto numero di antenne permette di utilizzare la tecnica del beamforming che porta ad un ulteriore incremento di guadagno.

Mentre segnali a basse frequenze possono raggiungere facilmente l'interno degli edifici, le *mm-wave* faticano ad attraversare materiali solidi. In tabella 3 sono riportati valori tipici di attenuazione per i materiali edili più comuni. Per evitare che il segnale resti confinato nelle strade e all'esterno delle abitazioni, un possibile standard di comunicazione che utilizza la banda millimetrica deve perciò prevedere l'impiego di femtocelle o altre soluzioni simili.

| Materiale         | Spaceage [em] | Attenuazione [dB] |        |        |  |  |

|-------------------|---------------|-------------------|--------|--------|--|--|

| iviateriale       | Spessore [cm] | < 3 GHz           | 40 GHz | 60 GHz |  |  |

| Cartongesso       | 2.5           | 5.4               | -      | 6.0    |  |  |

| Vetro trasparente | 0.3/0.4       | 6.4               | 2.5    | 3.6    |  |  |

| Vetro con maglia  | 0.3           | 7.7               | -      | 10.2   |  |  |

| Compensato        | 1.6           | -                 | 0.6    | -      |  |  |

| Legno             | 0.7           | 5.4               | 3.5    | -      |  |  |

| Malta             | 10            | -                 | 160    | -      |  |  |

| Mattone           | 10            | -                 | 178    | -      |  |  |

| Calcestruzzo      | 10            | 17.7              | 175    | -      |  |  |

Figura 3: Attenuazione tipica introdotta dai più comuni materiali edili.

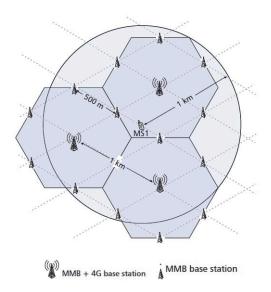

Per quanto detto finora, una rete MMB (*Millimeter-wave Mobile Broadband*) necessita di una densità elevata di stazioni base per coprire in maniera adeguata un'area geografica. Una disposizione possibile è quella di figura 4 dove un alto numero di nodi, ai quali un dispositivo mobile può collegarsi, sono posizionati in modo da formare una griglia, ad una distanza reciproca di 500m. Così facendo si risolve anche il problema della scarsa qualità di segnale ai bordi delle celle che caratterizza l'attuale sistema di comunicazione.

Come anticipato in precedenza, l'utilizzo di schiere di antenne rende possibile l'applicazione della tecnica del beamforming. Essa, attraverso un controllo sulla fase e l'ampiezza dell'onda, permette la trasmissione e la ricezione di segnali direttivi. Per far questo sfrutta le interferenze costruttive e distruttive combinandole in modo da ottenere il diagramma di radiazione voluto. Inoltre, sfruttando i fasci generati da diverse antenne, è possibile attuare lo spatial multiplexing (figura 5) e quindi focalizzare raggi trasmittenti differenti su utenti differenti realizzando lo spatial-division multiple access (SDMA). Come si può intuire, per rendere possibile la direzionalità selettiva della trasmissione, ogni antenna che partecipa al processo necessita di

Figura 4: Possibile disposizione di una rete MMB.

essere pilotata da un amplificatore dedicato. Di conseguenza il numero di PA utilizzati in un normale processo di comunicazione raggiunge valori elevati. Per questo motivo si rendono necessari dispositivi di amplificazione sempre più performanti, caratterizzati da bassi costi di produzione e da elevata efficienza così da ridurre al minimo i consumi. La progettazione e l'analisi di un amplificatore di potenza con le caratteristiche appena citate, che abbia una frequenza operativa nella banda delle onde millimetriche, è l'obiettivo di questa tesi.

Figura 5: Spatial multiplexing realizzato combinando 18 fasci provenienti da tre schiere di antenne.

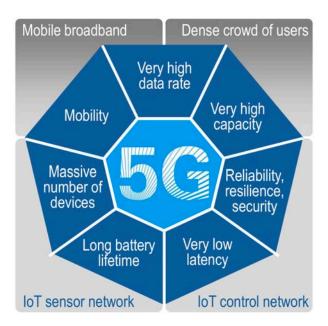

Allo scopo di regolamentare e fornire dei parametri utili per la ricerca e lo sviluppo dei futuri dispositivi in grado di supportare la prossima generazione di comunicazioni mobili, nello scorso Febbraio sono state emanate le linee guida dello standard che prende il nome di 5G. Questo si prefigge l'obiettivo di diventare il successore dell'attuale sistema 4G e prevede le seguenti caratteristiche [2]:

- velocità di picco di almeno 20 gigabit al secondo in download e almeno 10Gb/s in upload;

- velocità minima per ogni utente di 100Mb/s in download e 50Mb/s in upload;

- possibilità di supportare fino a un milione di dispositivi connessi per chilometro quadrato;

- latenza massima accettata di 4 millisecondi;

- consumo energetico ridotto e modalità di risparmio energetico attivabile per le celle non utilizzate;

- possibilità di supportare tutti i diversi tipi di dispositivi purché si muovano ad una velocità inferiore ai 500km/h.

Figura 6: Schema riassuntivo delle caratteristiche del 5G associate alle diverse applicazioni.

#### Stato dell'arte

In una rete MMB e più in generale nell'ambito delle onde millimetriche, un ruolo fondamentale è svolto dagli amplificatori di potenza che hanno il compito di pilotare le antenne. Devono infatti soddisfare determinate specifiche sia per quanto riguarda la linearità che per quanto concerne l'efficienza, senza perdere di vista il fattore economico. Si ricorda infatti che l'utilizzo di schiere di antenne comporta inevitabilmente l'impiego un gran numero di PA.

Sistemi di comunicazione basati sulle mm-wave già esistono per trasferire dati a distanze brevi, nell'ordine di qualche chilometro, ad una frequenza di funzionamento di 60GHz (ci si riferisce agli standard ECMA-387, IEEE 802.15.3c e IEEE 802.11ad). Questa situazione ha portato allo sviluppo di diverse soluzioni per PA in tecnologia CMOS, quindi dai costi contenuti e dimensioni scalate.

|      | Tecnologia | Struttura     | $ m V_{DD}$ | $P_{1dB}[dBm]$ | $P_{\rm sat}[{ m dBm}]$ | PAE   |

|------|------------|---------------|-------------|----------------|-------------------------|-------|

| [3]  | CMOS 65nm  | common source | 1.2V        | 13.5           | 15.6                    | 6.6%  |

| [4]  | CMOS 65nm  | common source | 1.2V        | 15.5           | 16.8                    | 14.5% |

| [5]  | CMOS 90nm  | common source | 1.2V        | 9              | 11                      | 6%    |

| [6]  | CMOS 65nm  | cascode       | 1.2V        | 11             | 16.6                    | 5%    |

| [7]  | CMOS 90nm  | cascode       | 1.2V        | 18             | 20                      | 14.2% |

| [8]  | CMOS 65nm  | c.s. diff.    | 1.2V        | 10             | 14.6                    | 16.3% |

| [9]  | CMOS 65nm  | cascode diff. | 1.2V        | 15.5           | 19.7                    | 25%   |

| [10] | CMOS 40nm  | common source | 1V          | 13.8           | 17                      | 30.3% |

Figura 7: Tabella comparativa per alcuni amplificatori CMOS a 60GHz.

Come si può vedere in figura 7 i nodi CMOS finora più utilizzati sono quelli da 65nm e 90nm, in configurazione a source comune o cascode. La prima permette di avere più swing di tensione d'uscita a parità di  $V_{DD}$ , mentre la seconda aumenta la stabilità del circuito. Il bias è tale da far operare gli amplificatori indicati in classe A e AB. Sono inoltre spesso adottati dei circuiti di preamplificazione tipicamente realizzati con struttura cascode, come in [5] e [8], e delle soluzioni di power combine come descritto in [7]. Degno di nota è [10] che utilizzando la più recente tecnologia CMOS a 40nm, caratterizzata da una frequenza di transizione maggiore e da minori parassiti, riesce a raggiungere un'efficienza superiore al 30%.

Per soperire alla richiesta di prestazioni sempre più spinte per gli integrati RF, sono state studiate ed introdotte nuove tecnologie. Si parla ad esempio dei processi BiCMOS silicio-germanio (SiGe BiCMOS) che permettono di raggiungere frequenze di transizione abbondantemente superiori al centinaio di GHz (la tecnologia BiC-

MOS9MW da 0.13u di ST è caratterizzata da  $f_T = 230GHz$ ) e combinano i vantaggi dei dispositivi bipolari con quelli dei MOS. Si trovano poi realizzazioni di PA che sfruttano gli High-Electron- $Mobility\ Transistor\ (HEMT)$  all'arsenuro di gallio i quali offrono un elevato guadagno. Nella tabella di figura 8 sono riportate delle realizzazioni di amplificatori di potenza che sfruttano le tecnologie appena citate.

|      | Tecnologia              | Classe | $ m V_{DD}$ | f[GHz] | $P_{1dB}[dBm]$ | PAE    |

|------|-------------------------|--------|-------------|--------|----------------|--------|

| [11] | GaAs pHEMT              | B-J    | 8V          | 8      | 27             | 60%    |

| [12] | SiGe BiCMOS $0.18\mu m$ | A      | 3.3V        | 5.5    | 22.39          | 17.42% |

| [13] | SiGe BiCMOS 120nm       | A      | _           | 30     | 16.58          | 11.47% |

| [14] | SiGe BiCMOS 120nm       | AB     | 2.5V        | 28     | 15.7           | 27.5%  |

Figura 8: Realizzazioni di PA per le onde millimetriche basati su dispositivi bipolari ed HEMT.

Con l'obiettivo di aumentare l'efficienza di un PA e ridurre quindi i costi legati ad un suo utilizzo, sono stati esplorati gli amplificatori *switching* che fanno parte delle classi di funzionamento E ed F. Queste promettono una massima efficienza teorica del 100%. Per una trattazione più dettagliata si rimanda al capitolo successivo. In figura 9 sono riportate le caratteristiche di alcuni PA realizzati in classe E o F.

|      | Tecnologia              | Classe   | $ m V_{DD}$ | f[GHz] | $P_{out}[dBm]$ | PAE   |

|------|-------------------------|----------|-------------|--------|----------------|-------|

| [15] | CMOS $65nm$             | E        | 2.5V        | 5      | 21.3           | 57%   |

| [16] | SiGe BiCMOS $0.13\mu m$ | E        | 2.7V        | 41     | 18.1           | 36%   |

| [17] | SOI CMOS 45nm           | E        | 1V          | 47     | 17.6           | 19.4% |

| [18] | SiGe BiCMOS $0.13\mu m$ | F        | 2.2         | 24     | 17             | 40.4% |

| [19] | CMOS $65nm$             | $E_3F_2$ | 2.5V        | 5      | 21             | 51%   |

Figura 9: Confronto tra PA in classe E ed F realizzati in diverse tecnologie.

Gli amplificatori switching hanno il difetto di essere fortemente non lineari. Nelle reti di comunicazione molto spesso sono utilizzati protocolli che richiedono un certo grado di linearità sia in ampiezza che in fase. Una classe di PA che sembra soddisfare sia i requisiti di linearità che di efficienza è la classe J. I dispositivi polarizzati per funzionare in questo modo combinano le caretteristiche delle classi A e B. Si tratta infatti di una modalità di funzionamento AB con una particolare condizione sul carico che ne aumenta le prestazioni. Nel corso di questa tesi verrà presentato un PA in classe J realizzato in tecnologia CMOS. Per offrire dei termini di paragone in

|      | Tecnologia       | Classe | $ m V_{DD}$ | f[GHz] | $P_{\rm sat}[dBm]$ | PAE   |

|------|------------------|--------|-------------|--------|--------------------|-------|

| [20] | CMOS $0.13\mu m$ | A      | 2V          | 24     | 12.5               | 30%   |

| [21] | CMOS $65nm$      | A      | 1.2V        | 58     | 13.8               | 7.6%  |

| [22] | SOI CMOS 45nm    | A-AB   | 5           | 14     | 25.1               | 32.5% |

| [23] | CMOS 28nm        | AB     | 1           | 28     | 14                 | 35.5% |

| [24] | CMOS 28nm        | AB     | _           | 28.5   | 14.8               | 36.5% |

Figura 10: Caratteristiche di alcuni amplificatori di potenza in classe A ed AB, in tecnologia CMOS.

|      | Tecnologia                      | $ m V_{DD}$ | f[GHz] | $P_{out}[dBm]$ | PAE   |

|------|---------------------------------|-------------|--------|----------------|-------|

| [25] | AlGaAs-InGaAs pHEMT $0.1 \mu m$ | 3.8V        | 5      | 27.8           | 62%   |

| [26] | AlGaAs-InGaAs pHEMT $0.25\mu m$ | 7V          | 6.5    | 30.7           | 44%   |

| [27] | GaAs pHEMT $0.1\mu m$           | 4V          | 10     | 26             | 46%   |

| [28] | GaN HEMT $0.8\mu m$             | 15V         | 2.6    | 27             | 50%   |

| [29] | SiGe BiCMOS 120nm               | 3.6V        | 28     | 15.5           | 31.5% |

| [30] | CMOS $0.18\mu m$                | 3.3V        | 1      | 12.2           | 43%   |

| [31] | CMOS $0.18\mu m$                | 3.3V        | 3.5    | 22             | 43.7% |

Figura 11: Stato dell'arte per gli amplificatori in classe J realizzati in diverse tecnologie.

figura 10 si riportano delle realizzazioni in tecnologia CMOS, mentre in figura 11 si mostrano le caratteristiche dei più recenti amplificatori in classe J.

Per quanto riguarda quest'ultima serie di PA, si può notare che con dispositivi come gli HEMT si riescono a raggiungere elevati valori di potenza ed efficienza senza compromettere la linearità ma con costi superiori rispetto alla più economica tecnologia CMOS. Le prestazioni più performanti degli HEMT sono in parte merito della capacità di sostenere una maggiore tensione, mentre la frequenza di transizione che li caratterizza dipende fortemente dal tipo di materiali che li compongono.

In seguito verrà dimensionato e simulato un amplificatore in classe J in tecnologia CMOS  $0.13\mu m$ . Questa, a differenza di [31] e [30], offre il vantaggio di una  $f_T$  più elevata che implica un maggiore guadagno, ma presenta una minore tensione di alimentazione possibile e quindi meno swing in uscita.

#### Contributo e struttura della tesi

Il lavoro di tesi svolto e qui presentato descrive il dimensionamento e le caratteristiche di un amplificatore di potenza per applicazioni RF, basato sulla tecnologia CMOS da  $0.13\mu m$ . Sono state prese come specifiche di progettazione una potenza di almeno 20dBm su un carico di  $50\Omega$  alla frequenza di 10GHz.

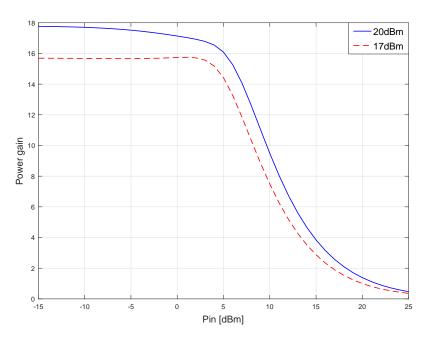

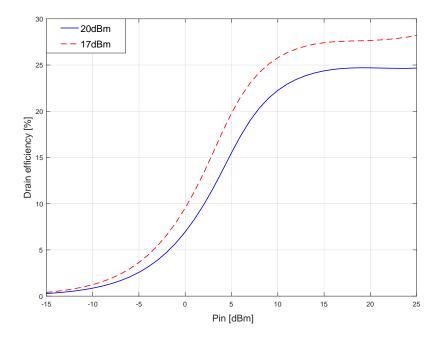

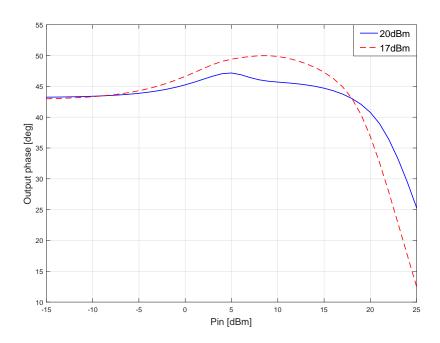

Dopo aver analizzato le condizioni legate al carico per permettere il funzionamento in classe J, vengono definite le linee guida per una corretta implementazione. Si passa poi a definire le dimensioni dei transistor in modo da renderli capaci di sopportare la corrente necessaria per rispettare le specifiche di potenza. È in seguito proposto un circuito di polarizzazione ed un arrangiamento per migliorare alcune caratteristiche di linearità del PA. Viene previsto anche un trasformatore in ingresso per permettere l'adattamento tra sorgente ed amplificatore. Vista l'importanza che il carico presenta al fine di avere un corretto funzionamento in classe J, è anche proposto un possibile layout per il trasformatore di uscita. I valori di induttanze e fattori di qualità del modello realizzato sono poi usati nelle simulazioni allo scopo di valutare il peso dei componenti parassiti nelle prestazioni del sistema. Infine è analizzato lo stesso circuito con un dimensionamento per una potenza di uscita pari a 17dBm. Anche per quest'ultimo viene proposta una realizzazione del trasformatore d'uscita.

Lo scopo di questo lavoro è non tanto quello di valutare le prestazioni della singola implementazione proposta, quanto fornire un punto di partenza per la realizzazione della classe J in tecnologia CMOS. Si è cercato quindi di valutare la reale possibilità di utilizzare dispositivi CMOS per questa classe di funzionamento. A tale scopo si sono cercate di raggiungere prestazioni paragonabili ad altri PA proposti in letteratura realizzati in tecnologie più performanti ma dal costo maggiore.

La struttura dell'elaborato presenta tre sezioni principali:

- 1. un primo capitolo dove vengono forniti i fondamenti teorici che sono risultati utili nello svolgimento del lavoro di tesi;

- un secondo capitolo che presenta l'analisi teorica ed il dimensionamento del PA;

- 3. un terzo capitolo che mostra ed analizza i risultati ottenuti dal circuito realizzato.

Un ultimo capitolo trae le conclusioni del lavoro svolto fornendo alcuni sviluppi futuri per questo ambito di ricerca.

## Capitolo 1

## Richiami teorici

#### 1.1 Serie di Fourier

La serie di Fourier permette di riscrivere particolari funzioni dotate di alcune caratteristiche sottoforma di serie trigonometrica. In seguito verrà fornita una definizione priva di alcuni rigori matematici ma sufficiente per comprendere la trattazione che sarà fatta nei prossimi paragrafi riguardante l'amplificatore in classe J.

Si consideri una funzione  $f: \mathbb{R} \to \mathbb{C}$  periodica di periodo  $2\pi$ , dove tale periodicità viene scelta come caso specifico per le applicazioni che interessano in questa tesi, continua ed integrabile su  $(-\pi, \pi)$ . I numeri

$$\begin{cases} a_n = \frac{1}{\pi} \int_{-\pi}^{\pi} f(x) \cos(nx) dx & \text{con } (n = 0, 1, 2, ...) \\ b_n = \frac{1}{\pi} \int_{-\pi}^{\pi} f(x) \sin(nx) dx & \text{con } (n = 0, 1, 2, ...) \end{cases}$$

(1.1)

si dicono coefficienti di Fourier di f e la serie

$$S_f(x) = \frac{1}{2}a_0 + \sum_{n=1}^{+\infty} (a_n cos(nx) + b_n sin(nx))$$

(1.2)

che utilizza (1.1) si dice serie di Fourier associata ad f. Sotto alcune condizioni di regolarità di f (ad esempio  $f \in C^1(\mathbb{R})$  può bastare) si può dimostrare che  $S_f(x)$ converge uniformemente a f(x) e quindi

$$f(x) = \frac{1}{2}a_0 + \sum_{n=1}^{+\infty} (a_n \cos(nx) + b_n \sin(nx))$$

(1.3)

con  $a_n$  e  $b_n$  dati da (1.1).

Alcune situazioni particolari possono semplificare il calcolo dei coefficienti della serie di Fourier. Una funzione f(x) si dice pari o dispari se verifica rispettivamente:

$$f$$

pari  $\iff f(-x) = f(x) \qquad \forall x \in \mathbb{R}, \qquad (1.4)$

$f$  dispari  $\iff f(-x) = -f(x) \qquad \forall x \in \mathbb{R}. \qquad (1.5)$

$$f$$

dispari  $\iff f(-x) = -f(x) \quad \forall x \in \mathbb{R}.$  (1.5)

In questi due casi la (1.3) si riduce a:

$$f \text{ pari}$$

$\iff$   $f(x) = \frac{a_0}{2} + \sum_{n=1}^{+\infty} a_n cos(nx)$   $\forall x \in \mathbb{R},$  (1.6)

$$f \text{ dispari} \qquad \iff \qquad f(x) = \sum_{n=1}^{+\infty} b_n \sin(nx) \qquad \forall x \in \mathbb{R}.$$

(1.7)

sempre con  $a_n$  e  $b_n$  calcolati come indicato in (1.1).

## 1.2 Figure di merito

Nella caratterizzazione degli amplificatori di potenza diverse figure di merito sono usate per esprimere caratteristiche legate alla potenza e all'efficienza del dispositivo. In particolare, nel corso di questa tesi, si farà riferimento al "guadagno" (inteso come operating power gain), all'efficienza di drain e alla PAE (Power Added Efficiency). Sarà infine preso in considerazione anche il 1dB-compression point.

**Guadagno** Con questo termine si fa riferimento, come specificato prima, all'*operating* power gain, ovvero il rapporto tra potenza consegnata al carico  $(P_L)$  e potenza fornita in ingresso all'amplificatore  $(P_{in})$ :

$$G_P = \frac{P_L}{P_{in}}. (1.8)$$

Efficienza di drain Con questo parametro si danno indicazioni su quanto efficacemente il PA riesce a convertire la potenza DC fornita dall'alimentazione  $(P_{DC})$  in potenza consegnata al carico alla frequenza fondamentale  $(P_{rf})$ . È indicata con  $\eta$  e si calcola con il rapporto:

$$\eta = \frac{P_{rf}}{P_{DC}}. (1.9)$$

Power Added Efficiency Per considerare il fatto che un amplificatore assorbe potenza anche dal circuito che lo pilota e non solo dalla rete di alimentazione, si fa riferimento alla PAE. Questa figura di merito infatti tiene conto anche della potenza di ingresso a radiofrequenza  $(P_{in})$  ed è definita come:

$$PAE = \frac{P_L - P_{in}}{P_{DC}} = \eta (1 - \frac{1}{G_P}). \tag{1.10}$$

1dB-compression point Si immagini di dare in ingresso al PA una forma d'onda ideale del tipo

$$V_{in} = A_{in}cos(wt). (1.11)$$

Andando a scrivere la funzione di trasferimento del PA come una serie di potenze

$$V_o(t) = a_0 + a_1 V_{in}(t) + a_2 V_{in}^2(t) + a_3 V_{in}^3(t) + \dots$$

(1.12)

se si applicano le proprietà di seno e coseno quello che si ottiene è un'espressione di  $V_o(t)$  che mostra gli effetti della distorsione armonica. In particolare diventa ben visibile come una distorsione di ordine pari genera un contributo a DC e in tutti gli ordini pari inferiori, mentre una distorsione di ordine dispari si ripresenta in tutti gli ordini dispari di grado inferiore, compresa la frequenza fondamentale, dando origine al fenomeno di gain compression. Limitandosi all'ordine 3, per la componente fondamentale della tensione di uscita si ottiene:

$$V_{o,1}(t) = \left[ a_1 A_{in} + \frac{3a_3 A_{in}^3}{4} \right] cos(wt)$$

(1.13)

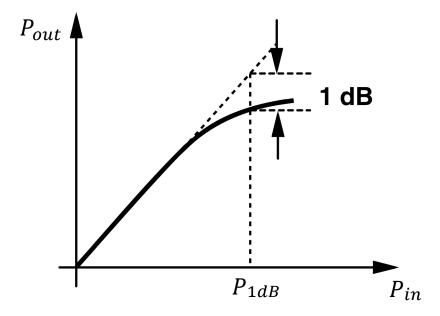

dove tipicamente  $a_3 < 0$ . Per segnali di ingresso con ampiezza limitata la compressione risulta trascurabile ma aumentando  $A_{in}$  questo non è più vero finché non si arriva ad avere che i coefficienti dispari di ordine superiore al primo diventano dominanti. Quando questo accade il PA satura e il guadagno crolla, producendo segnali distorti. Il 1dB-compression point  $(P_{1dB})$  è definito come il valore della potenza di ingresso per cui il guadagno è diminuito di 1dB rispetto al valore ideale calcolato alla  $P_{in}$  minima (figura 1.1).

Figura 1.1: Misura grafica di 1dB compression point.

### 1.3 Parametri di scattering

Un sistema può essere caratterizzato in molti modi, facendo riferimento a grandezze e figure di merito diverse. Alle basse frequenze la rappresentazione più diffusa fa uso di impedenze, di ammettenze, o di entrambe (modello ibrido). Si possono così definire, ad esempio con le impedenze, delle espressioni per la tensione all'ingresso delle porte in funzione della corrente [32]:

$$\begin{cases}

V_1 = Z_{11}I_1 + Z_{12}I_2, \\

V_2 = Z_{21}I_1 + Z_{22}I_2.

\end{cases}$$

(1.14)

Alle microonde risulta invece più comodo riferirsi a quantità legate alla potenza, questo essenzialmente per due motivi:

- la misura ad alta frequenza di tensioni e correnti può risultare molto difficoltosa a causa dei problemi nel realizzare cortocircuiti o circuiti aperti per misurare, ad esempio, i parametri Z di (1.14);

- il design di circuiti RF è basato sostanzialmente sul trasferimento di potenza, quindi molte specifiche sono appunto fissate in termini di potenza.

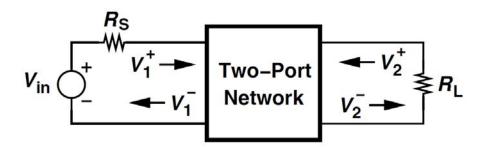

Figura 1.2: Indicazione delle onde incidenti e riflesse in un doppio bipolo generico con generatore di ingresso  $V_{in}$  e carico  $R_L$ .

In questo ambito vengono perciò usati i parametri di scattering, o parametri S, definiti come segue. Facendo riferimento ad una rete generica caratterizzata dal doppio bipolo di figura 1.2, si identificano l'onda incidente e riflessa alla porta di ingresso rispettivamente con  $V_1^+$  e  $V_1^-$ , mentre per la porta d'uscita si hanno  $V_2^+$  e  $V_2^-$ . In altre parole  $V_1^+$  è definita come l'onda generata da  $V_{in}$  e nel caso in cui l'impedenza d'ingresso del doppio bipolo fosse diversa da  $R_s$  è necessario considerare anche l'onda riflessa  $V_1^-$  che si genera. Alla porta 2 si ha che  $V_2^+$  può essere vista sia come l'onda incidente all'ingresso della porta, sia come l'onda riflessa dal carico  $R_L$ . Queste quattro grandezze sono legate tra loro dai parametri S della rete:

$$\begin{cases}

V_1^- = S_{11}V_1^+ + S_{12}V_2^+, \\

V_2^- = S_{21}V_1^+ + S_{22}V_2^+.

\end{cases}$$

(1.15)

I coefficienti di (1.15) possono essere descritti e calcolati come segue:

$S_{11}$  è il rapporto tra l'onda riflessa e l'onda incidente alla porta di input quando la riflessione dal carico è nulla. Rappresenta la bontà dell'accoppiamento in ingresso.

$$S_{11} = \frac{V_1^-}{V_1^+} \bigg|_{V_2^+ = 0}. (1.16)$$

$S_{12}$  è il rapporto tra onda riflessa alla porta 1 e onda incidente alla porta 2 con un adattamento perfetto in ingresso e segnale  $V_{in}$  nullo  $(V_1^+ = 0)$ . Rappresenta quanto il segnale d'uscita contribuisce all'onda riflessa  $V_1^-$ .

$$S_{12} = \frac{V_1^-}{V_2^+} \bigg|_{V_1^+ = 0}. (1.17)$$

$S_{22}$  è il rapporto tra onda riflessa e onda incidente alla porta d'uscita quando la riflessione da  $R_S$  è nulla. Rappresenta la qualità dell'output matching.

$$S_{22} = \frac{V_2^-}{V_2^+} \bigg|_{V_1^+ = 0}. (1.18)$$

$S_{21}$  è il rapporto tra l'onda incidente sul carico e l'onda incidente alla porta 1 quando la riflessione da  $R_L$  è nulla. Rappresenta il guadagno del circuito.

$$S_{21} = \frac{V_2^-}{V_1^+} \bigg|_{V_2^+ = 0}. (1.19)$$

I parametri appena definiti presentano solitamente valori complessi dipendenti dalla frequenza. Possono inoltre essere espressi in decibel calcolando:

$$S_{mn}|_{dB} = 20log|S_{mn}|. (1.20)$$

#### 1.4 AM-PM conversion

Con il termine AM-PM conversion si indica di quanto varia la fase del segnale di uscita (PM) in seguito ad una variazione di ampiezza del segnale di ingresso (AM). In un amplificatore ideale non è presente interazione tra la sua fase di uscita ed il livello di potenza dell'ingresso. Nella realtà però questo avviene, soprattutto in PA realizzati con moderni processi CMOS i quali sono caratterizzati da un'ampia distorsione AM-PM dovuta alla forte non linearità delle capacità parassite (in particolare della capacità  $C_{qs}$  del MOSFET).

Il parametro AM-PM conversion è molto importante e può diventare critico in tutti quei sistemi di trasmissione che utilizzano la modulazione di fase, come:

- FM;

- QPSK;

- QAM.

In questi casi una variazione di fase indesiderata comporta un aumento del tasso di errore dei bit (BER), cioè peggiora il rapporto tra i bit ricevuti correttamente e i bit inviati, cosa ben visibile in figura 1.3. Un elevato BER è sinonimo di un sistema di comunicazione di scarsa qualità. È importante quindi cercare di ridurre l'AM-PM conversion durante la fase di progettazione del PA. In seguito verrà descritto ed implementato un modo per migliorare questo parametro.

Figura 1.3: Bit error causato da AM-PM conversion.

### 1.5 Classi di funzionamento per PA

Un amplificatore a radio frequenze è un tipo di amplificatore che converte un segnale RF di potenza limitata in un segnale a potenza maggiore. Tipicamente sono usati nei sistemi di comunicazione per pilotare antenne e trasmettitori. In queste applicazioni spesso gli obiettivi sono differenti e in fase di progettazione si pone la priorità a volte sulla larghezza di banda, altre sulla potenza di uscita e altre ancora sulla linearità. Non meno frequentemente si cerca un compromesso tra i diversi parametri che caratterizzano il PA. Allo scopo di rispettare le diverse specifiche che deve soddisfare, un amplificatore può operare in diversi modi, chiamati classi di funzionamento, cha saranno a breve descritti.

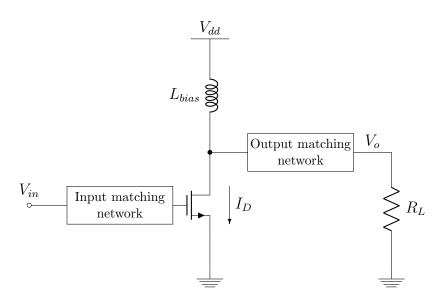

Figura 1.4: Schema generale di un amplificatore di potenza RF.

Solitamente ognuna di queste classi può essere ricondotta allo schema generico mostrato in figura 1.4. Qui è visibile un transistor n-MOS che si comporta da driver, connesso all'alimentazione tramite un induttore  $(L_{bias})$  assimilabile, in DC, ad un cortocircuito in modo da permettere la polarizzazione. Con  $R_L$  si indica il carico al quale il PA deve fornire potenza, ed è separato dal core dell'amplificatore da una rete di matching che ha il duplice scopo di filtrare le armoniche indesiderate e realizzare un adattamento. In alcune classi questa rete è usata anche per caricare il transistor con una particolare impedenza tale da migliorare l'efficienza del dispositivo. È presente poi una rete di matching in ingresso che serve essenzialmente per eseguire un adattamento di impedenza tra la sorgente ed il driver, riuscendo in certi casi ad aggiungere un piccolo guadagno al sistema.

#### 1.5.1 Classe A

Un amplificatore lineare produce un segnale di uscita che è esattamente una versione scalata del segnale di ingresso. In altre parole il guadagno che introduce è costante ed indipendente dall'ampiezza dell'input. La classe più semplice che ha un comportamento di questo tipo è la classe A.

Un PA che opera in classe A è polarizzato con una tensione di overdrive sufficientemente ampia in modo da evitare che il transistor si spenga. Inoltre si deve impedire che il MOSFET entri nella regione di triodo, o rispettivamente che il BJT vada in saturazione, per non introdurre non linearità. Un altro modo di indicare questo funzionamento è attraverso l'angolo di conduzione che assume il valore di 360°, ciò sta a significare che il transistor conduce per l'intero ciclo del segnale d'ingresso.

Lo swing di tensione massimo che si riesce ad ottenere è  $(V_{dd} - V_{ov})$ , infatti la presenza dell'induttore permette alla tensione di drain di oscillare simmetricamente attorno a  $V_{dd}$  così da garantire una tensione DC nulla ai capi di  $L_{bias}$ . Lo swing di corrente dipende invece dalla  $I_{bias}$  settata tipicamente a metà della corrente massima che il transistor può gestire, in questo modo si ha  $I_{sw} = I_{bias}$ . Di conseguenza la potenza massima ottenibile è

$$P_{out}^{A} = \frac{1}{2} V_{sw} I_{sw} = \frac{1}{2} (V_{dd} - V_{ov}) \frac{I_{max}}{2}.$$

(1.21)

sotto la condizione di avere un'appropriata impedenza di carico pari a

$$R_{opt}^{A} = 2\frac{V_{dd} - V_{ov}}{I_{max}}. (1.22)$$

Inoltre, in questa situazione, la massima efficienza di drain che un classe A può realizzare è:

$$\eta_D^A = \frac{P_{out}^A}{P_{DC}} = \frac{\frac{(V_{dd} - V_{ov})I_{max}}{4}}{\frac{V_{dd}I_{max}}{2}} = \frac{V_{dd} - V_{ov}}{2V_{dd}} \approx 50\%.$$

(1.23)

Figura 1.5: Schema e forme d'onda V-I di un amplificatore di potenza in classe A.

#### 1.5.2 Classe B

Un transistor dissipa potenza in corrispondenza di una sovrapposizione tra tensione e corrente entrambe non nulle. Per aumentare l'efficienza si può quindi cercare di ridurre questa sovrapposizione. Quello che viene fatto in un amplificatore in classe B è proprio questo, nello specifico si utilizza una tensione di bias pari alla tensione di soglia così da far condurre il transistor solo per metà periodo (figura 1.6). La corrente che si ottiene può quindi essere espressa da

$$i_D(t) = \begin{cases} I_{max}cos(w_0t) & \text{se } i_D > 0; \\ 0 & \text{altrimenti} \end{cases}$$

(1.24)

ed è caratterizzata da una componente fondamentale di ampiezza  $\frac{I_{max}}{2}$  ed un valore DC pari a  $\frac{I_{max}}{\pi}$ .

La potenza di uscita con il relativo valore ottimale del carico e l'efficienza massima possono essere calcolate come segue:

$$P_{out}^{B} = \frac{1}{2} V_{sw} I_{sw} = \frac{1}{4} (V_{dd} - V_{ov}) I_{max}$$

(1.25)

$$R_{opt}^B = 2\frac{V_{vv} - V_{ov}}{I_{max}} \tag{1.26}$$

$$\eta_D^B = \frac{P_{out}^B}{P_{DC}} = \frac{\frac{(V_{dd} - V_{ov})I_{max}}{4}}{\frac{\pi}{V_{dd}I_{max}}} = \frac{\pi(V_{dd} - V_{ov})}{4V_{dd}} \approx 78.5\%$$

(1.27)

Solitamente gli amplificatori in classe B sono progettati secondo una topologia push-pull a due transistor. In questo modo un dispositivo è attivo durante la semionda positiva mentre l'altro durante la semionda negativa del segnale di ingresso e quest'ultimo può essere interamente amplificato.

Figura 1.6: Schema e forme d'onda V-I di un amplificatore di potenza in classe B.

#### 1.5.3 Classe AB

Per incrementare la linearità di un amplificatore in classe B, la tensione di bias al gate del transistor può essere aumentata in modo da renderla maggiore della tensione di soglia e non più uguale. Così facendo il driver conduce per più di metà periodo e l'efficienza di conseguenza ne risente restando comunque maggiore di quella che caratterizza un classe A. Un tale compromesso risulta in molti casi soddisfacente e questa modalità di funzionamento, che prende il nome di classe AB, è spesso la scelta più utilizzata.

Per trovare le espressioni di potenza ed efficienza massima bisogna prima scrivere lo swing di corrente  $(I_{sw})$  e la componente DC  $(I_{DC})$  in funzione dell'angolo di conduzione  $\alpha$ , definito come il numero di radianti in un periodo durante i quali il core dell'amplificatore conduce corrente. Si ha [33]:

$$I_{sw} = \frac{1}{2\pi} \left[ \frac{\alpha - \sin(\alpha)}{1 - \cos(\frac{\alpha}{2})} \right] I_{max}$$

(1.28)

$$I_{DC} = \frac{1}{2\pi} \left[ \frac{2\sin(\frac{\alpha}{2}) - \alpha\cos(\frac{\alpha}{2})}{1 - \cos(\frac{\alpha}{2})} \right]. \tag{1.29}$$

Di conseguenza la potenza in uscita, il carico ottimo e l'efficienza di drain risultano:

$$P_{out}^{AB} = \frac{1}{4\pi} \left[ \frac{\alpha - \sin(\alpha)}{1 - \cos(\frac{\alpha}{2})} \right] (V_{dd} - V_{ov}) I_{max}$$

(1.30)

$$R_{opt}^{AB} = 2\pi \left[ \frac{1 - \cos(\frac{\alpha}{2})}{\alpha - \sin(\alpha)} \right] \frac{V_{dd} - V_{ov}}{I_{max}}$$

(1.31)

$$\eta_D^{AB} = \frac{P_{out}^{AB}}{P_{DC}} = \frac{1}{2} \frac{V_{dd} - V_{ov}}{V_{dd}} \frac{\alpha - \sin(\alpha)}{2\sin(\frac{\alpha}{2}) - \alpha\cos(\frac{\alpha}{2})}$$

(1.32)

dove, per tutte le espressioni riguardanti il classe AB si considera  $\alpha \in [\pi, 2\pi]$  e i due estremi corrispondono rispettivamente al funzionamento in classe B per  $\alpha = \pi$  e al funzionamento in classe A per  $\alpha = 2\pi$ .

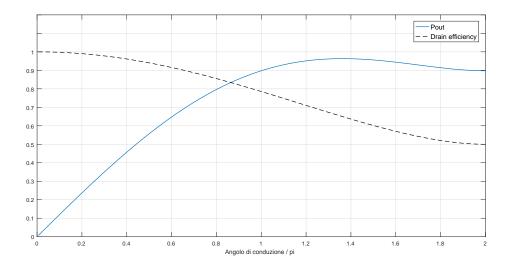

#### 1.5.4 Classe C

Se si polarizza un PA con una tensione al gate del transistor inferiore alla tensione di soglia, quello che si ottiene è un funzionamento in *classe C*. Questo tipo di amplificatori sono non lineari quindi non adatti ad essere utilizzati in sistemi di comunicazione basati sulla modulazione di ampiezza, ma possono essere impiegati in reti che sfruttano la modulazione di fase purché abbiano una bassa distorsione phase-to-phase.

Un PA in classe C conduce per meno di metà periodo per questo presenta una ridotta sovrapposizione di tensione e corrente non nulle ed una conseguente efficienza di drain molto elevata, che tende teoricamente al 100%. Al diminuire dell'angolo di conduzione però, il transistor, essendo acceso per meno tempo, riesce a trasferire al carico una quantità inferiore di potenza, che tende a 0 quando l'efficienza è massima. Le formule per  $P_{out}^C$ ,  $R_{opt}^C$  e  $\eta_D^C$  sono le stesse del classe AB, (1.30)-(1.32), con una differenza per quanto riguarda l'intervallo di definizione di  $\alpha$  che risulta  $\alpha \in [0, \pi]$ . Dalle equazioni (1.30) e (1.32) si può notare come la potenza e l'efficienza siano proporzionali a due diversi fattori dipendenti da  $\alpha$ , in particolare si ha

$$P_{out} \propto \frac{\alpha - sin(\alpha)}{1 - cos(\frac{\alpha}{2})}$$

;  $\eta_D \propto \frac{\alpha - sin(\alpha)}{sin(\frac{\alpha}{2}) - \frac{\alpha}{2}cos(\frac{\alpha}{2})}$  (1.33)

che una volta graficati (figura 1.7) mostrano quanto detto precedentemente a proposito del caso in cui  $\alpha=0$ . Inoltre sono individuabili i valori relativi ai casi limite di classe A e B rispettivamente per  $\frac{\alpha}{\pi}=2$  e  $\frac{\alpha}{\pi}=1$ .

Figura 1.7: Andamento di efficienza di drain e potenza di uscita al variare di  $\alpha$ .

Figura 1.8: Schema e forme d'onda V-I di un amplificatore di potenza in classe C.

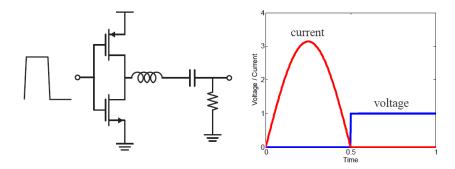

#### 1.5.5 Classe D

Un PA in classe D fa parte della famiglia degli amplificatori switching nei quali i transistor si comportano da interruttori e funzionano o in regione di triodo o in cut-off. Solitamente è adottata una topologia push-pull caricata con un filtro LC in modo da permettere solo alla componente fondamentale di raggiungere il carico (figura 1.9). Uno switch ideale quando è aperto presenta corrente nulla e tensione diversa da zero, mentre quando è chiuso si ha la situazione opposta. In questo modo la sovrapposizione tra corrente e tensione non nulle è idealmente assente portando l'efficienza di drain teorica verso il 100%. Un tale valore non è però in pratica realizzabile a causa dei componenti parassiti e al tempo non nullo di commutazione dei transistor. Inoltre l'efficienza di picco può essere raggiunta solo a basse frequenze dove le capacità associate al nodo di drain sono trascurabili, infatti la potenza spesa per caricare queste capacità cresce con la frequenza. Un altro effetto introdotto dalle  $C_{par}$  è quello di ridurre la pendenza dei fronti di commutazione introducendo sovrapposizioni V-I [33].

Figura 1.9: Schema e forme d'onda V-I di un amplificatore di potenza in classe D.

#### 1.5.6 Classe E

Per mitigare i problemi del classe D dovuti ai componenti parassiti, che si presentano maggiormente durante le commutazioni dei dispositivi, è stata introdotta la classe E. I transistor lavorano sempre come interruttori ed è previsto di assorbire le capacità parassite in una opportuna rete [34] in modo da imporre alla tensione di uscita due caratteristiche:

- raggiunge lo zero prima che lo switch sia chiuso, quindi prima che inizi a scorrere corrente, per poi restare nulla finché il transistor conduce;

- la sua derivata nell'istante in cui lo switch si accende è zero.

Queste due proprietà permettono di ridurre sia la sensibilità dell'efficienza alle variazioni parametriche, che la potenza dissipata portando l'efficienza di drain prossima

al 100%. Un problema di questa classe di funzionamento è l'elevata tensione al drain del transistor che aumenta lo stress del dispositivo e impedisce di realizzare un classe E in tecnologie particolarmente scalate [32].

Figura 1.10: Schema e forme d'onda V-I di un amplificatore di potenza in classe E.

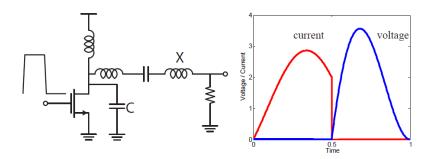

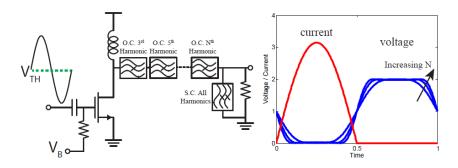

#### 1.5.7 Classe F

Se si combina il singolo switch di un classe C con l'approccio ad onda quadra di tensione del classe D, quello che si ottiene è il funzionamento in classe F [35]. In alternativa si può vedere questo tipo di amplificatori come il tentativo di migliorare l'efficienza massima di un classe B senza sacrificare la potenza di uscita [33]. L'idea è quella di aggiungere armoniche di ordine dispari alla forma d'onda della tensione di uscita, trasformando quest'ultima da una sinusoide ad un'onda quadra, riducendo così l'overlap tra tensione e corrente. Aumentando il numero di armoniche si tende ad una efficienza massima del 100%. A livello circuitale quello che si fa è inserire in serie all'uscita del PA un banco di filtri che si comportano come cortocircuito per le armoniche dispari, mentre si aggiunge un filtro passa basso per eliminare tutte le armoniche di ordine pari (1.11). Come per il classe D, l'efficienza è spesso degradata dalla presenza di capacità parassita al nodo di drain e dalle perdite causate dalla serie di filtri. Oltre la terza armonica l'aumento di prestazioni ottenuto aggiungendo un ulteriore filtro viene spesso cancellato dai parassiti introdotti.

Figura 1.11: Schema e forme d'onda V-I di un amplificatore di potenza in classe F.

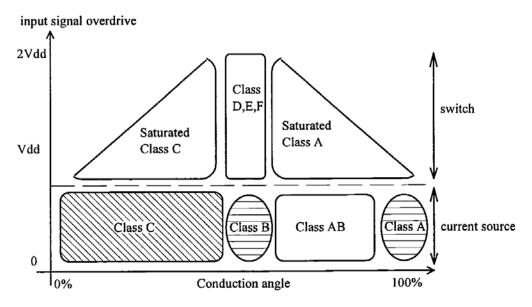

Le classi di funzionamento per un amplificatore di potenza RF viste finora si possono distinguere in base all'angolo di conduzione e all'ampiezza del segnale di ingresso, come mostrato nel grafico di figura 1.12 [35]. L'angolo  $\alpha$  è legato al bias DC che viene imposto al transistor, mentre l'efficienza può essere migliorata in due modi:

- 1. riducendo l'angolo di conduzione, finendo quindi nella classe C, a discapito della potenza di uscita;

- 2. aumentando la tensione di ingresso e forzando il PA a lavorare come switch, tenendo fisso  $\alpha$ .

Figura 1.12: Definizioni delle classi di funzionamento di un PA basate sull'angolo di conduzione e sul segnale di ingresso.

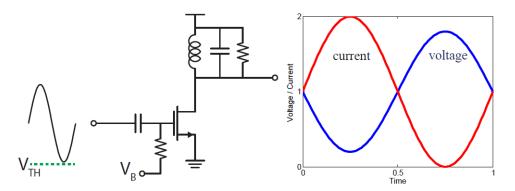

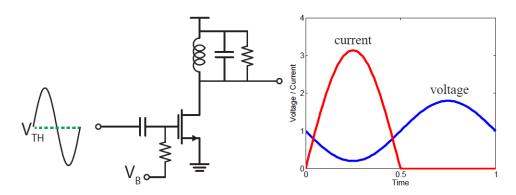

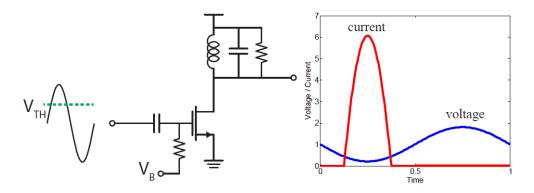

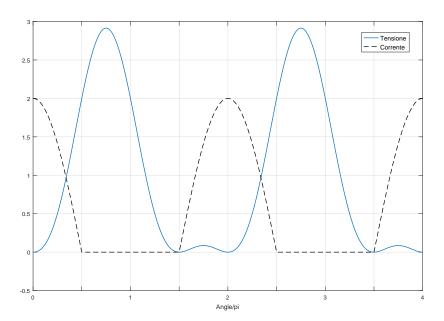

#### 1.5.8 Classe J

A differenza di altre classi di amplificatori dove si cerca di presentare al PA un carico puramente resistivo alla prima armonica e assimilabile ad un corto circuito alle armoniche superiori, nel classe J si va ad utilizzare proprio il carico per realizzare una particolare impedenza sia alla prima che alla seconda armonica. Queste impedenze sono tali da sfruttare i componenti parassiti presenti al drain del transistor in modo da creare delle forme d'onda di tensione e corrente sovrapposte solo per un intervallo ridotto (figura 1.13). Così facendo si riesce a diminuire la potenza media dissipata, ottenendo un'efficienza elevata.

A causa della non linearità ai grandi segnali dei componenti parassiti che interagiscono con il carico, risulta difficile stabilire analiticamente un valore univoco da

Figura 1.13: Forme d'onda di tensione e corrente ideali al drain del transistor mosfet per un amplificatore in classe J.

attribuire a quest'ultimo. Inoltre va considerato che l'impedenza cambia significativamente con il variare della frequenza e questo risulta problematico se si vuole mantenere un certo funzionamento in una larga banda.

Allo scopo di determinare l'impedenza di carico, la procedura più attuabile è quella di andare ad analizzare le forme d'onda di tensione e corrente ai capi del transistor imponendo gli andamenti voluti alle diverse armoniche e andando a ricavare i valori di impedenza necessari per massimizzare l'efficienza. Considerando un generico amplificatore di potenza, l'andamento di figura 1.13 della corrente al drain del transistor può essere espresso analiticamente come:

$$i_D(t) = \begin{cases} i_{rf}cos(w_0 t) & \text{se } i_D > 0, \\ 0 & \text{altrimenti.} \end{cases}$$

(1.34)

Inoltre, posto  $\theta = wt$ , si possono esprimere tensione e corrente generiche mediante le serie di Fourier:

$$V(\theta) = V_{DC} + \sum_{n=1}^{N} [V_{nr}cos(n\theta) + V_{nq}sin(n\theta)], \qquad (1.35)$$

$$I(\theta) = I_{DC} + \sum_{n=1}^{N} [I_{nr}cos(n\theta) + I_{nq}sin(n\theta)].$$

(1.36)

È conveniente poi normalizzare i coefficienti relativi all'ampiezza delle diverse armoniche relativamente al valore di riposo

$$v_{nr} = \frac{V_{nr}}{V_{DC}} \qquad i_{nr} = \frac{I_{nr}}{I_{DC}}$$

(1.37)

$$v_{nq} = \frac{V_{nq}}{V_{DC}} \qquad i_{nq} = \frac{I_{nq}}{I_{DC}}$$

(1.38)

in modo da avere

$$v(\theta) = 1 + \sum_{n=1}^{N} [v_{nr}cos(n\theta) + v_{nq}sin(n\theta)], \qquad (1.39)$$

$$i(\theta) = 1 + \sum_{n=1}^{N} [i_{nr}cos(n\theta) + i_{nq}sin(n\theta)]. \tag{1.40}$$

Sul carico si vuole sia presente solo potenza attiva legata alla fondamentale, e viste le frequenze in gioco si può considerare l'impedenza vista dal transistor come un cortocircuito per tutte le armoniche superiori alla seconda. Arrestando quindi le equazioni (1.39) e (1.40) ad n=2 si ottiene:

$$v(\theta) = 1 + v_{1r}\cos(\theta) + v_{1q}\sin(\theta) + v_{2r}\cos(2\theta) + v_{2q}\sin(2\theta), \tag{1.41}$$

$$i(\theta) = \frac{1}{\pi} + \frac{1}{2}cos(\theta) + \frac{2}{3\pi}cos(2\theta).$$

(1.42)

Per quanto riguarda la tensione, (1.41) deve rispettare la condizione

$$v(\theta) \ge 0 \tag{1.43}$$

allo scopo di mantenere un comportamento lineare. In particolare è interessante il caso il cui  $v(\theta)$  sfiora lo zero, che si traduce nei vincoli:

$$v(\theta) = 0, \qquad v'(\theta) = 0.$$

(1.44)

Secondo quanto proposto da Cripps [36], il quale si basa su precedenti lavori di Rhodes [37] e Raab [38], la forma d'onda di tensione del classe J può essere scritta nella forma

$$v_J(\theta) = 1 - \cos(\theta) - \sin(\theta) + \frac{1}{2}\sin(2\theta)$$

(1.45)

che, una volta fattorizzata, corrisponde a

$$v_J(\theta) = (1 - \cos(\theta))(1 - \sin(\theta)).$$

(1.46)

È facilmente verificabile che (1.46) soddisfa le condizioni (1.44) per  $\theta = 0$ . Da questa osservazione segue quindi che esiste una famiglia di espressioni, le quali verificano (1.44), esprimibili come:

$$v(\theta) = (1 - \beta \cos(\theta))(1 - \alpha \sin(\theta)) \tag{1.47}$$

per  $(-1 \le \alpha \le 1)$  e  $(0 < \beta < 1)$ . Lo standard della classe B per quanto riguarda l'efficienza è mantenuto per  $\beta = 1$ , infatti  $\beta$  è legato al coefficiente  $v_{1r}$  ovvero all'ampiezza della parte reale della tensione sul carico. Scegliendo questo valore si va anche a massimizzare la potenza trasmessa in uscita. Il parametro  $\alpha$  invece varia l'ampiezza della parte reattiva alla prima e alla seconda armonica. La classe J corrisponde ad  $\alpha = 1$ , mentre si definisce anche la classe J\* per  $\alpha = -1$ . La classe B convenzionale si ottiene con  $\alpha = 0$  [39].

I vincoli finora trovati per garantire il funzionamento in classe J portano a dei particolari valori che il carico deve assumere alla prima e alla seconda armonica. Considerando le trasformate di Fourier, per  $\alpha = \beta = 1$  si ricava:

$$Z_1 = \frac{V_1}{I_1} = (1+j)\frac{2V_{DC}}{I_{DC}} = (1+j)R,$$

(1.48)

$$Z_2 = \frac{V_2}{I_2} = -j\frac{3\pi}{4}\frac{V_{DC}}{I_{DC}} = -j\frac{3\pi}{8}R. \tag{1.49}$$

Questi valori devono teoricamente essere mantenuti per tutta la banda di funzionamento del PA, ma questo non è possibile perchè l'impedenza varia con la frequenza. In [40] è proposto un metodo che permette di aggirare il problema basato sui contorni di clipping: questi permettono di individuare, data un'impedenza alla fondamenta-le  $(Z_1)$ , una famiglia di impedenze alla seconda armonica  $(Z_2)$  che garantiscono il funzionamento in classe J, seppure con un'efficienza ridotta. Si ottiene così una regione della carta di Smith il cui interno identifica dei valori di  $Z_2$  tali da permettere alla forma d'onda di tensione di restare sempre positiva in modo da evitare lo spegnimento del transistor e quindi forti non linearità. I contorni di clipping vengono calcolati introducendo a (1.47) dei gradi di libertà:

$$v(\theta) = (1 - \cos(\theta + \delta))(1 - \alpha\sin(\theta + \gamma)) \tag{1.50}$$

con  $\beta = 1$ ,  $(-1 \le \alpha \le 1)$  e  $(0 \le \delta, \gamma < 2\pi)$ . Questo porta (1.50) ad avere le seguenti caratteristiche:

- 1. gli sfasamenti  $\delta$  e  $\gamma$  permettono ai termini in seno e coseno di avere sia parte reale che immaginaria. Tramite la sovrapposizione delle due parti reali è possibile ottenere un'ampiezza per  $v_{1r}$  maggiore o minore di uno.

- 2. le forme d'onda generate da questa equazione accarezzano lo zero, cioè  $\exists \theta$  tale che  $V(\theta) = 0$ , senza mai diventare negative. Rispettano quindi le condizioni (1.44).

- 3. avendo tre gradi di libertà  $(\alpha, \delta \in \gamma)$ , si può dimostrare che fissati  $v_{1r} \in v_{1q}$  si ottiene un sistema lineare di equazioni che permette di calcolare due parametri rispetto ad un terzo considerato variabile.

Il punto 3 suggerisce che le soluzioni di (1.50) rappresentano un caso limite: questo limite è appunto il *contorno di clipping*. Da un lato del contorno la tensione sarà sempre positiva, dall'altro scenderà sotto lo zero.

Considerando (1.50), sviluppando il prodotto e normalizzando rispetto alla fondamentale si ricavano i seguenti coefficienti della serie di Fourier:

$$v_{1r} = \frac{-\alpha sin(\gamma) - cos(\delta)}{1 - \frac{\alpha}{2} sin(\delta - \gamma)} \qquad v_{1q} = \frac{-\alpha cos(\gamma) + sin(\delta)}{1 - \frac{\alpha}{2} sin(\delta - \gamma)}, \tag{1.51}$$

$$v_{2r} = \frac{\frac{\alpha}{2}sin(\delta + \gamma)}{1 - \frac{\alpha}{2}sin(\delta - \gamma)} \qquad v_{2q} = \frac{\frac{\alpha}{2}cos(\delta + \gamma)}{1 - \frac{\alpha}{2}sin(\delta - \gamma)}, \tag{1.52}$$

$$v_{3r} = 0 v_{3q} = 0. (1.53)$$

Come risultato del fatto che la rete di carico diventa più sensibile alle variazioni dei componenti alle alte frequenze, il tipico modo di procedere prevede, una volta scelta la topologia, la regolazione prima del comportamento alla fondamentale per poi passare alla risoluzione delle equazioni (1.51) e (1.52) con appunto la fondamentale fissata. Matematicamente, per una tensione nota alla prima armonica  $[v_{1r}, v_{1q}]$  e di conseguenza una  $Z_1$  nota, esiste un'insieme di soluzioni

$$S = \{ [\alpha_1, \delta_1, \gamma_1], \dots, [\alpha_n, \delta_n, \gamma_n] \}$$

$$(1.54)$$

che portano proprio a  $[v_{1r}, v_{1q}]$ . Con queste soluzioni è possibile calcolare i coefficienti della tensione alla seconda armonica

$$S_2 = \{ [v_{2r-1}, v_{2q-1}], \dots, [v_{2r-n}, v_{2q-n}] \}.$$

(1.55)

e con tali ampiezze, conoscendo la corrente di drain, si trovano le impedenze che danno luogo alle forme d'onda desiderate.

#### 1.6 Trasformatori

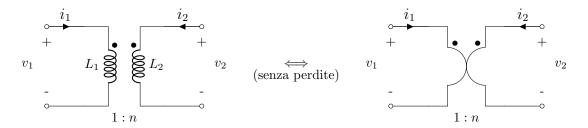

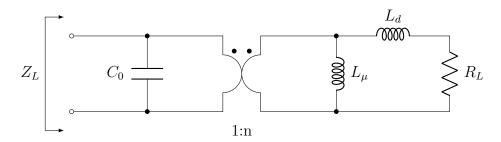

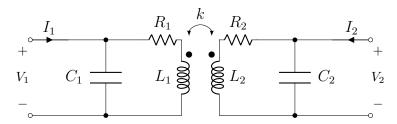

Nella progettazione dell'amplificatore di potenza descritto in questa tesi si fa uso di due trasformatori, uno per eseguire un adattamento di impedenza all'ingresso del PA ed uno per realizzare il carico necessario al funzionamento in classe J. È quindi utile introdurre un modello di trasformatore che ne approssimi il comportamento reale e che tenga conto di alcune non idealità per riuscire a dimensionare correttamente il sistema.

Come descritto in [32] si presenta inizialmente il trasformatore ideale in figura 1.14, formato da un sistema di due induttori, uno primario  $(L_1)$  e l'altro secondario  $(L_2)$ , accoppiati magneticamente. Per il singolo induttore si ha che la tensione ai suoi capi è la diretta conseguenza di una variazione di flusso magnetico all'interno delle sue spire, come espresso dalla legge di Faraday. Per più induttori accoppiati la

legge continua a valere, in particolare si ha che una variazione di flusso prodotta dal primario induce una tensione ai capi del secondario, e viceversa. Inoltre, vista la presenza del rapporto di trasformazione n, una variazione di flusso comune ad entrambi gli induttori comporta una tensione  $v_2$  n volte superiore a  $v_1$ . Per la conservazione dell'energia, questo aumento di  $v_2$  deve essere accompagnato da una diminuzione di corrente  $i_2$  dello stesso fattore. Di conseguenza si ha che il trasformatore esegue anche una trasformazione di impedenza di un fattore  $n^2$ . Nel modello ideale appena descritto è ipotizzato che tutto il flusso magnetico generato da un induttore venga concatenato dall'altro, senza alcuna perdita. Questo comportamento non corrisponde tuttavia a quello di un trasformatore reale che è invece caratterizzato da un accoppiamento imperfetto.

Figura 1.14: Rappresentazione del trasformatore ideale senza perdite.

Per quanto detto finora ci si aspetta, che  $v_1$  e  $v_2$  siano dati dalla sovrapposizione di due termini, uno di autoinduzione e uno di mutua induzione:

$$v_1 = L_1 \frac{di_1}{dt} + M \frac{di_2}{dt} (1.56)$$

$$v_2 = M \frac{di_1}{dt} + L_2 \frac{di_2}{dt} \tag{1.57}$$

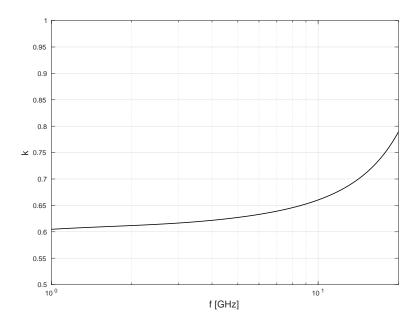

dove M è chiamata mutua induttanza e descrive il grado di accoppiamento tra primario e secondario, assumendo valori sia positivi che negativi a seconda che la mutua induzione sia concorde o discorde all'autoinduzione. È possibile poi definire un parametro che dia un'indicazione quantitativa sulla qualità dell'accoppiamento tra i due induttori, questo è il coefficiente di accoppiamento, indicato con k e dato da:

$$k = \frac{M}{\sqrt{L_1 L_2}}. (1.58)$$

Il range di valori possibili per questo parametro è  $k \in [0, 1]$ , dove 1 sta ad indicare un accoppiamento perfetto.

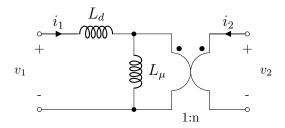

In figura 1.15 è mostrato il modello di trasformatore usato in questa tesi, che include le perdite nella concatenazione del flusso. È costituito da un trasformatore ideale e da due induttanze non accoppiate  $L_d$  e  $L_\mu$ . L'induttanza di dispersione,  $L_d$ , tiene conto del flusso che non viene concatenato mentre l'induttanza di magnetizzazione,  $L_\mu$ , rappresenta la porzione di  $L_1$  al primario che partecipa all'accoppiamento.

Inoltre  $L_{\mu}$  impedisce il funzionamento a DC, proprio come accade nella realtà. Di conseguenza possiamo scrivere:

$$L_d = L_1(1 - k^2)$$

;  $L_\mu = L_1 k^2$  (1.59)

dove è visibile come, per  $k=1,\,L_{\mu}$  sia proprio  $L_1$  di figura 1.14.

In presenza di flusso disperso, il rapporto di trasformazione n può essere espresso come segue:

$$n = \frac{L_2}{M} = \frac{1}{k} \sqrt{\frac{L_2}{L_1}}. (1.60)$$

Figura 1.15: Modello equivalente del trasformatore reale con accoppiamento imperfetto.

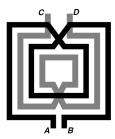

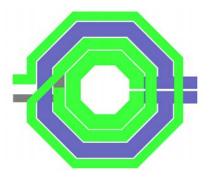

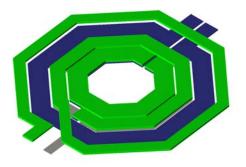

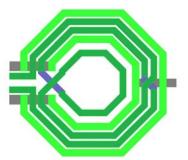

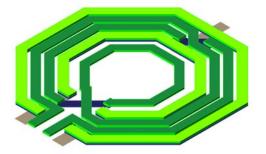

Una volta effettuato il dimensionamento, si passa alla realizzazione del trasformatore integrato. Questo sfrutta i vari strati di metal e le geometrie permesse dalla tecnologia per realizzare degli induttori planari tali da [41]:

- minimizzare la resistenza serie degli avvolgimenti;

- massimizzare l'accoppiamento magnetico;

- ridurre al minimo le capacità parassite tra gli avvolgimenti;

- presentare un basso accoppiamento capacitivo con il substrato.

Come spesso accade, un trade-off tra le caratteristiche appena elancate è la soluzione più adottata.

Figura 1.16: Esempio di trasformatore integrato con struttura quadrata.

## Capitolo 2

# Progettazione circuitale

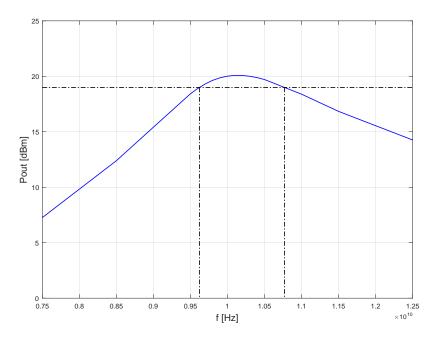

Per permettere il confronto con altri amplificatori di potenza in classe J realizzati in tecnologie diverse, vengono considerate le seguenti specifiche di funzionamento:

- potenza di uscita pari a 20dBm;

- carico pari a  $50\Omega$ ;

- frequenza di centro banda pari a 10GHz.

Ulteriori vincoli, come la tensione di alimentazione e le dimensioni minime dei MOSFET, sono imposti dalla tecnologia utilizzata (la UMC130nm).

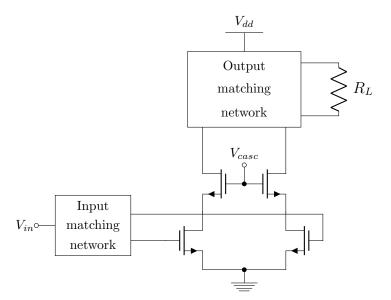

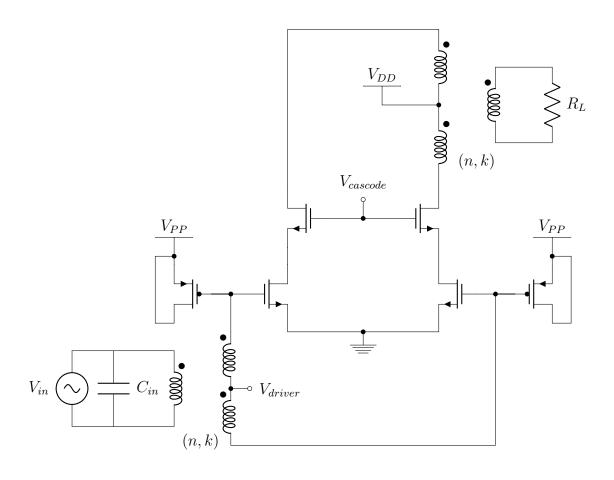

Per il core dell'amplificatore si è scelto di utilizzare una struttura cascode differenziale come quella mostrata in figura 2.1. Lo stadio differenziale permette infatti la cancellazione della distorsione armonica di ordine pari e un'alta reiezione dei segnali di modo comune. La configurazione cascode, in cui si osserva la presenza di uno stadio a source comune il cui drain fa da ingresso per uno stadio a gate comune, permette invece di aumentare lo swing della tensione d'uscita. Inoltre, migliorando l'isolamento tra input ed output ( $|S_{12}|$  più piccolo), rende il circuito più stabile [41].

### 2.1 Rete di carico

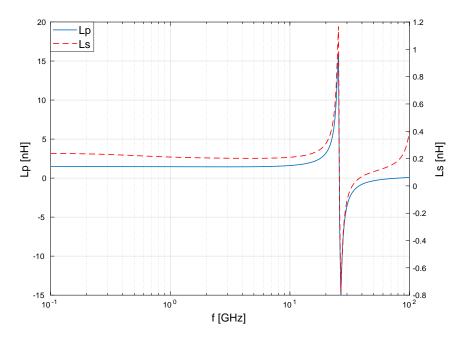

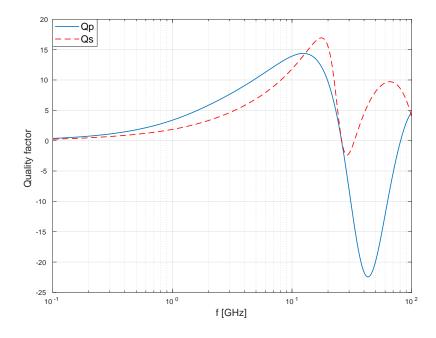

La rete di adattamento in uscita, visibile in figura 2.1, è costituita essenzialmente da un trasformatore. Questo si rende necessario per eseguire una trasformazione di impedenza e presentare ai transistor un carico inferiore, il quale necessita di un'ampiezza zero-picco di tensione più bassa per rispettare i 20dBm di specifica sulla potenza d'uscita. Altrimenti si avrebbe, con  $R_L$  pari a  $50\Omega$ :

$$V_{max} = \sqrt{2RP_{out}} = 3.16V.$$

(2.1)

Considerando invece una  $V_{max}$  pari a 1.2V risulta

$$R = \frac{V_{max}^2}{2P} = 7.2\Omega. {(2.2)}$$

Figura 2.1: Schema teorico del PA, con struttura differenziale e transistor di cascode.

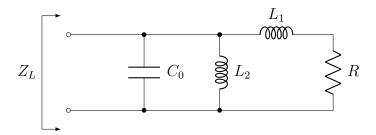

Figura 2.2: Schema elettrico del carico necessario per un funzionamento in classe J

Per un funzionamento in classe J, è necessario avere un'impedenza d'uscita ben precisa alla prima e alla seconda armonica. Lo schema elettrico più funzionale per questo scopo è quello di figura 2.2, dove lo si è reso il meno complesso possibile per evitare che le perdite dovute ai suoi componenti parassiti abbiano un peso rilevante.

Come descritto nel precedente capitolo, nella sezione riguardante il classe J, alla fondamentale deve esserci un'impedenza resistivo-induttiva, equazione (1.48). Si evince allora una prima condizione da imporre per il dimensionamento del carico, ovvero la risonanza tra  $C_0$  ed  $L_2$  per f=10GHz in modo da avere  $Z_L$  pari alla serie di  $L_1$  ed R:

$$\frac{1}{\sqrt{L_2 C_0}} = w_0. {(2.3)}$$

Sempre da (1.48) risulta che la parte reale e la parte immaginaria di  $Z_1(w_0)$  devono coincidere ed essere pari alla parte resistiva:

$$w_0 L_1 = R \tag{2.4}$$

dove R è fissata dalle specifiche sulla potenza.

Per quanto riguarda la seconda armonica, se si calcola  $Z_L(j2w_0)$  a partire dal circuito in figura 2.2, considerando le condizioni per la fondamentale (2.3) e (2.4), si ottiene

$$Z_L(j2w_0) = \frac{(2-j)\frac{2}{3}\sqrt{\frac{L_2}{C_0}}}{1+j(2-\frac{2}{3}\frac{1}{R}\sqrt{\frac{L_2}{C_0}})}$$

(2.5)

con il termine  $\frac{1}{R}\sqrt{\frac{L_2}{C_0}}$  che assume le sembianze di un fattore di qualità di un circuito RLC serie e per questo può essere espresso come  $q_s$ . Separando la parte reale di (2.5) da quella immaginaria risulta:

$$\Re\{Z_L(j2w_0)\} = R \cdot \frac{4q_s(1 - \frac{q_s}{3})}{3\left[1 + (2 - \frac{2}{3}q_s)^2\right]},\tag{2.6}$$

$$\Im\{Z_L(j2w_0)\} = R \cdot \frac{2q_s(\frac{4}{3}q_s+1)}{3\left[1 + (2 - \frac{2}{3}q_s)^2\right]}.$$

(2.7)

Adesso è possibile applicare la condizione espressa dalla (1.49), cioè  $Z_2 = -j\frac{3\pi}{8}R$ , che porta a:

$$\begin{cases} \Re\{Z_L(j2w_0)\} = 0\\ \Im\{Z_L(j2w_0)\} = \frac{3\pi}{8}R. \end{cases}$$

(2.8)

Si ottengono così due equazioni nella sola incognita  $q_s$ , le quali non possono essere contemporaneamente verificate. Andando a risolvere la condizione per  $\Im\{Z_L(j2w_0)\}$  si trova  $q_s = 1.367$ . Questo valore di  $q_s$ , usato nella (2.6), dà origine ad una parte reale non nulla alla seconda armonica che, per quanto detto sui contorni di clipping, è tollerata entro certi limiti ma comporta una riduzione dell'efficienza massima.

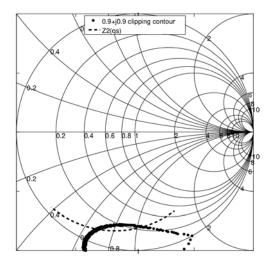

Figura 2.3: Confronto tra  $Z_L(j2w_0)$ , al variare di  $q_s$  compreso nell'intervallo  $0.5 \le q_s \le 1.5$ , e il contorno di clipping calcolato per  $v_1 = 0.9 + j0.9$ .

Come descritto in [42], se si va a plottare (2.5) per  $0.5 \le q_s \le 1.5$  e lo si confronta con il contorno di clipping calcolato per  $v_1 = 0.9 + j0.9$ , quello che si ottiene è la carta di Smith di figura 2.3 dove si notano due aspetti:

- $Z_2(q_s)$  non evolve lungo il cerchio a resistenza nulla a causa dei valori di  $q_s$  che non permettono il verificarsi di  $\Re\{Z_L(j2w_0)\}=0$ ;

- per valori di  $q_s$  approssimativamente compresi in  $0.82 \le q_s \le 1.15$  si ha che  $Z_L(j2w_0)$  entra nel contorno di clipping rendendo possibile il funzionamento in classe J.

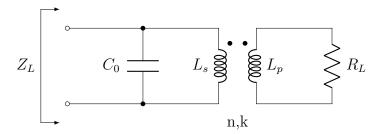

Sono state quindi trovate delle condizioni che devono essere verificate dai componenti di figura 2.2 e dal parametro  $q_s$  affinché il PA operi in classe J. Nel circuito reale però, i transistor vengono caricati con un trasformatore dove il primario è connesso ad una terminazione resistiva  $R_L = 50\Omega$ , mentre il secondario è collegato alla capacità  $C_0$  (figura 2.4).

Figura 2.4: Rete di carico con il trasformatore reale.

Utilizzando il modello per un trasformatore descritto nel capitolo precedente ci si può facilmente ricondurre al circuito di figura 2.5.

Figura 2.5: Rete di carico con il trasformatore sostituito dal suo modello.

Tra il carico necessario per il funzionamento in classe J (figura 2.2) ed il modello del circuito usato per l'impedenza  $Z_L$  del PA descritto in questa tesi (figura 2.5), esiste un legame dato dalle equazioni:

$$L1 = L_s \frac{1 - k^2}{k^2}$$

;  $L_2 = L_s$  ;  $R = \frac{R_L}{(nk)^2}$  (2.9)

È possibile inoltre ricavare una formula per esprimere il fattore di accoppiamento k in funzione di  $q_s$ . Da (2.9), utilizzando (2.3), (2.4) e ricordando che  $q_s = \frac{1}{R} \sqrt{\frac{L_2}{C_0}}$ , si ha

$$k = \sqrt{\frac{q_s}{1 + q_s}} \tag{2.10}$$

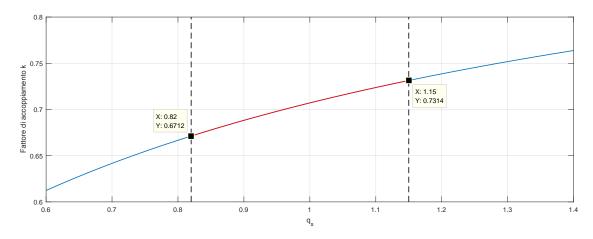

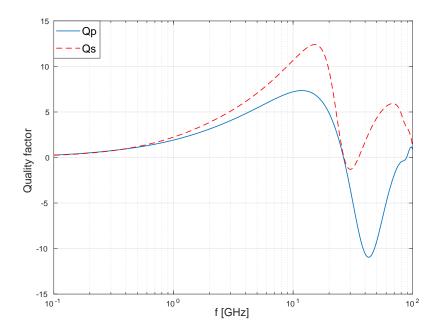

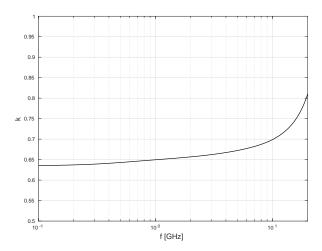

il cui andamento è rappresentato in figura 2.6. Si può vedere come, per restare in un funzionamento tipico della classe J caratterizzato da  $0.82 \le q_s \le 1.15$ , è necessario che k assuma dei valori compresi nell'intervallo  $0.67 \le k \le 0.73$ .

Figura 2.6: Andamento del fattore di accoppiamento k in funzione del parametro  $q_s$ .

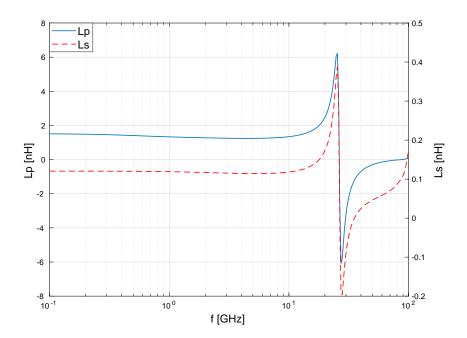

Si è ora a conoscenza di un numero sufficiente di condizioni per poter dimensionare la rete di carico in figura 2.4, in particolare, fissando il fattore di accoppiamento al valore k = 0.7 facilmente realizzabile in tecnologia integrata e corrispondente a  $q_s \approx 0.961$ , si ottiene:

$$n = \frac{1}{k} \sqrt{\frac{R_L}{R}} = 3.76, \tag{2.11}$$

$$L_1 = \frac{R}{w_0} = 57.3pH, (2.12)$$

$$L_2 = q_s L_1 = 55.1 pH, (2.13)$$

$$C_0 = \frac{1}{w_0^2 L_2} = 4.6pF, (2.14)$$

$$L_s = L_2 = 55.1pH, (2.15)$$

$$L_p = n^2 L_s = 780.3 pH. (2.16)$$

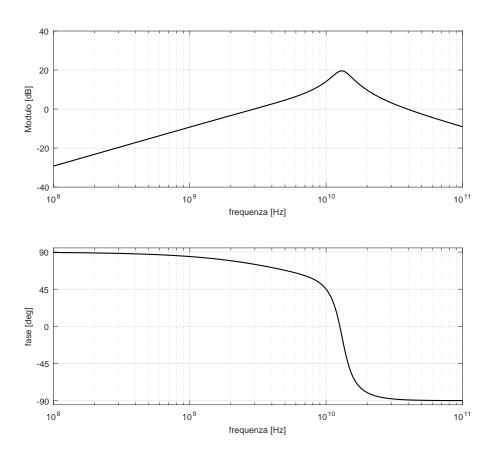

Graficando l'impedenza  $Z_L$  della rete di carico (figura 2.4) con i parametri appena calcolati si ottiene un andamento per modulo e fase visibile in figura 2.7. Il comportamento voluto alla prima armonica è ben realizzato (la fase di 45° indica

un'impedenza con parte resistiva ed induttiva uguali), mentre alla seconda armonica, come si può capire sempre dalla fase, è presente una parte resistiva oltre a quella capacitiva voluta. Quest'ultimo comportamento era atteso visto che il fattore  $q_s$  non soddisfa la condizione sulla parte reale di  $Z_L(j2w_0)$ .

Figura 2.7: Modulo e fase dell'impedenza di carico.

### 2.2 Dimensionamento dei transistor

Allo scopo di ridurre la tensione di picco presente all'uscita dei transistor, è stata introdotta una rete di adattamento, formata da una trasformatore, tra il PA e la resistenza di carico. Rete che, come è stato spiegato nei capitoli precedenti, costituisce un ruolo fondamentale nel realizzare la giusta impedenza per permettere il funzionamento in classe J. Viene quindi eseguita una trasformazione di impedenza che riduce  $R_L$  al valore R in modo da rendere necessario uno swing di tensione minore per fornire al carico la potenza richiesta. Questo calo di tensione però implica un aumento dello stesso fattore della corrente generata dai transistor.

Se si esprime in serie di Fourier l'andamento ideale di corrente (1.34), quello che si ottiene è:

$$i_D(t) = \frac{i_{rf}}{\pi} + \frac{i_{rf}}{2}cos(wt) + \frac{2}{3\pi}i_{rf}cos(2wt).$$

(2.17)

La prima armonica è perciò caratterizzata da un'ampiezza massima pari a  $\frac{i_{rf}}{2}$ . Imponendo la potenza di 0.1mW sulla resistenza trasformata  $R=7.2\Omega$  si può calcolare il valore  $i_{rf}$  necessario:

$$P = \frac{1}{2}R\left(\frac{i_{rf}}{2}\right)^2 \iff i_{rf} = \sqrt{\frac{8P}{R}}.$$

(2.18)

Andando a sostituire quest'ultimo in (2.17) è possibile ricavare il picco  $I_{max}$  della forma d'onda di corrente  $i_D$  con il quale dimensionare i transistor.

Per un MOSFET in saturazione, con un valore fissato per la tensione di overdrive  $(V_{ov} = 200mW)$ , imponendo la corrente massima si può scrivere

$$I_{max} = \frac{k'}{2} \frac{W}{L} \frac{V_{ov}^2}{1 + \theta V_{ov}}$$

(2.19)

con  $k' = \mu_n C_{ox}$  e  $\theta$  parametro della tecnologia dipendente dalla lunghezza di canale L che tiene conto degli effetti di canale corto. Si ricava così il rapporto W/L con il quale dimensionare i transistor.

Una volta fissate le dimensioni dei mos è importante verificare il valore di capacità parassita che offrono al nodo di uscita perchè andrà a contribuire, se non realizzare completamente, la capacità  $C_0$  del carico. In fase di progettazione questa verifica, una volta imposte le dimensioni ideali calcolate, ha portato ad un valore di capacità superiore a quello voluto, per questo si è reso necessario diminuire le grandezze dei dispositivi fintanto che non è stato realizzato un valore di  $C_0$  molto prossimo a (2.14). È utile notare che anche il trasformatore andrà a contribuire alla  $C_0$  con la sua capacità parassita al secondario.

## 2.3 Circuito di polarizzazione

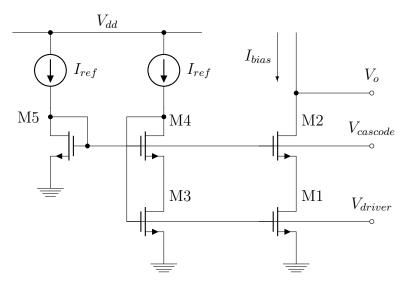

Il PA necessita di un circuito di polarizzazione per fissare il punto di lavoro in assenza di segnale di ingresso. Sarà responsabile quindi di generare le tensioni DC ai nodi dei transistor in modo da imporre una certa corrente di bias  $(I_{bias})$ .

Si è scelto di utilizzare lo specchio di corrente cascode high swing di figura 2.8, dove M1 e M2 rappresentano i transistor di un ramo dell'amplificatore di potenza. Questa configurazione, a differenza di un normale specchio di corrente, permette di diminuire di un termine pari alla tensione di soglia  $V_{th}$  la minima  $V_o$  necessaria per mantenere i transistor del PA in saturazione. Sotto l'ipotesi di tensione di overdrive uguale per i diversi mos risulta quindi [43]:

$$V_{o,min} = 2V_{ov}. (2.20)$$

Figura 2.8: Schema di uno specchio di corrente cascode high swing usato per polarizzare il PA.

Per dimensionare lo specchio si è fissata inizialmente  $I_{bias} = I_{ref} = \frac{I_{max}}{10}$  e si sono posti i transistor M3 e M4 delle stesse dimensioni di quelli del PA. Il MOSFET M5 invece, è stato realizzato con una larghezza di canale minore così da alzare la tensione  $V_{DS,M3}$ , ponendo attenzione a non mandare in triodo M4. Allo scopo di diminuire il consumo di potenza legato al circuito di polarizzazione, sono state scalate della stessa quantità sia le correnti  $I_{ref}$  che il fattore di forma di M3, M4 ed M5. Così facendo si è mantenuta costante la tensione di overdrive e non è stato modificato il punto di lavoro dei transistor. In altre parole l'angolo di conduzione è restato fisso perchè la  $V_{GS}$  è rimasta inalterata. Diverse prove hanno portato alla realizzazione di un fattore di specchio pari a 11.

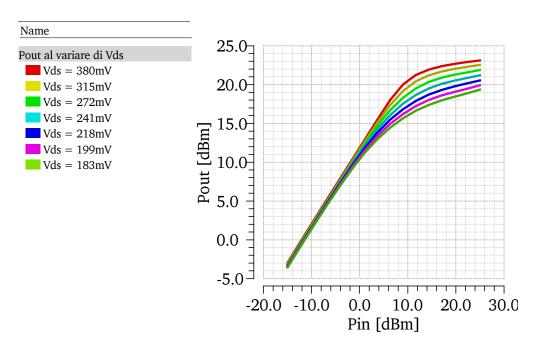

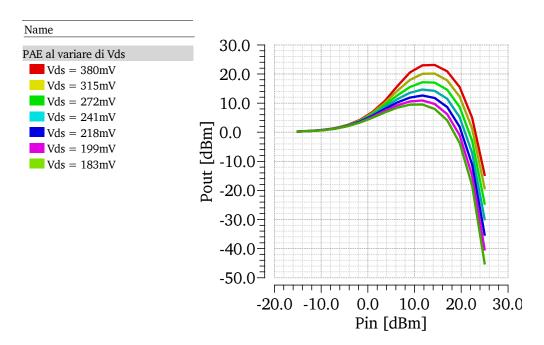

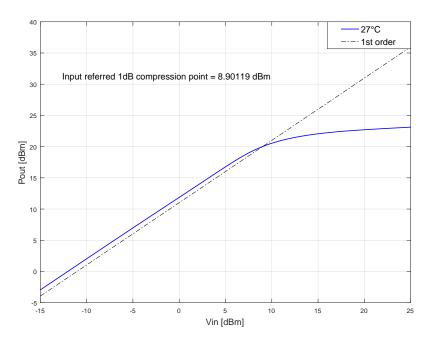

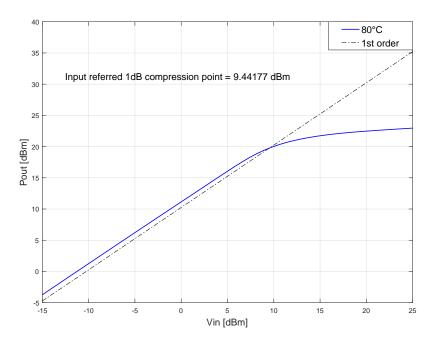

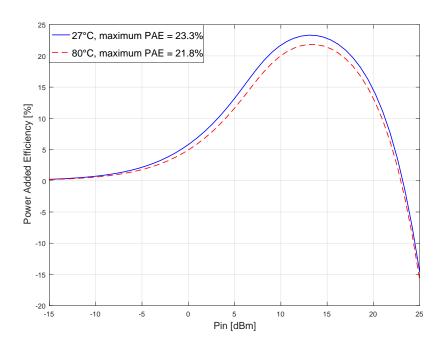

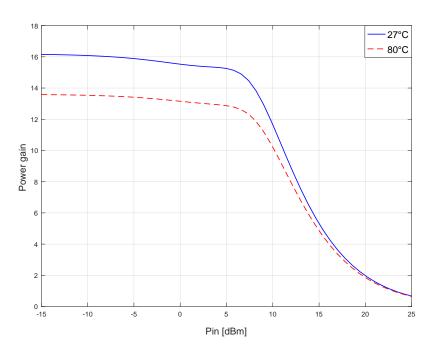

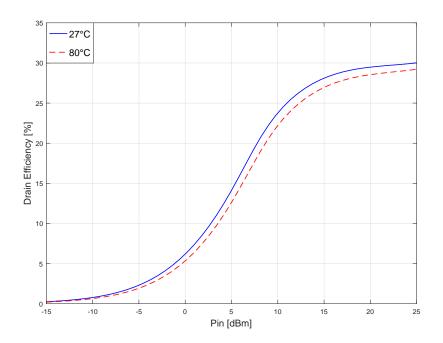

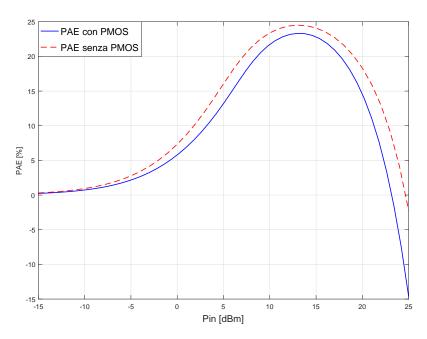

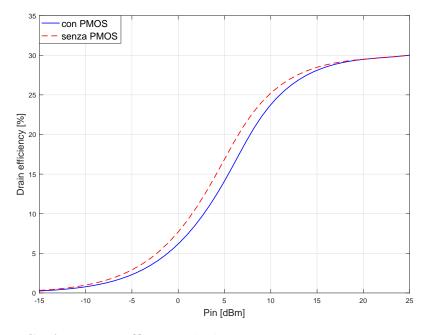

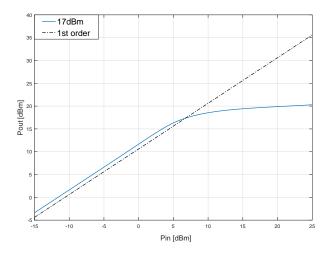

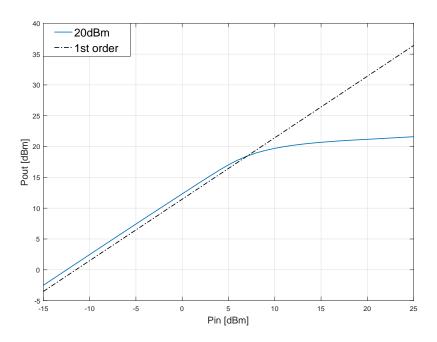

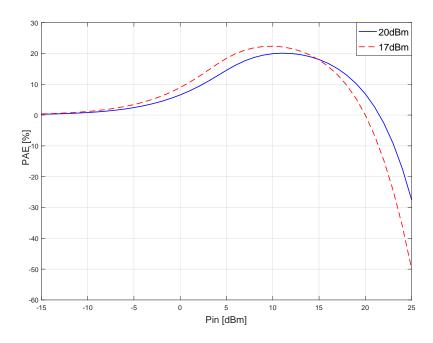

Attraverso delle simulazioni è stato poi aggiustato il valore di  $I_{ref}$  in modo da raggiungere il compromesso più soddisfacente tra potenza in uscita ed efficienza. Variare  $I_{ref}$ , e di conseguenza  $I_{bias}$ , ha l'effetto teorico di portare l'amplificatore a lavorare più in classe B (maggiore efficienza) se la corrente di riposo cala, e più in classe A (maggiore potenza) se  $I_{bias}$  cresce. Agendo poi sulle dimensioni di M5 è stata massimizzata la tensione  $V_{DS}$  dei driver in modo da mantenerli in saturazione il più possibile ed evitare, quando sono in conduzione, il loro funzionamento in triodo. Questo è vantaggioso in termini di potenza d'uscita come si può vedere dal grafico in figura 2.9 che mostra l'andamento di  $P_{out}$  in funzione di  $P_{in}$  per diversi valori di  $V_{DS}$  dei driver. Lo stesso vale per la PAE riportata in figura 2.10. Altro parametro che si è preso in considerazione nella messa a punto del circuito di bias è il 1dB-compression point. Si è fatto in modo che la potenza in ingresso necessaria per ottenere i 20dBm in uscita risultasse inferiore alla  $P_{in}$  responsabile di una compressione di 1dB così da mantenere una buona linearità e diminuire le distorsioni.

Figura 2.9: Potenza di uscita al variare della potenza di ingresso per diversi valore di tensione  $V_{DC}$  di polarizzazione dei driver.

Figura 2.10: PAE al variare della potenza di ingresso per diversi valore di tensione  $V_{DC}$  di polarizzazione dei driver.

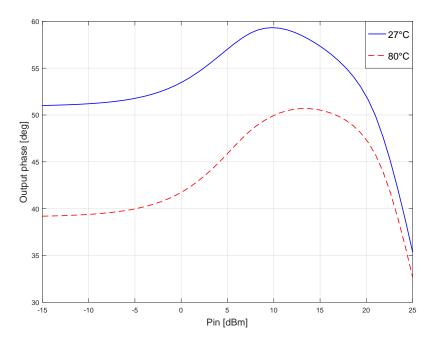

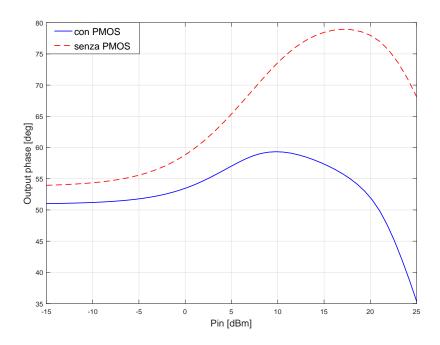

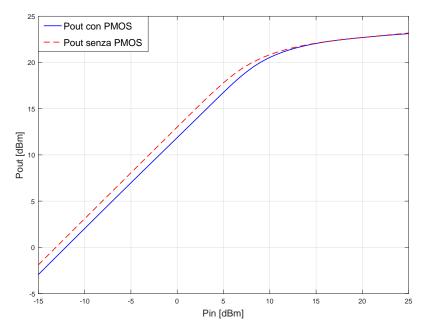

### 2.4 Miglioramento AM-to-PM conversion

La modalità di funzionamento in classe AB per un amplificatore di potenza offre una buona linearità unita a discreti livelli di efficienza. Nonostante la sua linearità sia superiore a quella di un classe B, spesso non è sufficiente per rispettare le specifiche imposte. Questo è dovuto soprattutto al passaggio tra lo stato ON e quello OFF del transistor che comporta distorsione. Un PA in classe AB è infatti polarizzato con una  $V_{GS}$  prossima alla tensione di soglia in modo da riuscire a spegnersi e diminuire l'angolo di conduzione con un conseguente miglioramento dell'efficienza.

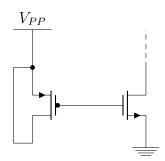

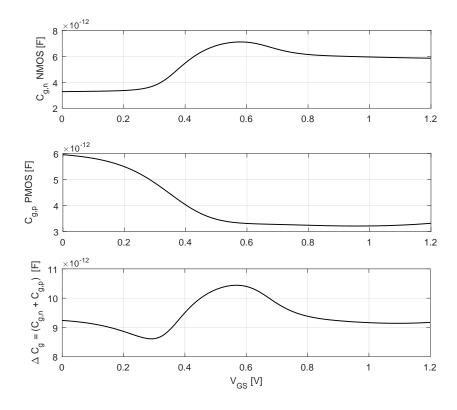

Come dimostrato in [44], molti effetti di distorsione sono introdotti dalle capacità parassite connesse al gate del transistor e, in particolare, un ruolo dominante è quello della capacità gate-source. La  $C_{gs}$  per un n-mos (figura 2.12) presenta, al variare della  $V_{GS}$ , un andamento tipico crescente in corrispondenza della tensione di soglia che è solitamente approssimato con un gradino. In figura 2.12 è anche rappresentato l'andamento della capacità di gate di un p-mos in funzione della tensione gate-source, con  $V_{DS}$  costante. Si può notare come il suo comportamento sia esattamente complementare a quello di un n-mos. Questa caratteristica rende possibile la compensazione della variazione di  $C_g$  di un n-mos mediante un p-mos opportunamente dimensionato e polarizzato, connesso come lo schema di figura 2.11. Così facendo la capacità totale all'ingresso dei MOSFET risulta quasi costante riducendo la distorsione generata al gate e di conseguenza quella riportata al drain.

Figura 2.11: Schema per compensare la variazione della capacità di gate di un n-mos utilizzando un dispositivo p-mos.

Il cambiamento del valore di  $C_g$  nei due dispositivi avviene in corrispondenza della propria tensione di soglia. È quindi necessario, perchè le due variazioni possano compensarsi tra loro, polarizzare il dispositivo p-mos con una tensione  $V_{PP}$  pari a:

$$V_{PP} = V_{th,n} - V_{th,p}. (2.21)$$

Inoltre, notando che il MOSFET di tipo n passa dalla weak alla strong inversion e che il MOSFET di tipo p lavora in triodo, si possono approssimare le variazioni di capacità ai due gate come [44]:

$$\begin{cases} \Delta C_{g,n} \approx \Delta C_{gs,n} \approx \frac{2}{3} W_n L_n C_{ox,n} \\ \Delta C_{g,p} \approx \Delta (C_{gs,p} + C_{gd,p}) \approx W_p L_p C_{ox,p}. \end{cases}$$

(2.22)

Imponendo infine l'uguaglianza tra  $\Delta C_{g,n}$  e  $\Delta C_{g,p}$  si ottiene una condizione che può essere usata per calcolare una stima iniziale delle dimensioni del p-mos:

$$\frac{\Delta C_{g,n}}{\Delta C_{g,p}} \approx \frac{2}{3} \frac{W_n L_n C_{ox,n}}{W_p L_p C_{ox,p}} \approx 1. \tag{2.23}$$

In questo modo, e con una successiva messa a punto mediante simulazioni, si sono istanziati nel circuito dei dispositivi di tipo p tali da produrre una  $\Delta C_g$  totale visibile in figura 2.12.

È importante notare che se da un lato l'aggiunta del p-mos migliora la linearità del sistema, dall'altro aumenta notevolmente la capacità di ingresso totale (risulta circa il doppio) con una conseguente diminuzione di efficienza dovuta alla maggior potenza necessaria per pilotare la combinazione dei due MOSFET.

Figura 2.12: Andamenti delle capacità di gate per i dispositivi n-mos e p-mos usati nella realizzazione del PA con relativa somma  $\Delta C_g = C_{g,n} + C_{g,s}$ .

### 2.5 Rete di adattamento in ingresso

L'obiettivo di una rete di adattamento posta tra la sorgente di segnale e l'ingresso dell'amplificatore è quello di massimizzare il trasferimento di potenza e di conseguenza lo swing di tensione. Inoltre è utile per eseguire la trasformazione da single-ended a differenziale. Per questi motivi si è deciso di utilizzare un trasformatore con delle capacità in parallelo alle due porte tali da formare quello che in inglese prende il nome di transformer-based resonator (figura 2.13).

Figura 2.13: Schema elettrico di un transformer-based resonator.

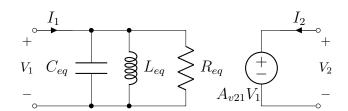

Questo dispositivo è un risuonatore che sotto opportune condizioni presenta delle caratteristiche utili per eseguire un adattamento. In particolare, come descritto in [45], nei pressi della risonanza si può approssimare il suo comportamento con un parallelo RLC ottenendo il modello di figura 2.14.

Figura 2.14: Schema elettrico per il modello del transformer-based resonator valido alla risonanza.