## UNIVERSITÀ DEGLI STUDI DI PADOVA

## Facoltà di Ingegneria

Corso di Laurea Magistrale in Ingegneria Elettronica

Dipartimento di Ingegneria dell'Informazione

# Dynamic Rdson Setup and Measurements on Normally-on and Normally-off GaN-HEMT Power Electronic Devices

Relatore

PROF. Gaudenzio Meneghesso

Correlatore

Dr. Dipl. Ing. Gianmauro Pozzovivo

*Laureanda* Silvia Bigal

Anno Accademico 2011-2012

Ai miei genitori

## Abstract

The increasing demand for high performance devices, in particular in terms of power at high frequencies, has moved the research towards new materials with better properties than the ones of the materials used until now. Si and GaAs technology has by now reached its limits in terms of efficiency and stability at high frequencies. These mid-range bandgap-based electronic devices cannot be used for a wide range of application due to the limit imposed by the size of the bandgap. A solution to these kinds of problems has come from GaN and III-nitrides. The possibility of driving large current densities in GaN and to apply high voltages, together with the possibility of building heterostructures, enables the fabrication of GaN-based High-Electron-Mobility-Transistors (HEMTs) capable of large output power. The main non-ideality of interest in GaN HEMTs is the current collapse. This effect is related to electronic traps in the device structure. GaN based-HEMT's are used for high power and high frequencies applications; this effect is thus really important and considerably limits the performances of this kind of devices. it is possible to evaluate the current collpase by measurements of gate-lag and drain-lag. The term gate lag is used to describe the slow transient response of the drain current, when the gate voltage is pulsed. The gate lag phenomen can also be defined as an increase in the dynamic Rdson value (measured under pulsed conditions), comparing with the static Rdson value (measured in steady state). In this work we will build the GaN DReaM (GaN Dynamic Rdson Measurement): a particular setup capable of measuring the dynamic Rdson of devices both on package level and on wafer level. Then we will compare the measured dynamic value of Rdson with the static Rdson, with the aim of evaluating the level of degradation of the Rdson.

# Acknowledgments

I wish to express my most sincere gratitude to all the following people, who have in various ways contributed to the research leading to this dissertation. My first thought goes to Dr. Gianmauro Pozzovivo and Dr. Andrej Steinberger, without whom this work would not have been possible. I owe my biggest thank to them, they have been my reference point. I will never forget their infinite support and endurance.

I owe my thanks to Prof. Gaudenzio Meneghesso, who introduced me to the world of GaN and gave me the opportunity of having this unforgettable experience.

I owe my thanks to all the guys of the characterization lab: Andreas, Georg, Harald, Michael, Stefan D., Stefan L. They had an opened door when I needed assistance at any time. Thanks for your continuous support.

I owe my gratitude to all the guys of the microelectronics lab in Padova, in particular I must thank Riccardo Silvestri, who gave my the basis to start this experience in the best way.

Special thanks is for Carlo Desanti, who, even if not *HEMTista*, gave me fundamental help.

Finally I want to thank all my friends, near and faraway. Thanks for your presence and for your effort to keep up the morale.

# Contents

| 1        | Intr                 | roduction                                                      | 1         |

|----------|----------------------|----------------------------------------------------------------|-----------|

|          | 1.1                  | GaN Peculiarities and Applications                             | 1         |

|          | 1.2                  | Switching Behaviour and Losses - GaN vs Si                     | 7         |

| <b>2</b> | $\operatorname{Gal}$ | N-HEMTs - Structure and Operating Principles                   | 15        |

|          | 2.1                  | GaN Crystal Structure                                          | 15        |

|          | 2.2                  | The Concept of Heterostructure                                 | 16        |

|          | 2.3                  | HEMT's - Structure and Operating Principles                    | 18        |

|          |                      | 2.3.1 Polarization $\ldots$                                    | 21        |

|          |                      | 2.3.2 The Role of Surface's Holes and Donors in the 2DEG       |           |

|          |                      | Formation                                                      | 24        |

| 3        | Cur                  | rrent Collapse                                                 | 29        |

|          | 3.1                  | Traps                                                          | 29        |

|          | 3.2                  | Current Collapse                                               | 31        |

|          | 3.3                  | Drain Lag                                                      | 37        |

|          | 3.4                  | Gate Lag                                                       | 40        |

|          |                      | 3.4.1 Dynamic Rdson Measurement                                | 41        |

| 4        | Cla                  | mping Circuit                                                  | <b>47</b> |

|          | 4.1                  | Problems Related with the Scope's Resolution $\ . \ . \ . \ .$ | 47        |

|          | 4.2                  | Clamping Circuit - Schematic                                   | 50        |

| <b>5</b> | $\operatorname{Gal}$ | N DReaM - GaN Dynamic Rdson Measurement Setup                  | 59        |

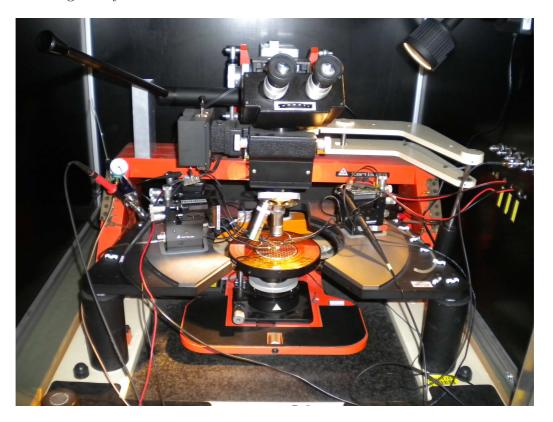

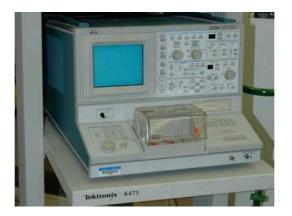

|          | 5.1                  | The Old Dynamic Rdson Measurement Setup                        | 59        |

### CONTENTS

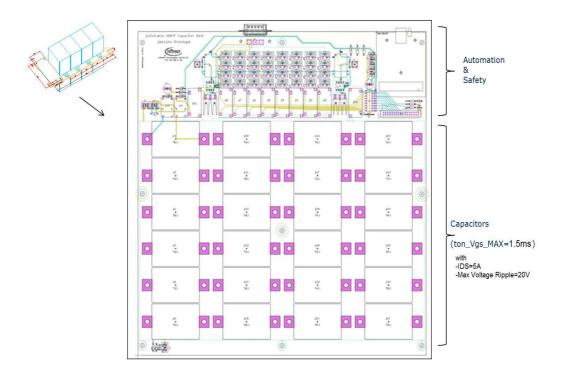

|   | 5.2   | GaN I  | DReaM: the New Dynamic Rdson Measurement Setup .          | 68  | ;; |

|---|-------|--------|-----------------------------------------------------------|-----|----|

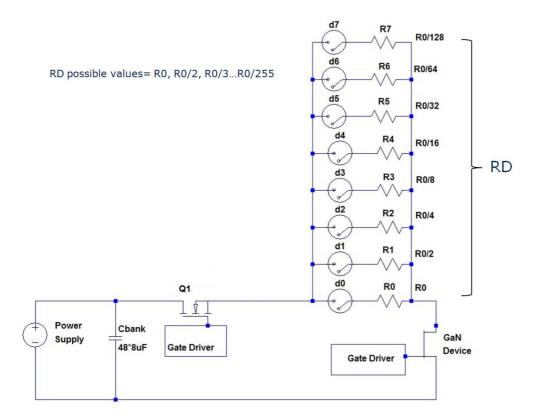

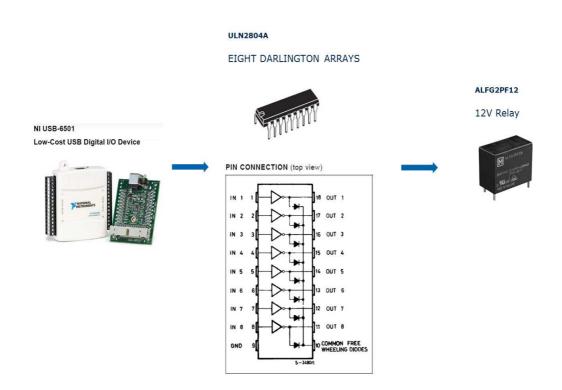

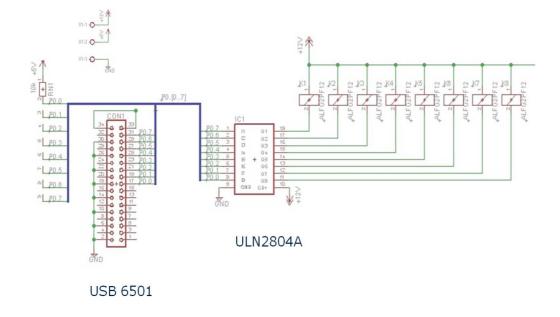

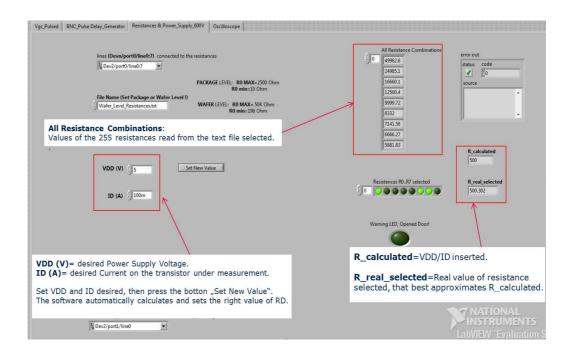

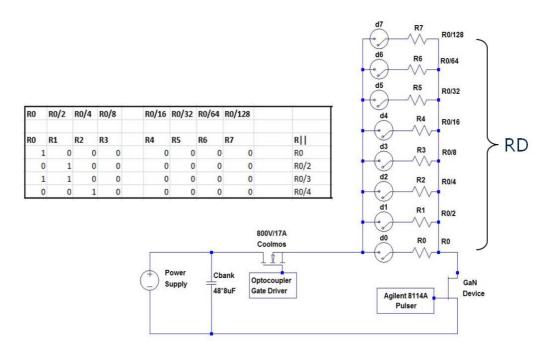

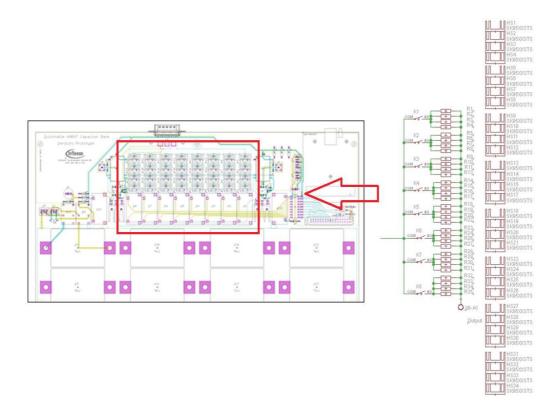

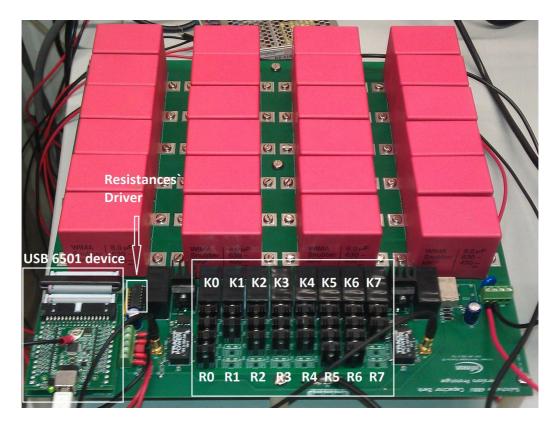

|   |       | 5.2.1  | Automatic Selection of the Drain Resistance RD            | 70  | )  |

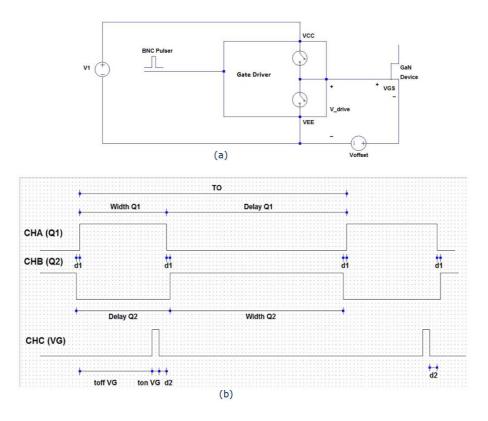

|   |       | 5.2.2  | Gate Driver                                               | 78  | ,  |

|   |       | 5.2.3  | Oscilloscope                                              | 89  | )  |

|   |       | 5.2.4  | Interlock Safety System.                                  | 93  | }  |

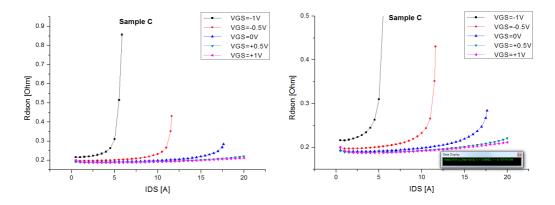

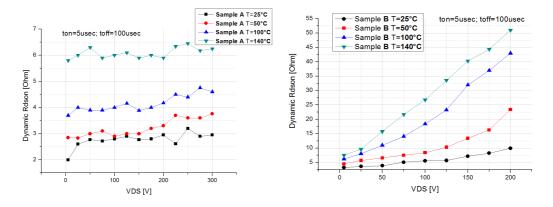

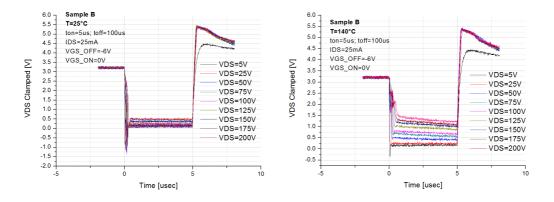

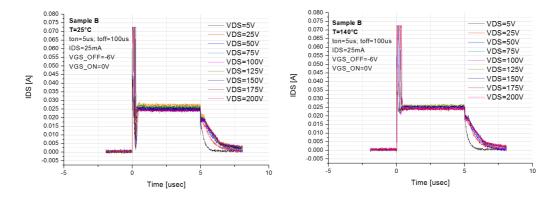

| 6 | Dyr   | namic  | Rdson Measurements                                        | 101 | -  |

|   | 6.1   | Measu  | rements on Package Level                                  | 101 | -  |

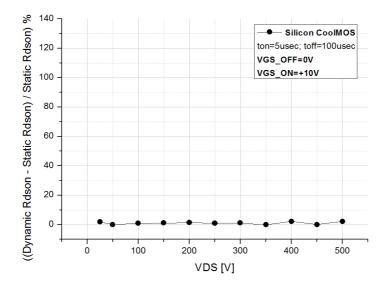

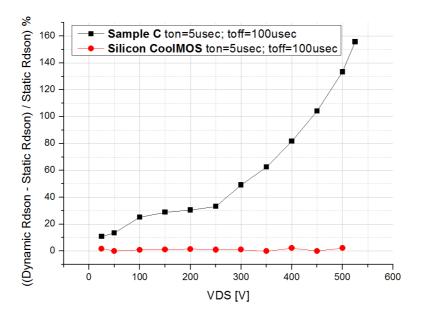

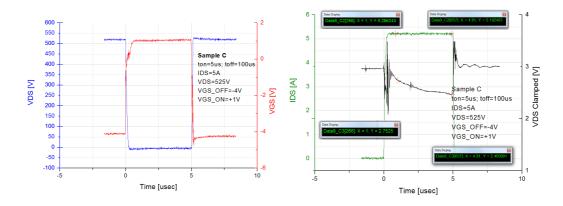

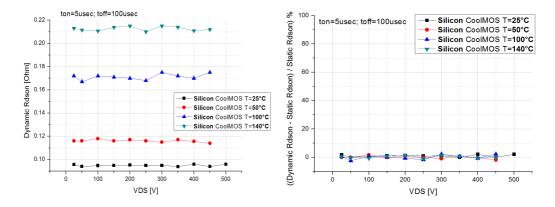

|   |       | 6.1.1  | Reference Point : Silicon CoolMOS                         | 101 | -  |

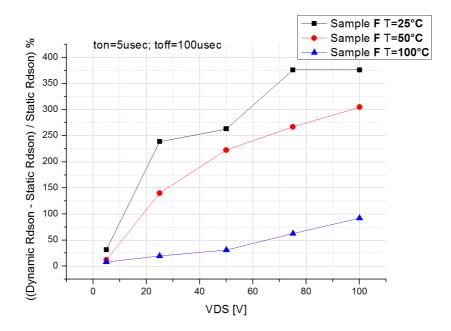

|   |       | 6.1.2  | Influence of the Drain-Source Voltage on the Degrada-     |     |    |

|   |       |        | tion of the Dynamic Rdson                                 | 108 | 3  |

|   |       | 6.1.3  | Influence of the Stress Time $t_{off}$ on the Degradation |     |    |

|   |       |        | of the Dynamic Rdson                                      | 128 | ,  |

|   |       | 6.1.4  | Recovery of the Dynamic Rdson with the On-Time $t_{on}$   | 134 | F  |

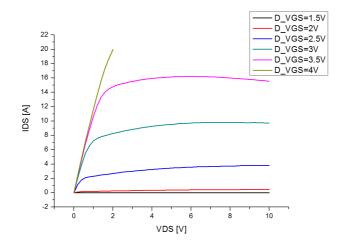

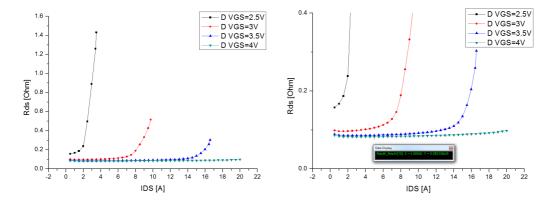

|   | 6.2   | Measu  | rements on Wafer level                                    | 141 | -  |

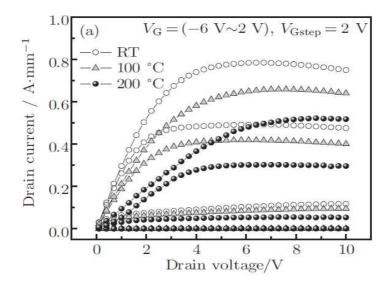

|   |       | 6.2.1  | Influence of the Temperature on the Degradation of        |     |    |

|   |       |        | the Dynamic Rdson                                         | 141 | -  |

| C | onclu | isions |                                                           | 148 | ;  |

| R | efere | nces   |                                                           | 151 | -  |

ii

## Chapter 1

# Introduction

## **1.1 GaN Peculiarities and Applications**

The increasing demand for high performance devices, in particular in terms of power at high frequencies, has moved the research towards new materials with better properties than the ones of the materials used until now. Si and GaAs technology has by now reached its limits in terms of efficiency and stability at high frequencies; in the last decades these properties became fundamentals, thanks to the fast development of telecommunication and broadband access systems: there is an increasing demand for much more smaller systems capable of transferring datas very fast. high power and high temperature transistors are needed for automobile engines, future advanced power distribution systems, all electric vehicles and avionics. Many power electronics devices are used for voltage and frequency control for transmitting and converting electric power; reductions in loss and performance improvement of these devices will directly lead to considerable reduction in electric power consumption.

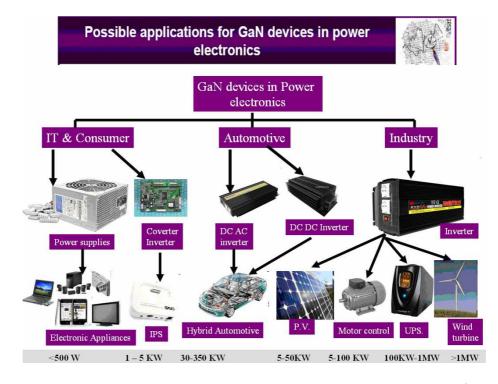

The semiconductors which have been used in electronics until now are Silicon (Si), Gallium Arsenide (GaAs) and all related III-V materials. The energy bandgap of these semiconductors are 1.12 eV for Si and 1.43 eV for GaAs, which are mid-range values. Unfortunately those mid-range bandgapbased electronic devices cannot be used for a wide range of application due to the limit imposed by the size of the bandgap. A solution to these kinds of problems has come from GaN and III-nitrides. Some possible applications of GaN devices in power electronics are shown in fig. 1.1.

Figure 1.1: Some Applications of GaN Devices in Power Electronics (from a Yole Development study).

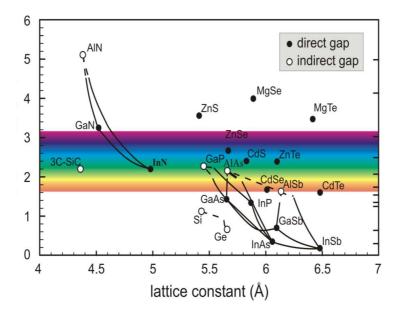

The bandgap of III-nitrides are large and direct and vary from 0,7 eV for InN to 6,2 eV for AlN.

The graph 1.2 indicates that semiconductors with small lattice constant exhibit larger bandgap energies; a small lattice constant stands for strong interatomic forces, which are responsible for the strong chemical bonding, thus leading to a large bandgap energy. GaN owns a high energy gap; this is a great advantage is terms of device's performances: the energy gap represents the energy that the electric field must give to a carrier, in order to bring it to the conduction band; thanks to the high energy gap values, GaN can easily support very high breakdown electric fields, so that the size of the devices can be reduced. In particular we usually have high electric field values between

Figure 1.2: Bandgaps of the most important elemental and binary cubic semiconductors versus their lattice constant at 300K. The right-hand scale gives the light wavelength  $\lambda$ , corresponding to the band gap energy.[5][19]

Gate and Drain, thus it is possible reduce this distance. The large Band Gap, moreover, enables GaN to operate at high temperatures: High energy gaps lead to low thermical carrier generation, so that we avoid problems of intrinsical generation with temperature. The thermal conductivity of Nitrides is about three times that of Si, therefore GaN power electronic devices can operate with less cooling and fewer high cost processing steps associated with complicated structures designed to maximize heat extraction [Pearton 2000].

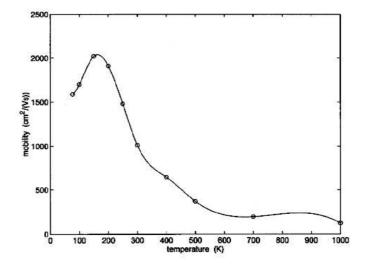

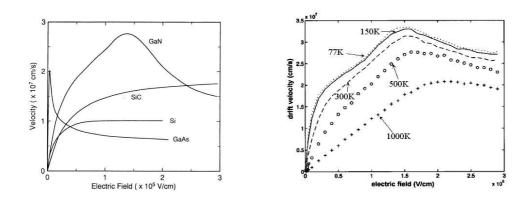

One of the main features of Nitrides is the possibility of fabricating heterostructures with larger band discontinuity, by using AlGaN, AlInGaN or InAlN. A two dimensional electron gas (2DEG) is formed at the heterostructure's interface due to spontaneous and piezoelectric polarization (more detail will be given in the next section). The presence of a 2DEG leads to a high maximum drift velocity (fig. 1.4) and a relatively high electron mobility (fig 1.3), comparable with the intrinsic semiconductor, thanks to the absence of scattering phaenomenas between carriers or between carriers and doping impurities.

Figure 1.3: GaN Electron Mobility [1].

These peculiarities make GaN-based heterostructures especially promising as high frequency devices.

Electron mobility and drift velocity depend also on the temperature: in the graphs in fig 1.3 [1] we can see that the value of the electron mobility at 300K is about  $1000cm^2/Vs$ , before going down while the temperature is increasing, due to scattering phaenomenas.

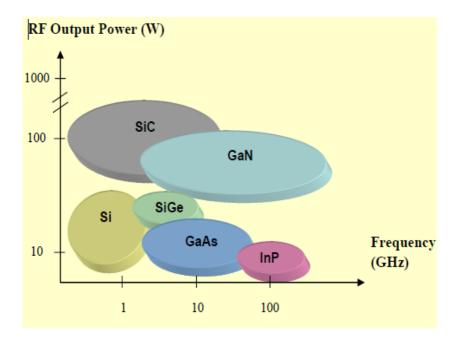

The comparison of GaN with some other important semiconductor materials is shown in fig. 1.5 [Yole 2005]; all semiconductors, which are promising candidates for the RF applications, are schematically indicated in a frequency-power diagram. Current technology is mainly based on Si or GaAs devices. As illustrated in fig. 1.5, GaN covers a fairly large frequency range while maintaining a high output power relative to the others. It is in strong competition with SiC on its low frequency side and with GaAs and InP on its low power/ high frequency side.

To further apprehend the advantages of GaN for future RF market, the material properties and figures of merit (FOM) of GaN, InP, GaAs, SiC and Si are summarized in Table 1.6. The FOM values for GaN are orders of magnitude higher than those for Si or GaAs and slightly higher than those

Figure 1.4: Electron Drift Velocity of GaN, SiC, Si and GaAs at 300 K omputed Using the Monte Carlo Technique [Gaska 1998] (on the left) and GaN Drift Velocity vS Temperature (right) [1].

Figure 1.5: Semiconductor Materials for RF Applications. RF Power is Plotted against Frequency [Yole 2005].

| GaN       | InP                                    | GaAs                                                                                                         | <u>SiC</u>                                                                                                                                                      | Si                                                                                                                                                                                                                                                     |

|-----------|----------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.39      | 1.35                                   | 1.42                                                                                                         | 3.26                                                                                                                                                            | 1.1                                                                                                                                                                                                                                                    |

| 3.3       | 0.5                                    | 0.4                                                                                                          | 3.0                                                                                                                                                             | 0.3                                                                                                                                                                                                                                                    |

| 1200-2000 | 5400                                   | 8500                                                                                                         | 700                                                                                                                                                             | 1350                                                                                                                                                                                                                                                   |

| 2.5       | 1                                      | 1                                                                                                            | 2                                                                                                                                                               | 1                                                                                                                                                                                                                                                      |

| 1.3       | 0.7                                    | 0.43                                                                                                         | 4.5                                                                                                                                                             | 1.5                                                                                                                                                                                                                                                    |

| 9.0       | 12.5                                   | 13.1                                                                                                         | 10.0                                                                                                                                                            | 11.8                                                                                                                                                                                                                                                   |

|           | 3.39<br>3.3<br>1200-2000<br>2.5<br>1.3 | 3.39       1.35         3.3       0.5         1200-2000       5400         2.5       1         1.3       0.7 | 3.39       1.35       1.42         3.3       0.5       0.4         1200-2000       5400       8500         2.5       1       1         1.3       0.7       0.43 | 3.39         1.35         1.42         3.26           3.3         0.5         0.4         3.0           1200-2000         5400         8500         700           2.5         1         1         2           1.3         0.7         0.43         4.5 |

of SiC. Thus, it is anticipated that GaN can outperform Si, GaAs, and SiC in the microwave electronic applications.

Figure 1.6: Physical Properties of GaN, InP, GaAs, SiC and Si [9].

By using AlGaN, AlInGaN or InAlN, it is relatively easy to produce structure with sheet electron densities of  $(1-3)*10^{13}cm^{-2}$ ; this electron density is 4-5 times larger than in AlGaAs/GaAs heterostructures, moreover the saturation drift velocity of GaN is 2.5 times that of GaAs. The maximum current is proportional to the product of the carrier density and the saturation drift velocity [18]: an approximate calculation shows that the maximum current density for GaN-based (HEMTs) is 10-15 times larger than for AlGaAs/GaAs structures.

As we said before, GaN shows also a high breakdown voltage (Vbr). The critical breakdown field varies roughly with  $Eg^2$  and is estimated to be > 3MV/cm for GaN compared to 0.3 MV/cm for Si and 0.4 MV/cm for GaAs [Bandic 1998], thus GaN-power electronic devices can be made ten times thinner than Si. The large breakdown electric field implies that a large electric field can be applied without damaging the devices. This

means that the possibility of driving large current densities and to apply high voltages, together with the possibility of building heterostructures, enables the fabrication of GaN-based High-Electron-Mobility-Transistors (HEMTs) capable of large output power. The most diffused type of Heterostrusture for HEMT is the AlGaN/GaN junction, capable of having great performances in terms of maximum voltage and current.

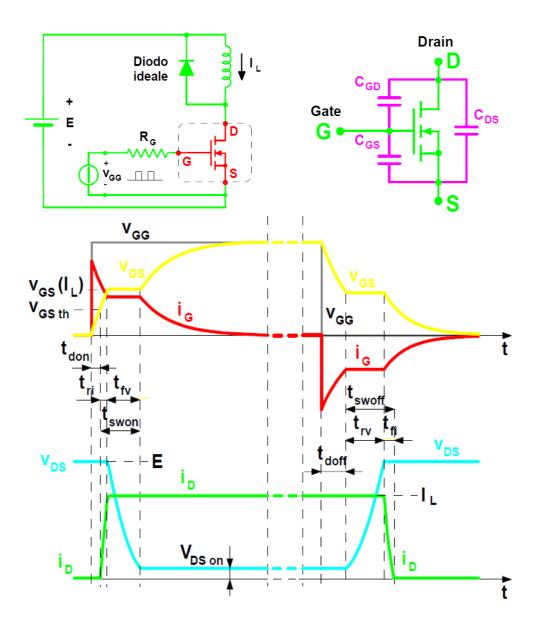

## 1.2 Switching Behaviour and Losses - GaN vs Si

Wide-band-gap semiconductors are expected to be used as materials for new switching devices with low losses and high switching speed, comparing with Silicon. Let us compare GaN HEMTs and Silicon mosfet switching characteristic, in order to understand what are the main differences that make GaN-HEMTs the best as high frequency switching devices. As you can see in figure 1.7, we study the MOSFET switching behaviour thanks to a test circuit that simulates the typical working conditions of the device (in this example, a typical buck converter). We suppose the current  $I_L$ , flowing throw the inductance, to be constant. When  $i_D < I_L$ , a current equal to  $I_L - i_D$ flows throw the ideal diode and  $v_{DS} = E$ . The gate voltage is driven, throw the resistance  $R_G$ , by a square wave voltage that goes from 0V up to  $V_{GG}$ . In order to fully understand the MOSFET's switching behaviour, we must take into account the capacitances  $C_{GD}$ ,  $C_{GS}$  and  $C_{DS}$ , shown in fig 1.7.

When we want the transistor to switch on, the gate driver voltage goes up to  $V_{GG}$ , while the current  $i_G$  charges the capacitances  $C_{GD}$  and  $C_{GS}$  throw the resistance  $R_G$ , then  $v_{GS}$  starts to increase. When, after a delay time equal to  $t_{don}$  (fig 1.7),  $v_{GS}$  reaches the threshold voltage  $V_{GSth}$ , the drain-source current  $i_D$  starts to increase, until reaching the maximum value  $I_L$ , after a delay time equal to  $t_{ri}$ . Then the ideal diode inhibits itself and, since the current  $I_L$  cannot increment anymore,  $i_D$  needs to discharge the capacitances  $C_{GD}$  and  $C_{GS}$  in order to rise, therefore  $v_{DS}$  decreases. In the meantime the gate current  $i_G$  charges the capacitance  $C_{GD}$ , while  $v_{GS}$  remains constant.

Therefore there is a period of time  $t_{fv}$  during which the gate voltage is constant: this behaviour is typical of voltage driven devices, such as MOSFET and IGBT. When  $V_{DS}$  reaches reaches the limit of the ohmic region, that corresponds to  $V_{GSth}$ ,  $v_{DS}$  stops decreasing, whereas  $V_{GS}$  starts again rising up to  $V_{GG}$ . The period of time  $t_{swon} = t_{ri} + t_{fv}$  is called *switching on time*. The integral of the current  $i_G$  gives the total charge  $Q_G$  given to the gate, that depends on the gate voltage and that can be divided into  $Q_{GS}$  and  $Q_{GD}$ , respectively stored in  $C_{GS}$  and  $C_{GD}$ . These charges have a typical value that is related to the type of device and depends on both  $v_{GS}$  and  $v_{DS}$ . During the switching off period, the reverse process occurs.

By studying the MOSFET switching characteristic, we can see that during the switching times, the device need a not negligible gate current  $i_G$ , in order to charge and discharge the capacitance  $C_{GS}$  and most of all  $C_{GD}$ . This current represents a power dissipation, that gets worse with the number of commutations, therefore with the working frequency.

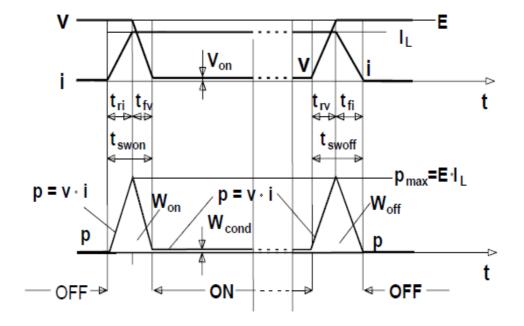

Referring to any component operating in switching mode, the power losses  $(P_l)$  can be mainly divided in two groups:

- Conduction Losses  $(P_c)$  (related to the energy  $W_{on}$  and  $W_{off}$  in fig 1.8)

- Switching Losses  $(P_{sw})$  (related to the energy  $W_{cond}$  in fig 1.8)

Let us see how to calculate the *switching losses* of a silicon MOSFET, in order to compare it with a GaN device [3]:

$$P_{sw} = (E_{swon} + E_{swoff}) * f_{sw}$$

$$(1.1)$$

As for the switching on time [3]:

$$E_{swon} = \int_0^{t_{swon}} v_{DS}(t) i_D(t) dt = E * I_{Don} * \frac{t_{swon}}{2} + Q_{rr} * E$$

(1.2)

where  $t_{swon} = t_{ri} + t_{fu}$ .  $t_{ri}$  depends on the value of the capacitances  $C_{GS}$  and

Figure 1.7: Study of the Silicon MOSFET switching behaviour by using a test circuit with inductive load [7]

Figure 1.8: Switching and Conduction losses for a silicon MOSFET measured inside a circuit with inductive load [7]

.

$C_{GD}$ , whereas  $t_{fu}$  is defined as [3]:

$$t_{fu} = (E - R_{DSon} * I_{Don}) \frac{C_{GD}}{I_{Gon}}$$

(1.3)

Regarding the switching off time [3]:

$$E_{swoff} = \int_{0}^{t_{swoff}} v_{DS}(t) i_D(t) dt = E * I_{Doff} * \frac{t_{swoff}}{2}$$

(1.4)

where  $t_{swoff} = t_{ru} + t_{fi}$ .  $t_{fi}$  depends on the value of the capacitances  $C_{GS}$  and  $C_{GD}$ , whereas  $t_{ru}$  is defined as [3]:

$$t_{ru} = (E - R_{DSon} * I_{Don}) \frac{C_{GD}}{I_{Goff}}$$

(1.5)

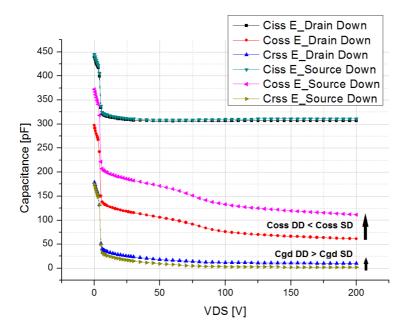

Since the MOSFET's switching losses are defined by the expression 1.1, we can desume the importance of the capacitances  $C_{GS}$  and  $C_{GD}$  in the MOS-FET's switching behaviour. The switching losses are as negligible as the capacitances  $C_{GS}$  and  $C_{GD}$  are small, where  $C_{GD}$  has the main role.

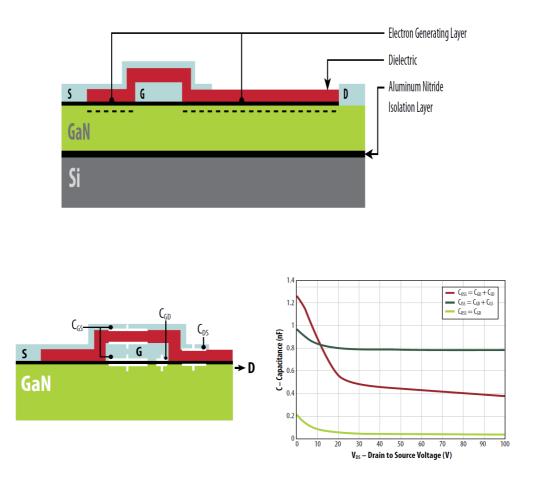

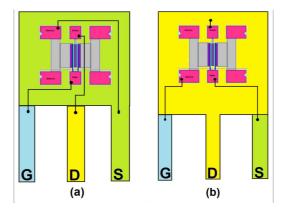

The strength of GaN-HEMTs are the very low values of the capacitances  $C_{GD}$ ,  $C_{GS}$  and  $C_{DS}$  in comparison with silicon MOSFETs. In the following an EPC device (fig 1.9) is shown as an example. As you can see in figure 1.9, thanks to the lateral structure, the capacitance  $C_{GD}$  comes only from a small corner of the gate: an extremely low  $C_{GD}$  leads to a very rapid voltage switching capability.  $C_{GS}$  consists of the junction from the gate to the channel summed to the capacitance of the dielectric between the gate and the field plate. $C_{GS}$  is large when compared to  $C_{GD}$ , giving GaN transistors excellent dV/dt immunity, but it is still small when compared with Silicon MOSFETs, giving them very short delay times and excellent controllability in low duty cycle applications . The lateral structure of the GaN transistor makes it a very low charge device: it has the capability of switching hundreds of volts in nanoseconds, giving it multiple megahertz capability. This capability will lead to smaller power converters and higher fidelity class D amplifiers [2].

As for the *conduction losses*  $(P_c)$ , they can be calculated by using a

Figure 1.9: Values and locations of physical capacitances inside an EPC device [2]

•

MOSFET-approximation with the drain-source on-state resistance  $(R_{DSon})$ [3]:

$$v_{DS}(i_D) = R_{DSon}(i_D) * i_D \tag{1.6}$$

where  $v_{DS}$  and  $i_D$  are the drain-source voltage and the drain current respectively. Therefore, the instantaneous value of the MOSFET's conduction losses is [3]:

$$p_C(t) = v_{DS}(t) * i_D(t) = R_{DSon} * i_D^2(t)$$

(1.7)

The integration of the instantaneous power losses over the switching cycle gives an average value of the MOSFET's conduction losses [3]:

$$P_C(t) = \frac{1}{T_{sw}} \int_0^{T_{sw}} p_C(t) dt = R_{DSon} * i_{Drms}^2$$

(1.8)

where  $i_{Drms}$  is the rms value of the MOSFET's on-state current.

As we can see from these formulas, the conductive losses are directly proportional to  $R_{DSon}$ .

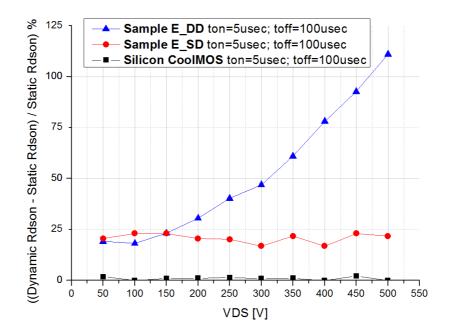

Therefore, for a switching device, it is very important to have a very low  $R_{DSon}$ , in order to minimize the conduction losses. Now the reason why GaN HEMTs particulary fits high frequency applications is clear, but unfortunatelyGaN suffers from current collapse, that is responsible for an increase of the Rdson in dynamic mopde during the switching on, due to trapping effects at the surface or/and in the buffer. The increase in the Rdson means an increase in the conduction losses. In section 3.4.1 we will introduce the method for calculating the Rdson in Gan HEMTs and how to compare the dynamic  $R_{DSon}$  value with the static  $R_{DSon}$  one, in order to evaluate the presence and, possibly, the level of current collapse.

## Chapter 2

# GaN-HEMTs - Structure and Operating Principles

### 2.1 GaN Crystal Structure

In order to better understand the origin for of GaN's benefits, listed in section 1.1, the crystal structure and the band structure will be discussed in the following part.

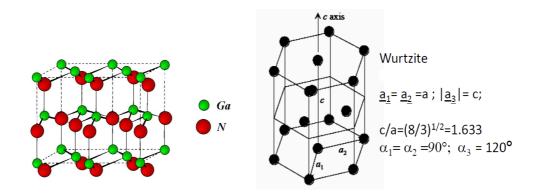

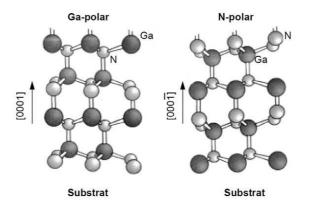

Gallium Nitride (GaN) is a compound semiconductor, formed by an atom of Gallium (Ga), an element of the III group on the periodic table, and by an atom of nitrogen (N), that belongs to the V group. GaN crystal structure is shown in fig. 2.1.

GaN, as well as other III nitrides-group, can crystallize into wurtzite, zincoblende or rocksalt structure; in ambient conditions the thermo dynamical stable structure is wurtzite for bulk GaN, AlN or InN, therefore the most common used crystal structure in devices is wurtzite, which has a hexagonal unit cell and thus two lattice constants, c and a (fig. 2.1); this crystal structure consists of two interpenetrating hexagonal close-packed lattices, which are shifted with respect to each other.

Figure 2.1: GaN Crystal Structure (left) and Wurtzite Unit Cell (right)

### 2.2 The Concept of Heterostructure

The possibility of building heterostructures enables the fabrication of GaNbased High-Electron-Mobility-Transistors (HEMTs), thus we would like to briefly introduce the concept of heterostructure.

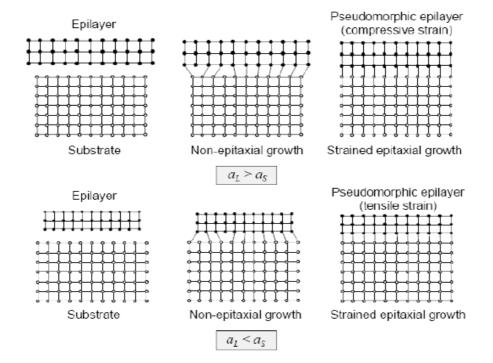

The heterostructures are junctions between materials with different Energy Gap and some other different proprieties. They are obtained by growing a certain type of crystal (epilayer) on another crystal (substrate) with a different lattice constant (fig. 2.2); this type of process is called *heteroepitaxy*. If the lattice constants are similar enough, so that the amount of defects at the iterface between the two materials is negligible, we will obtain a so called *heterostructure*; vice versa, if the lattice constants are extremely different, so that the amount of defects is prettly big, at the interface we will find defects called *misfit dislocations*, who will act as traps for electrons.

Heterostructures let us obtain particular electrical and optical proprieties, thanks to the electrical and optical confinement. They are used in order to build new devices, such as bipolar transistors, FET, LED, laser, photodetectors etc.

Figure 2.2: Hepitaxy. Compressive and Tensile Strain.

## 2.3 HEMT's - Structure and Operating Principles

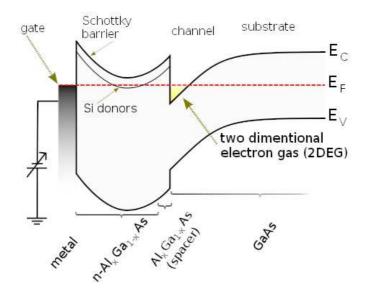

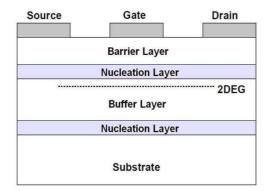

The HEMT, High Electron Mobility Transistor, are transistors with high electron mobility, based on a heterostructure between high band gap semiconductors. The high electron mobility value is related to the way in which the channel is formed: the channel is not formed on a doped semiconductor, but on a intrinsic one: in this way the mobility cannot decrease due to the scattering phaenomena between electrons and doping elements. These kinds of devices are built with a heterostructure that let us take advantage of the high carrier concentration of a doped semiconductor and the high mobility of the not doped one, where the carriers are collected.

The HEMT's fundamental element is the heterostructure, composed by a *buffer layer* (GaAs in fig.2.3), on which we deposit a so called *barrier layer* (AlGaAs in fig.2.3), doped with donors, with the aim of providing carriers. In order to build the heterostructure, we put two materials with different energy gaps closed together: at the interface a conductive channel is formed, thanks to the bands bending (fig. 2.3). The buffer layer conductive band goes down under the Fermi level, so making free a lot of electrons in the conduction band. Now carriers are confined inside the quantum well created by the bending bands. We have formed a channel where carriers can move only along the interface between the two semiconductors; the carriers in the channel are able to move only in two directions, thus the channel is called *Two Dimensional Electron Gas* (2DEG).

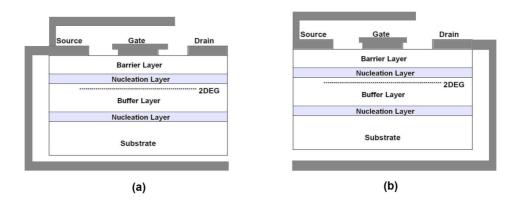

By applying voltage to the device, a high quantity of current is passing, thanks to the absence of scattering phaenomena between ions and doping impurities, thus we find mobility values comparable with the ones of the instrinsic material. The heterostructure is usually grown on a substrate, a material suitable for hepitaxial growth, and, in order to reduce the mismatch between buffer and substrate and thus the formation of defects, we can insert a thin layer called *nucleation layer* (fig 2.4). We can find a nucleation layer also between buffer layer and barrier layer, in order to support the carriers confinement and to increase the electron mobility.

Figure 2.3: Band Diagram of an AlGaAs/GaAs Heterostructure [25].

Figure 2.4: HEMT's Typical Structure [25].

### 20CHAPTER 2. GAN-HEMTS - STRUCTURE AND OPERATING PRINCIPLES

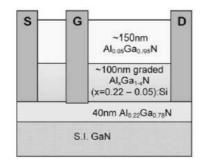

Nowadays the most studied heterostructure is the AlGaN/GaN one, that thanks to GaN peculiarities, gives birth to a very high carrier concentration at the interface, even with an undoped barrier layer. GaN based HEMT's way of working is similar to the one described above, but, by comparing with the GaAs-based devices, GaN-HEMT's presents a different channel's formation mechanism.

In order to understand how the 2DEG is formed in GaN-HEMT's, we need to briefly introduce the concept of spontaneous and piezoelectric polarization, without which the channel could not be formed [27].

### 2.3.1 Polarization

One of the most important properties for wurtzite III-nitrides group, like GaN, is that these materials exhibit an internal field caused by the spontaneous polarization (fig 2.5).

$$E = \frac{P}{\epsilon} \tag{2.1}$$

where P and  $\epsilon$  stand for the Polarization vector and the dielectric constant respectively [10].

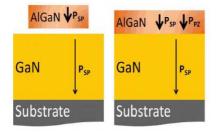

In the III-nitride crystals, for example InN, GaN and AlN, the crystal cell does not correspond to the ideal wurtzite's cell: there is a change in the position of positive and negative ions comparing with the ideal ones, due to the difference in electro negativity between the elements that belong to group-III and group-V; this phaenomena is called **Spontaneous Polarization** and it does not exist in materials with Zincoblenda' structure such as GaAs. Moreover GaN is characterized by high piezoelectric constants, so that we can find also a **Piezoelectric Polarization** effect, that, together with the spontaneous one, is fundamental for GaN devices, in order to let them work correctly. Piezoelectric Polarization effects are visible when GaN is put in contact with a material that show different lattice constant: in this way the forces at the interface between the two materials, caused by the lattice mismatch, are transformed into Piezoelectric Polarization, that, depending on the type of strain (compressive or tensile), can be directed in one direction or in the opposite one. In heterostructures such as AlGaN/GaN for example, AlGaN layer is subjected to tensile stress.

Thanks to his polar nature, GaN crystal may have two types of surfaces: one formed by Gallium atoms, Ga-face, and one formed by Nitrogen atoms, N-face. As it is shown in fig. 2.5, if the surface is of the type Ga-face, then the polarization vector is coming out from the surface, vice versa the vector is directed inside the surface.

When the AlGaN barrier layer is deposited on the GaN buffer layer, the piezoelectric polarization appears; this phaenomena is as much considerable as much important is the mechanical strain that the epilayer has to support. The stress between GaN and AlGaN is 5 times more than between AlGaAs

Figure 2.5: GaN Polarization [28].

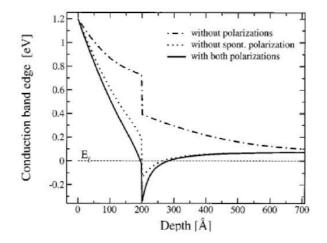

and GaAs. In case of tensile strain, the vectors spontaneous and piezoelectric polarization are parallel and have the same verso, whereas they are opposed in case of compressive strain. As you can see in fig 2.6, these two types of polarization (only if they both are present) give birth to a quantum well on the low edge of the conduction band.

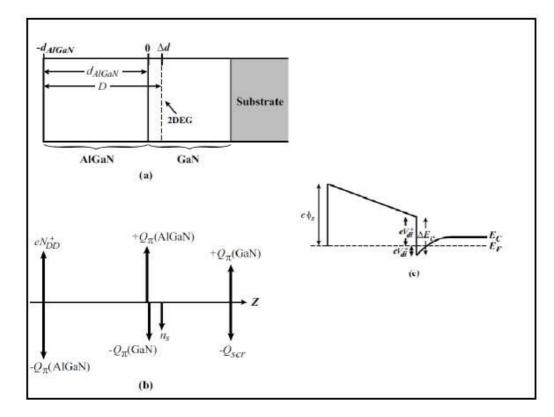

The different magnitude of the vector polarization in the two materials leads to a high negative charge concentration at the interface; the difference of band gap between the two materials make these electrons be confined in GaN. 2DEG channel is created thus without doping and without applying positive voltage: at the interface the carrier concentration is more or less  $10^{13} cm^{-2}$ [?], which is more than ten times higher than in the doped AlGaAs/GaAs counterpart, so that GaN polar charge can be considered equivalent to a 2D distribution. In order to have the best carrier confinement, spontaneous and piezoelectric polarization must have the same direction. We can discuss about what are the best conditions for the 2DEG formation, depending on which one is the exposed GaN face: if the Ga-face is exposed, the best situation is when AlGaN is grown on GaN, because AlGaN is suffering from tensile strain, so that piezoelectric and spontaneous polarization vectors are aligned (fig. 2.7).

If the N-face is exposed, vice versa, we could consider the best situation to

Figure 2.6: Conduction Band Bending for different values of Spontaneous and Piezoelectric Polarization Vectors (After Ambacher et. al. J. Appl. Phys. 1999).

be when GaN is grown on AlGaN, so creating a compressive strain; but in this case the vectors have opposite directions, so that the collected charge is much more smaller. Thus we can say that, by growing AlGaN on GaN (Ga-face), we can have the most populated 2DEG [25].

Figure 2.7: Spontaneous and Piezolectric Polarization Vectors in AlGaN before (on the left) and after (on the right) Heteroepitaxy.

## 2.3.2 The Role of Surface's Holes and Donors in the 2DEG Formation

After have explained the mechanisms that lead to the channel formation, it is necessary to comprehend where this huge amount of carriers comes from.

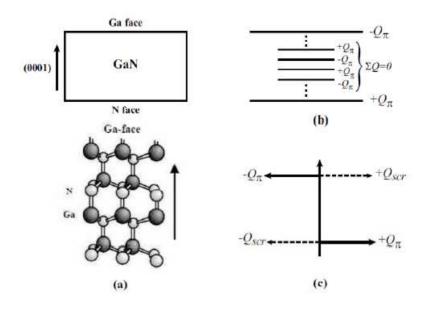

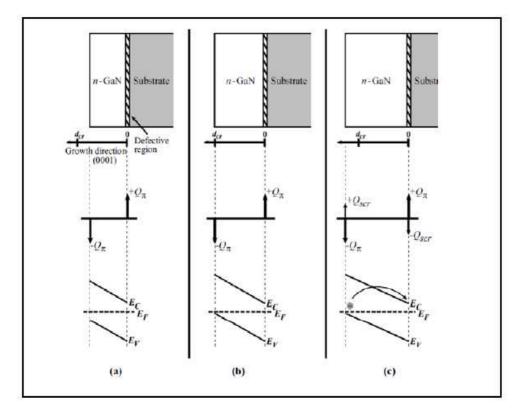

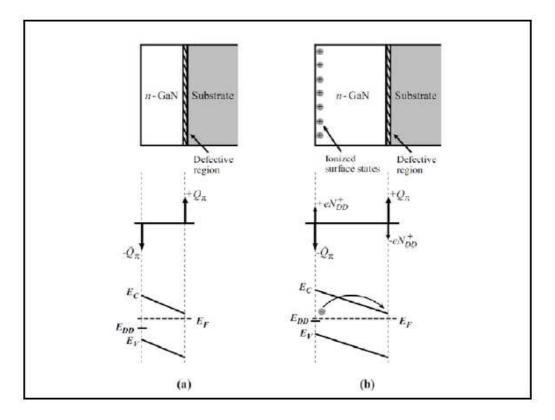

In fig. 2.8 it is shown how the polarization works in GaN ; inside the material positive and negative polar charges compensate each others, whereas on Ga-face and on N-face the polar charge is clearly present ( $-Q_{\pi}$  on Ga-face and  $+Q_{\pi}$  on N-face) [10].

Figure 2.8: GaN Polarization and Polar Charge Compensation [10].

Actually there are some mechanisms tryng to let the system reach an equilibrium status, by compensating the polarization:

#### 1. Holes generation at the Surface

### 2. Donor States at the Surface

We believe holes and donor states at the surface to be the source of electrons for the 2DEG formation. According to this theory, the amount of charge in the 2DEG can be modifyied by varying GaN thickness.

#### 1. Holes Generation at the Surface

Figure 2.9: Holes Generation at the Surface [10].

When the GaN layer grows over the critical distance  $d_{cr}$  (fig. 2.9), the valence band  $E_v$  crosses the Fermi level, generating electron-hole pairs; the so generated electrons enter the conduction band, thus creating an additional charge  $(+Q_{scr} \text{ and } -Q_{scr})$  in order to compensate the polarization charge $(-Q_{\pi} \text{ on Ga-face and } +Q_{\pi} \text{ on N-face respectively})$  [10].

#### 2. Donor States at the Surface

Figure 2.10: Donor States at the Surface [10].

On the GaN surface it is possible to deposit some donors states; they can be represented as allowed states inside the not allowed Energy Gap (fig. 2.10). If the GaN layer is large enough to let the energetic level of the donor states cross the Fermi Level, by letting electrons be free. The so generated electrons enter the conduction band, thus creating an additional charge ( $+Q_{scr}$  and  $-Q_{scr}$ ) in order to compensate the polarization charge ( $-Q_{\pi}$  on Ga-face and  $+Q_{\pi}$  on N-face).

While AlGaN thickness is growing, the carrier concentration in the 2DEG  $(n_s)$  grows fastly, until the buffer reaches the crytical thickness, then it does not increment anymore, but it even goes a bit down, due to crystal relaxing after mechanical strain [10].

27

Figure 2.11: GaN HEMT's - 2DEG Formation [10].

In fig. 2.11 the structure, the polar charges and the band diagram of an AlGaN/GaN-HEMT are shown. Both GaN and AlGaN show polar charge at the surfaces (fig.2.11(b)). When the surface states are ionized  $(eN_{DD}^+)$ , their charge is compensated by the generation of an additional charge in AlGaN :  $n_s$  and  $-Q_{scr}$ . Referring to (fig.2.11(b)), we can write the following equation, by using the charge balance principle [10]:

$$qN_{DD}^+ = +Q_\pi(GaN) + n_s \tag{2.2}$$

where  $n_s$  represents the conduction channel inside the GaN-HEMT; this channel is actually a quantum-well (fig.2.11(c)) ,where electrons can freely move along two directions; for this reason it is called 2DEG (Two dimensional Elecron Gas). The 2DEG is formed only thanks to polarization mechanisms, thus doping is not needed, whereas in the AlGaAs/GaAs system the charge in the channel is given by the doping.

As we said in section 1.1, the presence of a 2DEG in GaN-HEMT leads to a high maximum drift velocity (fig.1.4) and a relatively high electron mobility (fig. 1.3) ,thanks to the absence of scattering phaenomena between carriers.

# Chapter 3

# **Current Collapse**

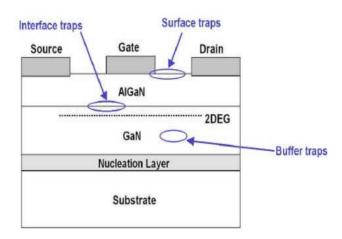

One of the major effects that continues to limit the performance of GaNbased devices is the presence of electronic traps in the device structure. It has been proven that in AlGaN/GaN HEMTs the 2DEG in the channel is affected by the parasitic charge moving in and out of the traps on the surface and/or in the bulk of the heterostructure. GaN based-HEMT's are used for high power and high frequencies applications; this effect is thus really important and considerably limits the performances of this kind of devices: it is important to understand the origin of the traps in GaN-based transistors, their location, and the physical mechanisms involved, in order to optimize the device's performances.

### 3.1 Traps

Traps can be caused by defects in the material, that can be related to crystal defects, polluting agents and the mismatch between the different layers. At the interfaces between different materials and at the materials surfaces the periodicity of the crystal lattice ends and creates unbonded bonds. As for the band diagram, these defects are represented by allowed states inside the not allowed band gap: the so called *traps*. HEMT are built throw layers with different lattice constant and they are hepitaxially grown one on the other one, so that the trapping phenomenon is really significant. Traps create

a quasi-static charge distribution both on the wafer surface and inside the buffer below the channel : this leads to a reduction in the drain current and therefore to a limitation in the maximum output power at high frequencies. Moreover these states bring a delay in the device's performances, thanks to the trapping-detrapping effects, therefore limiting the maximum operating frequency. HEMT are widely used for microwave power amplifiers, for this reason the development of these devices has been strongly limited by this phenomenon.

In AlGaN/GaN HEMTS's traps can be set at the surface, inside the AlGaN, at the AlGaN/GaN interface or inside the buffer layer (fig.3.1). Depending

Figure 3.1: HEMT's Typical Traps Setting [25].

on the traps' location inside the device, they show different effects. Even if a considerable research effort has been directed towards the identification and elimination of traps in AlGaN/GaN HEMTs, the trapping processes in GaN are still not completely understood [21] [29].

### 3.2 Current Collapse

The main non-ideality of interest in GaN HEMTs has been variously referred to as current collapse, transconductance frequency dispersion and current slump. This is the most important problem that impacts GaN FET technology for high power applications. Current collapse is essentially the observation that the measured output power of the device at the frequencies of interest such as 4-18 GHz, is considerably smaller than that expected based on the equation

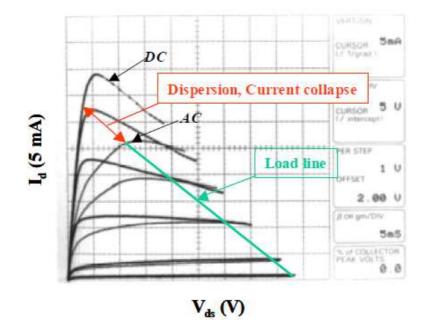

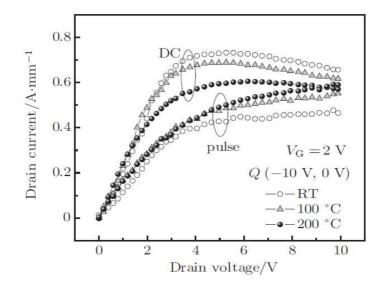

$$P = 1/8 * IDS_{MAX} * (V_{BREAKDOWN}) \tag{3.1}$$

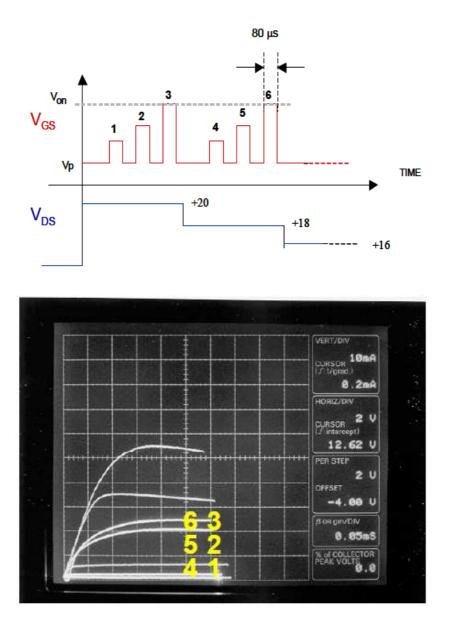

where the values of  $IDS_{MAX}$  and  $V_{KNEE}$  are based on the values measured at DC. In fig 3.2 we show the measured DC and pulsed I-V characteristics, typical of a GaN HEMT that exhibits current collapse. The DC curves are measured using a Tektronix curve tracer. The pulsed measurements are made using the pulsed mode of the Tektronix curve tracer where the sequence of drain and gate biases is shown in figure 3.3 [Veturi 2000]. As can be seen from figure 3.2, there is a considerable reduction in the drain current, together with an increase in knee voltage, when measured under pulsed conditions. Current collapse is caused by the presence of deep levels or traps located in the device structure [28].

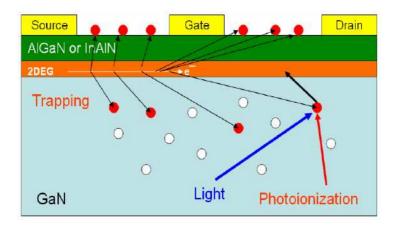

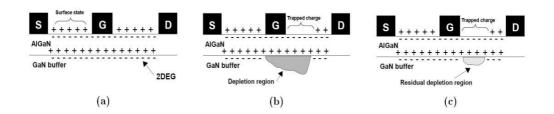

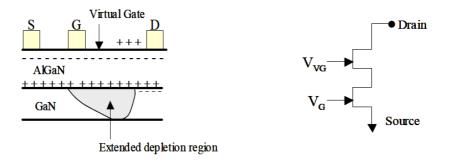

This phenomenon can be explained by considering that, when the transistor in normally operating and the channel is formed, the surface states behave as donors and their electron moves to the channel. In this way a positive charge distribution is formed on the AlGaN surface, in order to compensate the 2DEG's charge. If on the external surface there are electrons, this charge will be partially neutralized, so that we will see an electron's number reduction in the channel and an enlargement of the depletion region. When the channel is closed, infact, due to the high electrical field between gate and drain, the surface states are filled with negative charges coming from the gate. When the channel is opened again, the surface states are not able to come immediately back to the channel, because the trapping-detrapping

Figure 3.2: Typical DC and Pulsed I-V Characteristic of a GaN HEMT [28].

speed is much more smaller than the channel's formation speed (fig 3.4). This phenomenon brings an accumulation of negative charges, that keep the channel partially off, so that we can see a reduction in the drain current comparing to DC (fig.3.5). The current collapse effect is now explained by using the concept of **virtual gate** [28]: as for this model, a second gate electrode is inserted in series with the real one; the real gate is driven by the applied voltage, whereas the virtual one is driven by the quantity of charge trapped at the surface (fig. 3.6). The drain current is related to both the real gate's voltage and the mechanisms regulating the virtual gate's charge's movement. If we want the current to reach the nominal value, we can use a light source that, thanks to photons wiht energy higher than the GaN energy gap, gives birth to hole-electron pairs in the buffer layer. Holes are therefore moved by the electric field towards the surface, in order to make it positive biased and to eliminate the virtual gate. Nowadays some technics are used in order to eliminate the current collapse: the most common is the **surface** passivation, that is the deposition of a passivation film on AlGaN(fig.3.7),

Figure 3.3: Sequence of Pulses used to obtain the Pulsed I-V Curves [28].

Figure 3.4: Schematic charge movement in and out of the traps on the surface and/or in the bulk of the heterostructure [18].

Figure 3.5: The Transconductance Frequency Dispersion Phaenomen in GaN HEMTs [11].

Figure 3.6: Model of device showing the Location of the Virtual Gate [28].

used in order to make superficial defects inert. The most common passivation

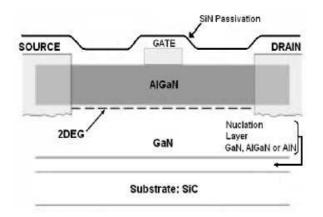

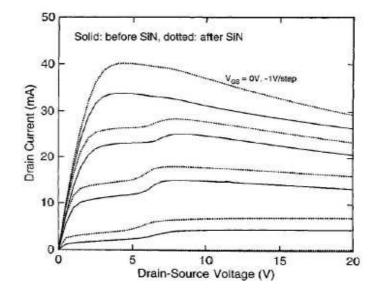

Figure 3.7: Surface Passivation on AlGaN/GaN HEMT [27].

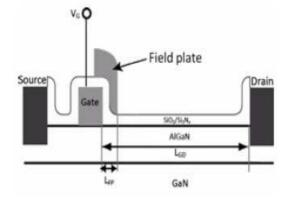

material is Silicon Nitride  $(Si_3N_4)$ . We build an almost perfect insulating material-semiconductor interface, in order to neutralize the superficial charge caused by unbonded bonds, defects, residual charges and to prevent electrons from reaching the surface. The final result depends on elements such as the surface, the quality of the material and the deposition process. In figure 3.8, it is shown the effect of SiN passivation on the DC characteristic: you can see how the passivation makes the current value increase, but without eliminating the current collapse effect. Another strongly diffused method, in order to reduce the current collapse, is the adoption of a field plate. This technique modifyies the gate's layout: in particular the gate has a T or  $\Gamma$ shape, in order to partly cover the gate-drain area (fig. 3.9). The field plate gives us the possibility of reducing the maximum electric field between gate and drain, that is the main reason for charges to move from the gate towards the surface. The field plate infact limits the electric field peak and by makes it more homogeneous along all the field plate's length. We can find a huge benefit also in terms of device's degradation after stress: infact the electric field gets lower and the electrons are less sped up, so that all the degradation processes, linked to the presence of hot electrons, decrease. The field plate's design depends on elements such as length, thickness and type of material.

Figure 3.8: Drain Current before (solid line) and after (dotted line) Passivation [?].

Figure 3.9: Field Plate in AlGaN/GaN HEMT.

Another Technique, called Gate Recess, is shown in figure 3.10 and it lets

Figure 3.10: Gate Recess Structure [?].

us limit the superficial traps effects. The barrier layer is moved more deeply: in this way it is set under the AlGaN and Gan layers, in order to push the surface away from the channel, therefore limiting the current collapse effects, even without passivation.

In order to make the current come back to the nominal value, we can highlight the device: the light source must have an energy level closed to GaN energy gap or closed to the trap's activation energy. If it is possible to use light sources with different wavelength, we can find out the energy of every trap, by understanding which wavelengths are related to current recovery phenomena; moreover the time necessary to the current recovery gives us information about the traps' nature.

I will give an overview of the two electrical characterization techniques used to investigate the various trapping effects in GaN-based HEMTs. These techniques are commonly known as drain lag and gate lag experiments and allow us to discriminate between lateral and vertical trapping phenomena.

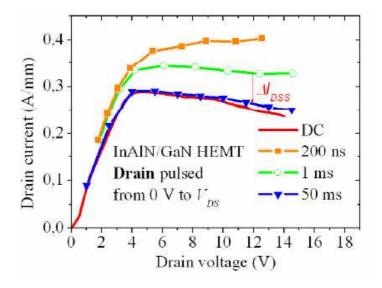

### 3.3 Drain Lag

A significant reduction in the drain current resulting from the application of a high drain-source bias voltage is known as drain lag (fig 3.11). The term drain lag is used to describe the transient in the drain current when the drain voltage is pulsed, while the gate voltage is held constant (fig 3.12) [28]. The drain lag effect is supposed to be associated with traps located in the buffer layer and in the substrate. GaAs devices are usually fabricated on semi-

Figure 3.11: Drain-lag output characteristics of an InAlN/GaN HEMT with different pulses (1 ms 50 ms and 200 ns) and in DC. The drain is pulsed from 0 to VDS and the gate is grounded [18].

insulating substrates, which provide good isolation between devices in ICs and minimize parasitic capacitances. However, the semi-insulating nature of the substrate is achieved by impurity compensation by deep levels, which can give rise to transient effects. Although the surface trapping effects cause transient effects in drain currents, even devices with single and double gate recesses and passivated surfaces have exhibited drain current transients. For this reason, drain lag effects are commonly attributed to the substrate trapping effects too [28]. Binari et al. [22] were the first to correlate drain current collapse in GaN-based MESFETs with hot electron trapping by deep traps in the highly resistive GaN buffer layer. Further studies by Binari et al. [24] [23] suggested that the degree of the drain lag is related to the conductivity of the GaN buffer, which can be strongly influenced by the growth pressure. By studying the wavelength dependence of the drain current recovery in more details, no enhancement of the optically induced drain current recovery was observed for photon energies at or below the AlGaN bandgap. It seems to be obvious that the drain lag in AlGaN/GaN HEMTs is caused by the same traps in the highly resistive GaN buffer layer that also is responsible for the drain lag in the GaN MESFETs [15] [14].

Figure 3.12: Drain-lag measurement schematic [6].

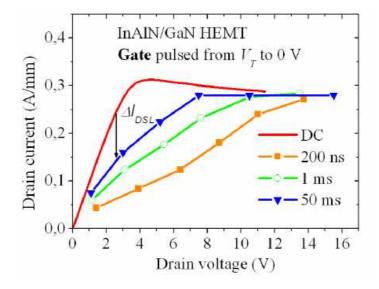

### 3.4 Gate Lag

The term gate lag is used to describe the slow transient response of the drain current when the gate voltage is pulsed [Veturi 2000] (fig 3.13). Figure

Figure 3.13: Gate-lag output characteristics of an InAlN/GaN HEMT with different pulses duration (1 ms 50 ms and 200 ns) and in DC. The gate is pulsed from VT (off-state) to VGS (on-state) and the drain is DC biased. Gate-Source voltage is VGS=0 [18].

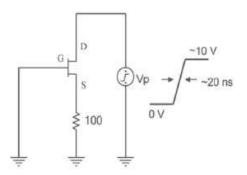

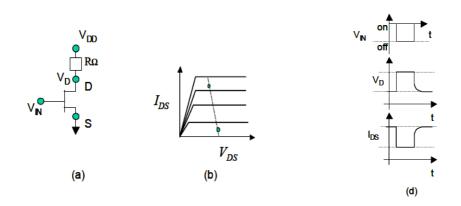

3.14(a) shows the measurement schematic used to quantify gate lag. Fig 3.14(b) shows the movement of the device on the I-V plane. The FET is biased in common source mode and the gate voltage is pulsed from the pinch-off (or a negative value) to a varying final values. A low value of the drain load resistor is usually chosen to keep the drain voltage variation small and to avoid any effects caused by variation in substrate trap densities due to drain voltage variation. Fig 3.14(d) shows the sequence of input pulses and output responses. We refer to as *lag* if, when the gate is pulsed ON, the drain current is larger than its steady state and the drain current slowly reaches its steady state value. This phenomenon is attributed to both surface state as well as substrate deep trap effects. Various research groups have confirmed that drain current reduction during large signal operation at microwave fre-

#### 3.4. GATE LAG

quencies is mainly caused by electrons trapping phenomena at the unpassivated barrier surface. The effect of the surface states was explained for the first time by Ventury, where they used floating gates as potential probes to directly measure the surface potential along the gate-drain access region suggesting the presence of negative charges on the surface. This negative charges are responsible for a more negative surface potential which leads to a rapid extension of the gate depletion region [28].

Figure 3.14: Schematic of Gate Lag Measurement [28].

#### 3.4.1 Dynamic Rdson Measurement

As we said in section 3.4, the term gate lag is used to describe the slow transient response of the drain current, when the gate voltage is pulsed. As we can see in fig 3.13, the gate lag phenomen can also be defined as an increase in the dynamic Rdson value (measured under pulsed conditions), comparing to the static Rdson value (measured in steady state). According to this point, we can quantify the current collapse in the following way: we fix the value of the drain-source current to an arbitrary value, belonging to the linear region of the I-V characteristic; we monitor the  $v_{DS}$  drop between drain and source, under pulsed conditions, and we compare that with the  $v_{DS}$  drop measured in steady state. If  $Vds_{DYNAMIC} > Vds_{STATIC}$ , we will

have current collapse: according to the following expressions,

$$Rdson_{DYNAMIC} = \frac{Vds_{DYNAMIC}}{IDS}Rdson_{STATIC} = \frac{Vds_{STATIC}}{IDS}$$

(3.2)

in case of current collapse, since the drain-source current is constant, it will be  $Vds_{DYNAMIC} > Vds_{STATIC}$ , because  $Rdson_{DYNAMIC} > Rdson_{STATIC}$ . Therefore, when the gate voltage is pulsed, we can quantify the current collapse by monitoring the transient response of the  $v_{DS}$  drop between drain and source in on-state. As we said in sec 3.2, when the voltage applied to the drain of the device gives birth to an electric field between drain and gate big enough to let some electrons escape from the channel and be captured inside traps, then we will have current collapse: it will be  $Rdson_{DYNAMIC} > Rdson_{STATIC}$ and so, thanks to our measurement setup, we will measure in increment in the vds value directly proportional to the degree of current collapse.

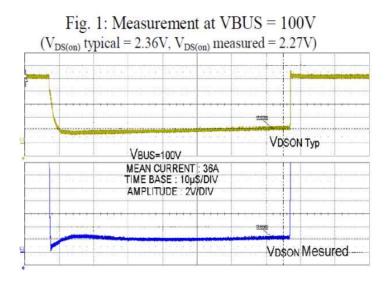

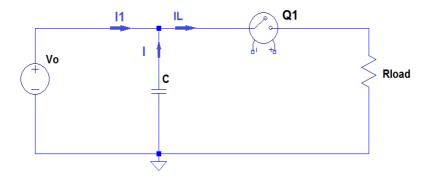

In fig 3.15, on the top, is shown the basic schematic we used for the Dynamic Rdson Measurements.

The gate is driven by a pulse generator, whereas the drain potential is held to a fixed voltage, given by the battery in parallel with the capacitance. The capacitance contributes to maintain the drain-source voltage at the value imposed by the battery, by avoiding any voltage over-undershoot coming from the battery. The drain resistance RD is used to fix the current that the device has to support. In fig 3.15 you can see the I-V characteristic of the device and the load line related to the drain resistance RD.

While the gate voltage is pulsed, the device continuously switches from on to off-state. When the device is on, it works in the linear part of the I-V characteristic; in particular, the working point is represented by the intersection between the load line and the vertical axis. The drain-source current is fixed throw the drain resistance RD and is equal to  $IDS = \frac{VDD}{RD}$ , where VDD is the voltage applied by the battery to the drain of the device. The drain-source voltage drop, on the other side, is very small in this working point. When the device is in off-state, it works in the point in which the load line intersects the horizontal axis: ID = 0 and VDS = VDD.

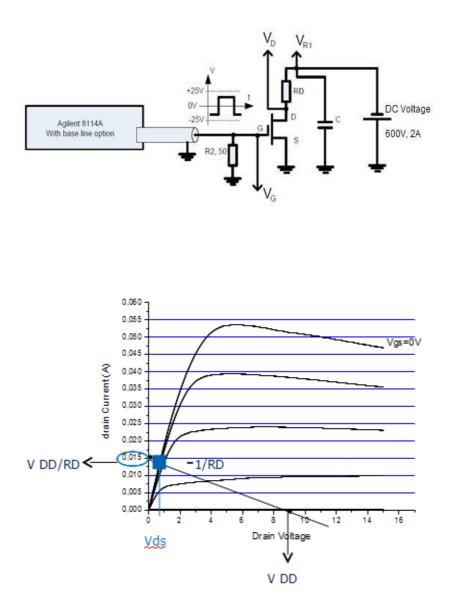

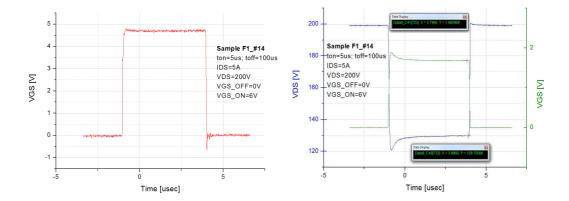

Fig 3.16 shows how the Scope Screen appears during a Dynamic Rdson

Figure 3.15: Dynamic Rdson Measurement Basic Schematic (on the top); output characteristic (on the bottom) with the load line related to the drain resistance RD.

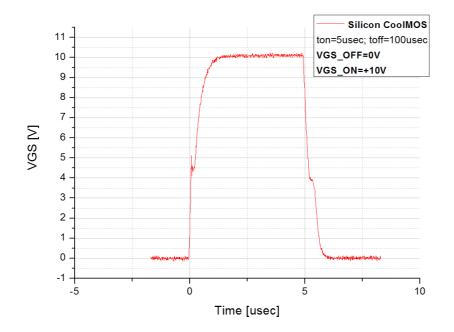

Measurement. The gate voltage (yellow line) is pulsed from 0V to 5V, in order to keep the transistor switched on for a period of time equal to (i.e.  $ton = 5\mu s$ ). The ton time chosen for the measurement depends on the application, therefore it is connected to the range of frequencies at which the device is supposed to operate.

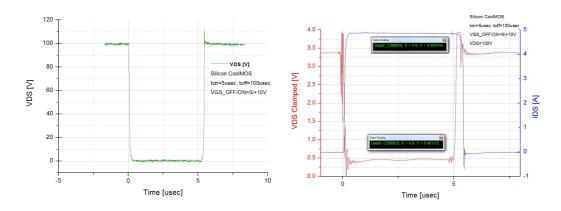

When the device turns on, the drain-source current (purple line) goes up to the drain-source current value fixed throw the drain resistance RD, (in the example it is IDS = 900mA). The drain voltage (blue line) is equal to the voltage on the battery (VDD=450V) when the transistor is off, whereas it is very small when the device is turned on.

When the device is in off-state, the  $v_{DS}$  drop between drain and source is big, therefore we have an high electric field between drain and source, that let some electrons come out from the channel and be captured inside traps, mostly on the surface of the device (sec 3.2), even if a trapping effect in the buffer cannot be excluded. The toff time is therefore also referred to as *stress time*. The longer is the stress time, the bigger is the number of electrons trapped and the more it takes, when the device is switched on, to detrap them and let them free to come back to the channel.

When the gate voltage pulse opens the channel again, the electrons need some time to be detrapped: the current does not immediately reach the final value, but it takes a bit longer. This delay time is called *recovery time*. In our type of measurement the current is fixed, so that, by monitoring the drain-source voltage in on-state, we will see that it does not immediately rise to the final value, but it slowly decrements until reaching that. The period of time the drain-source voltage takes to reach the final value representes a limitation for the device: it stands for the maximum frequency at which the device can operate.

Figure 3.16: Scope Screen. Example of Dynamic Rdson Measurement. Vgs (yellow line), Vds (blue line), Id (purple line)

# Chapter 4

# **Clamping Circuit**

### 4.1 Problems Related with the Scope's Resolution

The resolution of an instrument is defined as the minimum value that the instrument is able to evaluate. In order to obtain an accurate measurement, it is important to have as much resolution as possible.newline Referring to the scope, both vertical and horizontal resolution are defined; they are related to the vertical and horizontal number of divisions of the scope, respectively.

The scopes vertical resolution is related to the number of quantization levels of the ADC converter inside the scope; it is defined as follows:

$$Vertical Resolution = R = \frac{VBUS}{2^b} = \frac{VBUS}{2^8} = \frac{VBUS}{256}$$

(4.1)

where VBUS indicates the maximum voltage value of the signal to be measured, whereas "b" stands for the number of bit of the ADC converter, usually equal to 8 in digital scopes; this means that the read signal is quantized on  $2^8 = 256$  levels.

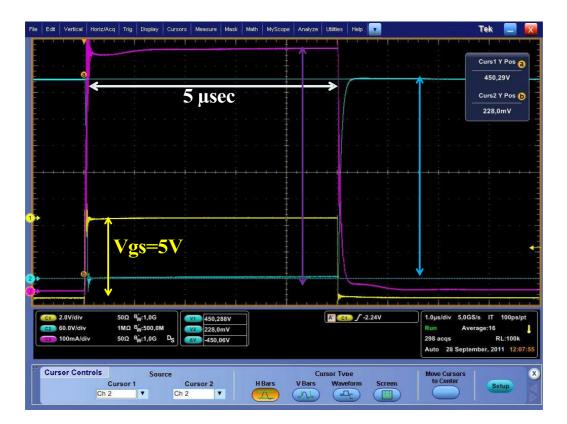

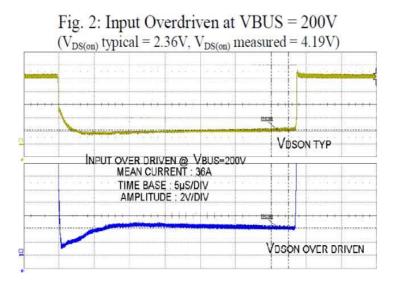

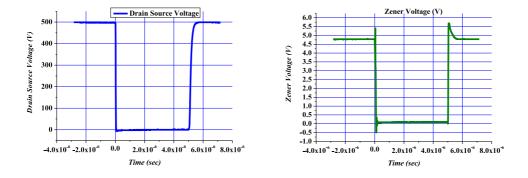

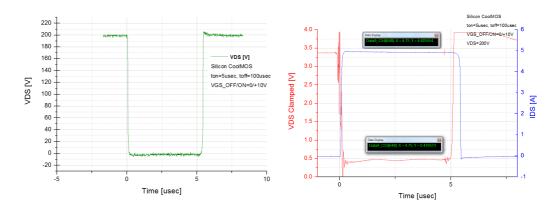

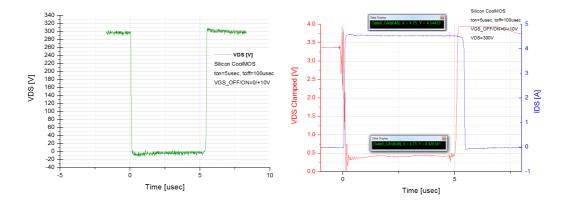

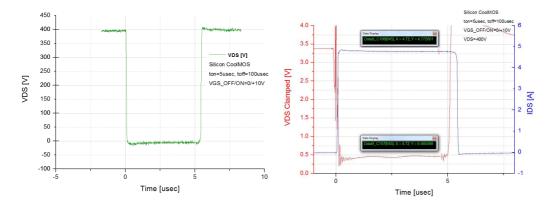

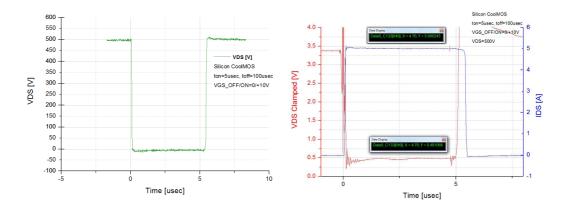

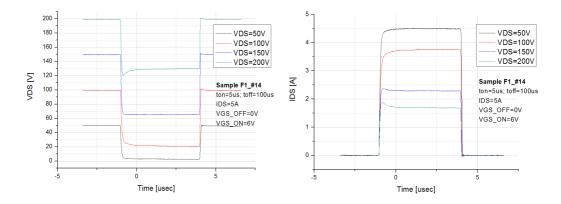

In fig 4.1, 4.2 and 4.3 you can see the drain-source voltage signal of a silicon MOSFET, measured under pulsed conditions and stressed with different values of drain-source voltage in off-state(VBUS) [4]. The yellow waveforms on the top indicate the typical and correct signals we should see on the scope's screen, whereas, in the graph on the bottom, the blue waveforms indicate the signals we actually measured. We want to evaluate the value of the drain-source voltage drop in on-state in corrispondence with the end of the  $v_{GS}$  pulse (fig 3.16); for example, referring to fig 3.16, if the vgs pulse lasts  $5\mu sec$ , we will evaluate the degree of current collapse at  $f = \frac{1}{5\mu sec} = 200 KHz$ .

Figure 4.1: Problems with the vertical resolution of the scope.  $R = \frac{VBUS}{256} = \frac{100V}{256} = 390mV$ : at VBUS=100V the  $v_{DS}$  measured is correct [4].

As for fig 4.1, the right  $v_{DS}$  value we should measure is  $v_{DS} \approx 2.36V$ . As you can see in fig 4.1, when the  $v_{DS}$  voltage in off state is equal to 100V, we actually measure  $v_{DS} = 2.27V$  in on-state, therefore we can consider the measurement to be correct. In this case, if we calculate the vertical resolution of the scope, it is  $\frac{VBUS}{256} = \frac{100V}{256} = 390mV$ . 390mV infact represents a good resolution to measure 2.27V. This is the reason why the measurement is correct.

Now let us give a look to fig 4.2, where the  $v_{DS}$  voltage in off state is equal to VDD = 200V. In this case, if we calculate the vertical resolution of the scope, it is  $R = \frac{VBUS}{256} = \frac{200V}{256} = 780mV$ . 780mV does not represent anymore a perfect resolution to measure 2.27V, therefore the  $v_{DS}$  measured

Figure 4.2: Problems with the vertical resolution of the scope.  $R = \frac{VBUS}{256} = \frac{200V}{256} = 780mV$ : at VBUS=200V the  $v_{DS}$  measured is 1.9V too high [4].

is too high, comparing with the typical value.

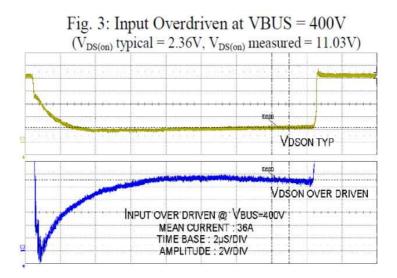

In the end, regarding fig 4.3, where the  $v_{DS}$  voltage in off state is VDD = 400V, we actually measure  $v_{DS} = 11.03V$ , therefore the measurement is completely wrong. In this case, infact, if we calculate the vertical resolution of the scope, it is  $R = \frac{VBUS}{256} = \frac{400V}{256} = 1.6V$ , that is too small in order to measure 2.27V, therefore the evaluated  $v_{DS}$  is completely wrong.

According to this observations, we can say that the larger is the range of values of the signal on the scope, the worse will be the measurement's accuracy. Reagarding the the  $v_{DS}$  signal, there is a huge step between the small value of  $v_{DS}$  in on state we want to evaluate (in the order of mV or few volts) and the value of  $v_{DS}$  in off state, VBUS, during the stress period. Actually we want to measure the value of  $v_{DS}$  in on state, regardless to the value of  $v_{DS}$  in off state: we would like somehow to cut the upper part of the  $v_{DS}$  signal, in order to have a higher accuracy on the value of  $v_{DS}$  in on state we are interested in. The solution to use is the so called *clamping circuit*,

Figure 4.3: Problems with the vertical resolution of the scope.  $R = \frac{VBUS}{256} = \frac{400V}{256} = 1.6V$ : Between 200V and 400V the scope input amplifier is substantially overdriven and the results are definitely wrong [4].

that gives us the possibility of measuring a clamped value of the drain-source voltage:  $v_{DS}$  clamped, instead of  $v_{DS}$ . The schematic of the clamping circuit will be shown in a more detailed way in section 4.2.

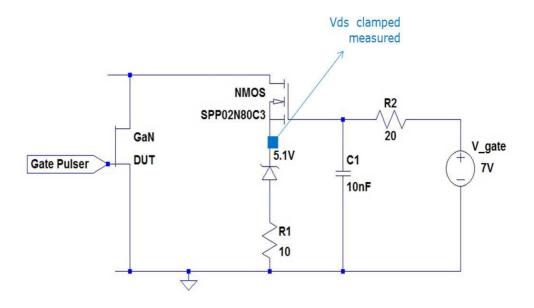

### 4.2 Clamping Circuit - Schematic

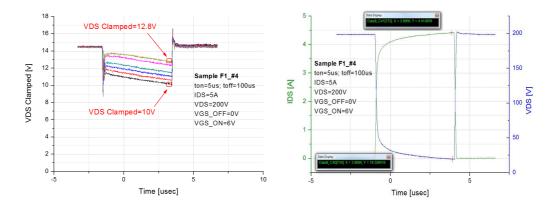

The schematic of the clamping circuit we used is shown in fig 4.4 [8]. The GaN device under measurement (DUT) is put in parallel with an NMOS. In series with the NMOS there are a zener diode and a small reistance R1. The DUTs  $v_{DS}$  clamped is the voltage drop measured across the series composed by the zener diode and the resistance R1, present for safety reasons, as it is indicated in fig 4.4. The gate potential of the NMOS is driven by a power supply ( $V_{gate}$  in fig 4.4), that gives about 7V DC, in order to have  $V_{GS_{NMOS}} \approx V_{th} \approx 2V$  continously, therefore a small drain-source current is flowing throw the NMOS device, when it is in on-state. The gate driver's power supply is followed by a low pass filter.

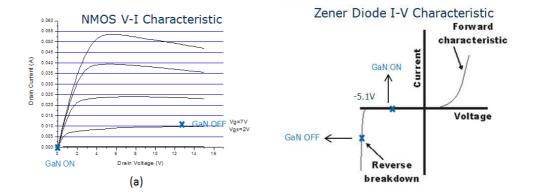

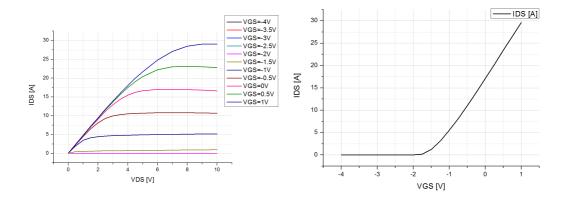

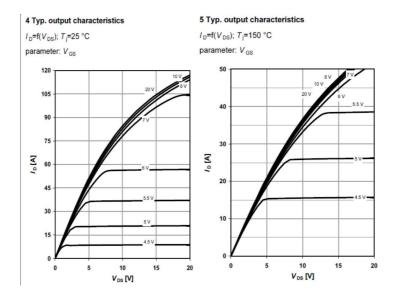

The I-V characteristics of the NMOS and of the zener diode, shown in fig 4.5, can help us to better understand how the circuit works. Let us study separately what happens when the GaN DUT is in on or in off-state.

When the DUT is switched off, the voltage drop between drain and source is equal to the voltage VBUS, provided by the drain battery shown in fig 3.15; therefore the NMOS is switched off and supports quite all the drain-source voltage drop across the GaN DUT. For this reason we chose an NMOS with a very high breakdown voltage, equal to 800V. The NMOS's drain-source current is flowing also throw the zener diode, therefore the zener diode is working in the breakdown region with  $V_{zener} \approx 5.1V$  (in case of a 5.1V zener diode). The GaN DUT drain-source voltage drop is then shared by the NMOS and the zener diode (the voltage drop on the resistance R1 can be considered negligible, since the current flowing throw the NMOS is very small).

On the other hand, when the GaN DUT is in on-state, the drain-source voltage drop on it is very small; therefore the NMOS is switched on and both the drain-source current flowing throw it and the drain-source voltage are very small (NMOS I-V characteristic in fig 4.5). As for the zener diode's I-V characteristic, the voltage measured on the zener diode is exactly equal to the  $v_{DS}$  drop on the GaN DUT.

In this way, when the GaN device is switched on,  $v_{DS}$  clamped gives exactly the  $v_{DS}$  drop across the GaN DUT, whereas, when the GaN device is off,  $v_{DS}$  clamped is limited to the breakdown voltage of the zener diode we are using; in this case Vz= 5.1V.

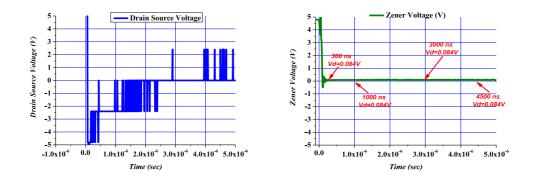

In fig 4.6 and 4.7 are shown the  $v_{DS}$  measurements made on a silicon  $90m\Omega$  coolMOS device without clamping circuit (waveforms on the left in fig 4.6 and then with clamping circuit (waveforms on the right in fig 4.6. In fig 4.6 the waveforms at the first sight seem to have the same level of accuracy. In fig 4.7 you can see the same waveforms shown in fig 4.6, respectively, but zoomed: here you can notice the huge difference between the measurements with and without clamping circuit. In the measurement without clamping circuit, infact, due to the low vertical resolution, the scope is not able to distinguish between different quantized values; when the clamping circuit is

Figure 4.4: Clamping Circuit's Schematic.

Figure 4.5: I-V Characteristic of the NMOS (a) and I-V characteristic of the Zener diode (b) used in the clamping circuit in fig 4.4.

used, vice versa, the signal's value is very clear.

Figure 4.6: Drain-source voltage drop  $v_{DS}$  measured under pulsed conditions in a silicon coolMOS device, without using the clamping circuit (on the left) and with the clamping circuit (on the right).

Figure 4.7: Zoomed drain-source voltage drop  $v_{DS}$  measured under pulsed conditions in a silicon coolMOS device, without using the clamping circuit (on the left) and with the clamping circuit (on the right). The CollMOS static Rdson measured at VGS=10V and IDS=1A is *StaticRdson* = 87.73m\Omega

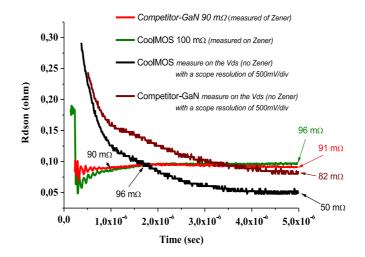

The graph in fig 4.8, moreover, shows a comparison between the Rdson values of a silicon and of a GaN device, calculated with and without using the clamping circuit. We can see the high accuracy of the measurement that we obtain thanks to the the clamping circuit, comparing to the measurement of  $v_{DS}$  without that. The signal evaluated without clamping circuit, infact,

is completely wrong.

Figure 4.8: Comparison between the drain-source voltage of two different devices (a silicon device and a Gan device) measured under pulsed conditions with and without clamping circuit.

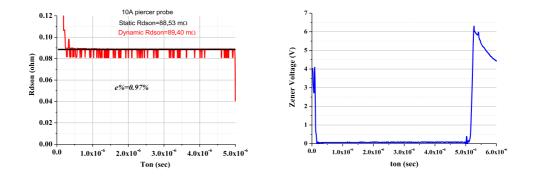

In order to understand how much our measurement is accurate, we have measured the static Rdson of a  $90m\Omega$  silicon coolMOS device for different values of the drain-source current; then we have compared that with the dynamic Rdson, measured with our dynamic rdson setup in quasi-static conditions, by using the clamping circuit. We measured the static Rdson value thanks to a particular machine capable of a very high accuracy (fig 4.9). By applying 10V between gate and source and by using different values of drain-source current we obtained:

- $IDS = 10A \rightarrow Rdson = 88.53m\Omega$

- $IDS = 7.5A \rightarrow Rdson = 87.71m\Omega$

- $IDS = 5A \rightarrow Rdson = 86.82m\Omega$

- $IDS = 1A \rightarrow Rdson = 83.75m\Omega$

Figure 4.9: Static Tester M3020 used for measuring the static Rdson.

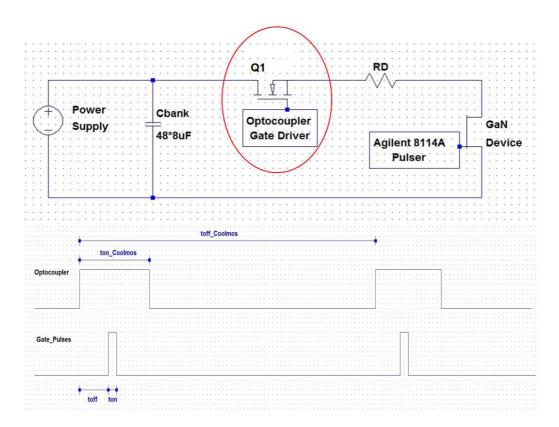

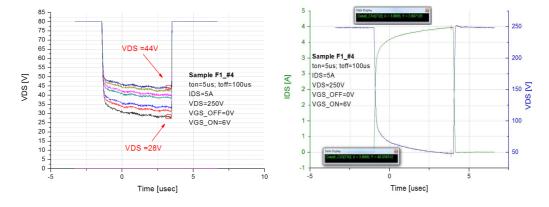

In fig 4.10, on the left, you can see the comparison between the static Rdson, measured with our static tester, and the one measured with our setup in quasi-static conditions for  $I_{DS} = 10A$ . The scopes vertical resolution is  $R = \frac{VBUS}{256} \approx frac6V256 = 23V$ . Since the current is equal to 10A, the device has  $R_{DSon_STATIC} = 88.53m\Omega$ , therefore the drain-source voltage drop I want to measure is  $v_{DS} = 885.3mV$ ; then the error mistake is negligible and equal to  $e = \frac{89.4-88.53}{88.53} = 0.97\%$ .

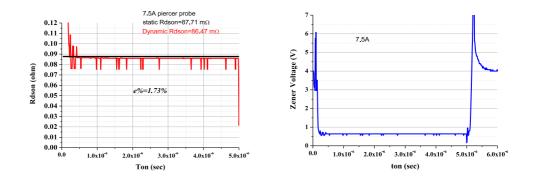

Referring to the same type of measurement in fig 4.11, since the current is 7.5A, and the device has  $R_{DSon_STATIC} = 87.71m\Omega$ , the drain-source voltage drop I want to measure is  $v_{DS} = 657.8mV$ ; then the error mistake is very small, as in the previous case, and equal to  $e = \frac{86.47-87.71}{87.71} = 1.73\%$ .

Again, referring to fig 4.12, since the current is 5A, and the device has  $R_{DSon_STATIC} = 86.82m\Omega$ , the drain-source voltage drop I want to measure is  $v_{DS} = 433.1V$ ; the error mistake I make is therefore quite small and equal to  $e = \frac{87.71-86.82}{86.82} = 2\%$ . As for a general agreement, a measurement is supposed to be correct until the error is e < 2%.

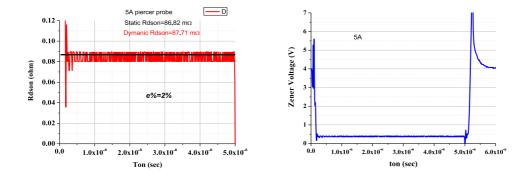

In the end, in fig 4.13, you can see the  $R_{DSon_STATIC}$  measured for IDS = 1A. Since the current is 1A and the device has  $R_{DSon_STATIC} = 83.75m\Omega$ , the drain-source voltage drop I want to measure is  $v_{DS} = 83.75V$ ; the error mistake is therefore very big and equal to  $e = \frac{97.21-83.75}{83.75} = 13.8\%$ .

Figure 4.10: Comparison between the static Rdson measured with the machine (black line) and the dynamic rdson measured with our setup and with the clamping circuit in quasi-static conditions (red line) with  $I_{DS} = 10A$  (on the left);  $v_{DS}$  clamped (on the right).

Figure 4.11: Comparison between the static Rdson measured with the machine (black line) and the dynamic rdson measured with our setup and with the clamping circuit in quasi-static conditions (red line) with  $I_{DS} = 7.5A$  (on the left);  $v_{DS}$  clamped (on the right).

Figure 4.12: Comparison between the static Rdson measured with the machine (black line) and the dynamic rdson measured with our setup and with the clamping circuit in quasi-static conditions (red line) with  $I_{DS} = 5A$  (on the left);  $v_{DS}$  clamped (on the right).

As we can see from these datas, the bigger is the drain-source current, the bigger is the error I make by measuring  $v_{DS}$  clamped and, therefore, Rdson. This error is clearly related to the limitation of the scopes vertical resolution: if the resolution is equal to R = 23mV, when the value I have to evaluate is in the range of 600-400mV, the result is accurate and the error I make is as maximum equal to e = 2%; whereas, for smaller values of the drain-source current, the  $v_{DS}$  clamped to be measured is smaller than 100mV, therefore my measurement is for sure less accurate, because the value I am evaluating is comparable with the vertical resolution.

Even though the clamping circuit is a very strong ally, errors and imperfections unfortunately belong to every measurement, we can only try to cut them down, but we will never manage to remove them completely. Until now we have used a 5.1V zener diode for our clamping circuit. What we can do, in order to improve our accuracy, also in case of low drain-source currents, is using a zener diode with a smaller brakdown voltage.

Figure 4.13: Comparison between the static Rdson measured with the machine (black line) and the dynamic rdson measured with our setup and with the clamping circuit in quasi-static conditions (red line) with  $I_{DS} = 1A$  (on the left);  $v_{DS}$  clamped (on the right).

# Chapter 5

# GaN DReaM - GaN Dynamic Rdson Measurement Setup

### 5.1 The Old Dynamic Rdson Measurement Setup

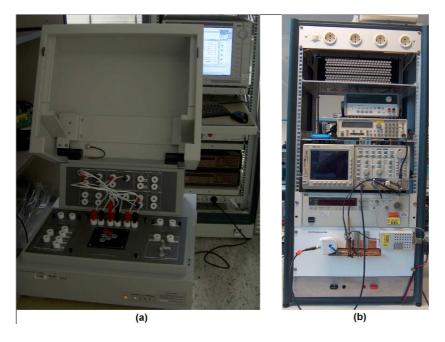

In this chapter we want to better understand how our dynamic Rdson measurement setup is build and how it works.

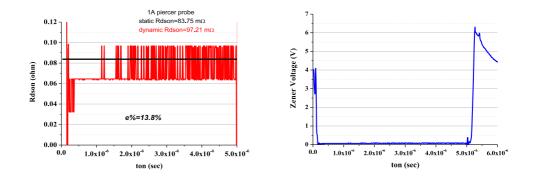

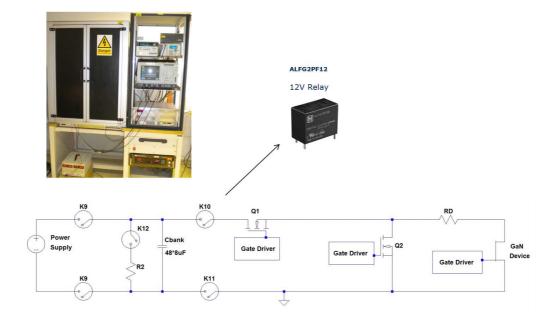

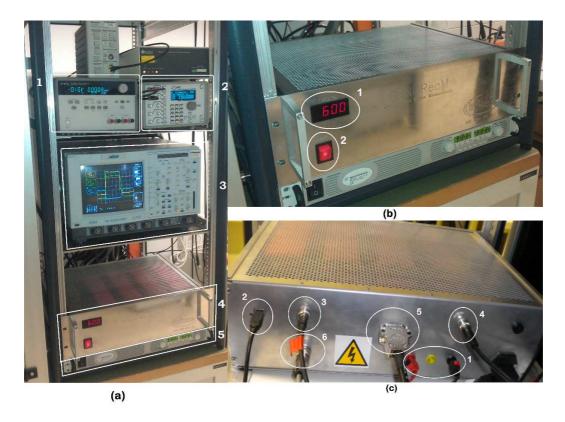

In fig 3.15 is shown a very simple schematic of the dynamic Rdson measurement circuit we used. Referring to fig 3.15, the drain potential of the device under test (DUT) is continously connected to the main power supply, so that, when the device is in off-state, it is continously stressed with a drain voltage value that can go up to 600V (maximum output voltage for our power supply Agilent N5752A); in the real circuit we inserted a switch between the power supply and the DUT, so that the DUT is connected to the main power supply only for a short period of time, that is equal to the sum of the stressing time( $t_{off}$ ) and the on-time  $t_{on}$  of the DUT (fig 5.1); after this time period the coolMOS is switched off, so that the device can have a rest before that the next stress time starts. Let us give a look to fig 5.1: here we can see the same circuit shown in fig 3.15, but with a new part circled in red: we introduced infact a high breakdown voltage coolMOS silicon device (Q1), put in series with the main power supply, with the aim of limiting the stress time of the DUT. The coolMOS Q1, infact, behaves as a switch: it lets the current flow from the power supply to the DUT while Q1 is in on-state, whereas, while Q1 is switched off, the drain of the DUT is disconnected from the power supply and the coolMOS Q1, thanks to its high breakdown voltage, can support up to 650V. As for the on-state drain-source voltage drop on the coolMOS Q1, it is negligible, infact  $Rdson\_coolMOS = 37m\Omega$ ; let us make a fast calculation in the worst case, by considering  $IDS_{max} = 20A$  we obtain:

$$VDS\_CoolMOS\_max = IDS_{max} * Rdson = 20A * 37m\Omega = 0.74V \quad (5.1)$$

value that, in comparison with the output voltages we set on the main power supply (from 25V up to 600V), can be considered negligible.

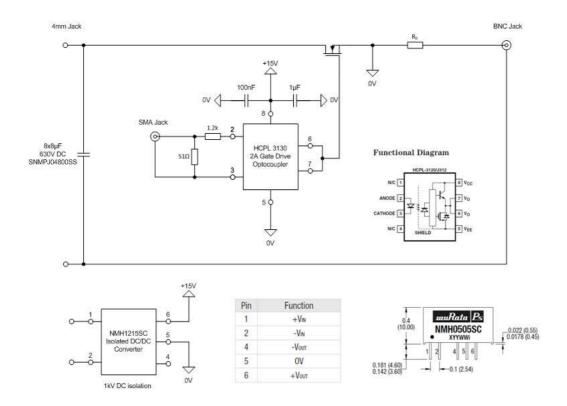

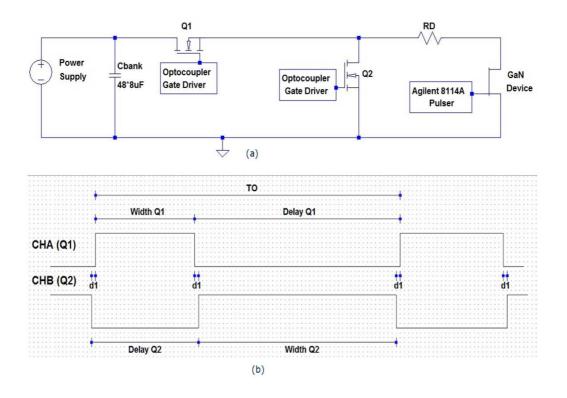

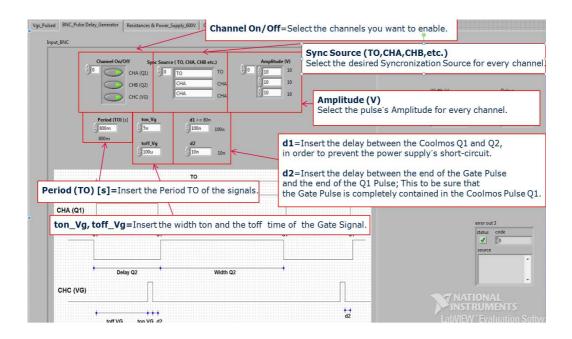

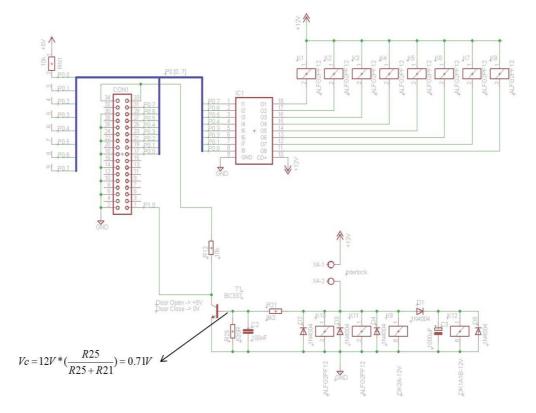

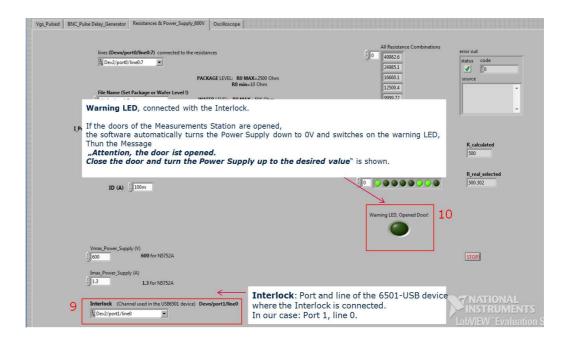

A much more detailed schematic of the circuit in fig 5.1 is shown in fig 5.2. The gate of the coolMOS Q1 is driven by the output of a gate drive optocoupler. The optocoupler is driven by the channel A of the BNC 575 Pulse Delay Generator, shown in fig 5.3(a), that therefore gives the switch-on and switch-off times of the coolMOS Q1.

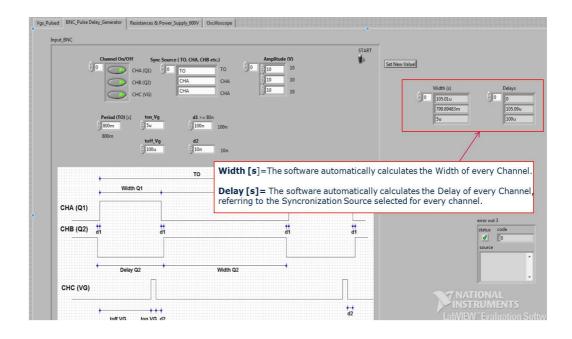

Now let us understand how the BNC instrument works: the BNC 575 Pulse Delay Generator is an instrument with different output channels; on every channel it can deliver a square wave signal; the square wave period, that is the same for every channel, can be set by the user. The instrument, moreover, gives the possibility of synchronizing each channel with another channel of the instrument or with an external signal. In every channel, furthemore, you can insert a delay with respect to the synchronization source. This instrument owns a very high precision, infact it is possible to define the width of the pulse or the delay of every channel, with respect to the synchronization source, by using up to 15 decimal digits.

After have understood how the BNC instrument works, let us come back to the description of the dynamic Rdson measurement circuit in fig 5.2: the gate drive optocoupler is supplied throw a 15V DC/DC converter, connected to an auxiliary 12V power supply. The 15V DC/DC converter, shown on the

Figure 5.1: Dynamic Rdson Measurement Circuit Schematic. The switch Q1 has the aim of avoiding to stress too much the GaN DUT with the continous voltage coming from the main power supply.

bottom part in fig 5.1, gives us the possibility of galvanic isolation of the 12V auxiliary power supply. The two capacitances connected to the optocoupler's 15V supply terminal have the aim of mantaining the optocoupler's voltage constant, with the aim of avoiding voltage overshoot, that could damage the optocoupler itself.

Now we would like to understand how the gate signal of the DUT is driven: we would like the gate signal to come directly from the BNC 575 Pulse Delay Generator, in order to synchronize the gate signal with the coolMOS Q1 and to minimize the number of instruments used. Unfortunately the BNC instrument is not capable of delivering pulses with negative amplitude, so that we cannot directly drive normally-on devices by using one channel of the BNC instrument. Since that, the DUT's gate potential comes from the output of the Agilent 8114A Pulser (fig 5.3(b)), capable of delivering both positive and negative voltages. The output signal of the Agilent Pulser is triggered with the channel C of the BNC 575, that gives the delay time  $(t_{off\_VGS})$  and the width  $(t_{on_VGS})$  of the gate signal. The on-time and off-time of the coolMOS signal are given by the channel A of the BNC instrument: this in order to have the possibility of synchronizing the gate signal with the Q1 signal, by syncronizing channel C with channel A. On the bottom part in fig ?? you can see an example of the gate signal and of the signal associated with the on and off-time of the coolMOS Q1: when the coolMOS signal pulse is up, it means that the device is in on-state and, vice versa, when the signal pulse is down, it means that the device is in off-state. As you can see in fig 5.1, Q1 is in on-state only during the time necessary to cover the delay time  $(t_{off}VGS)$ and the width $(t_{on_VGS})$  of the gate signal, in order to avoid stressing too much the DUT.

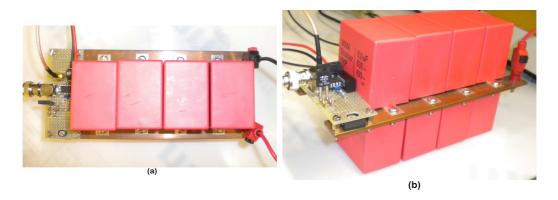

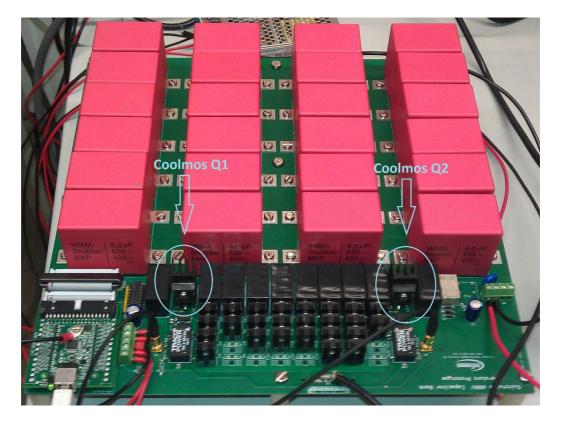

In fig 5.4 is shown the top view and the side view of the first Dynamic Rdson Measurement setup we used. In pink you can see the block of capacitance, in parallel with the main power supply. The capacitance is composed by eight capacitors of  $8\mu F$  eachone. They are mounted in parallel on two copper bars, therefore the total capacitance value is:

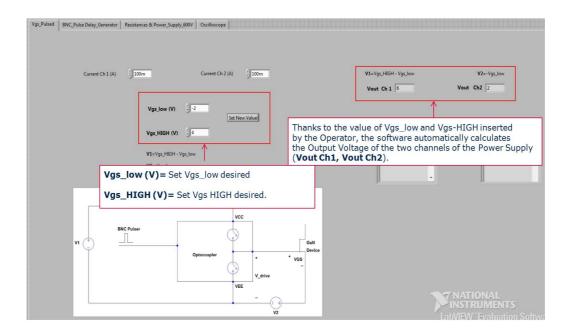

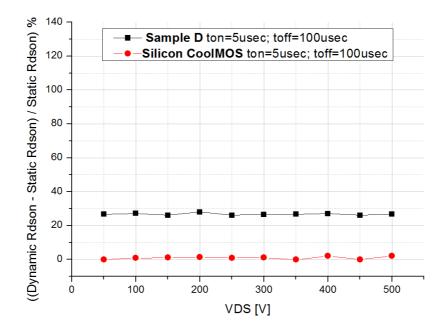

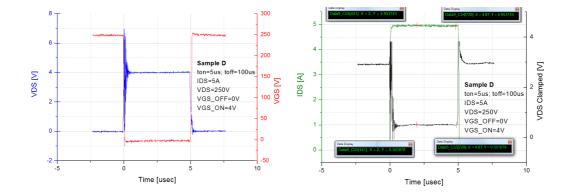

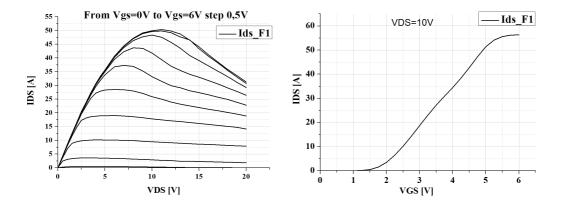

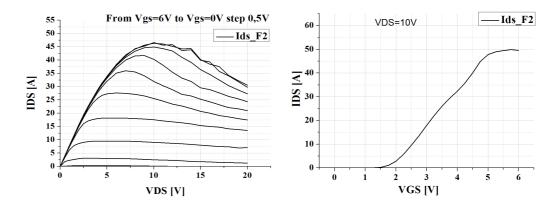

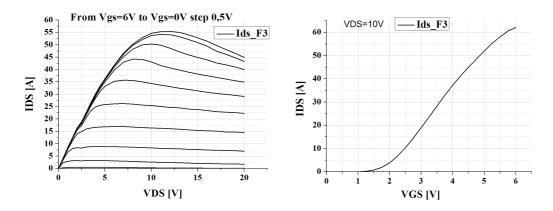

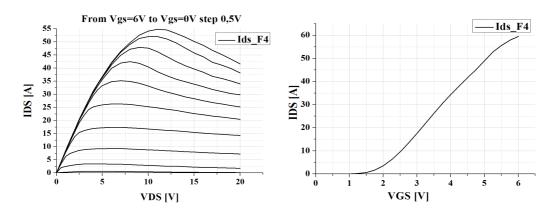

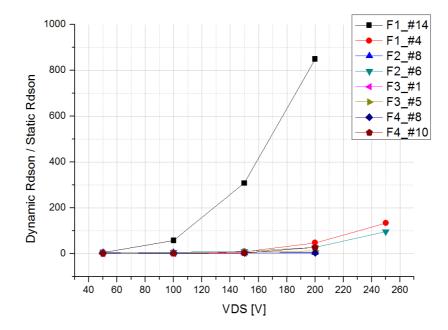

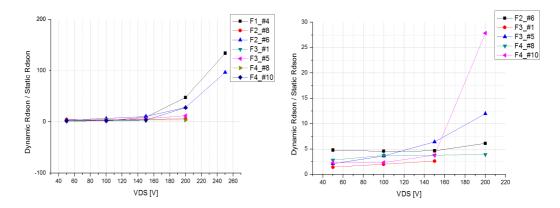

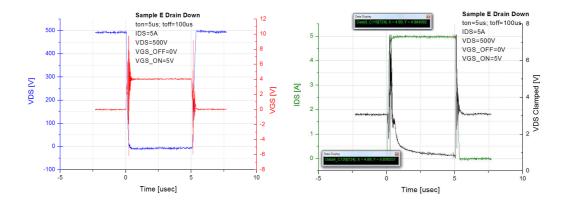

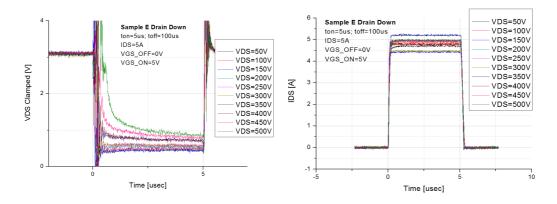

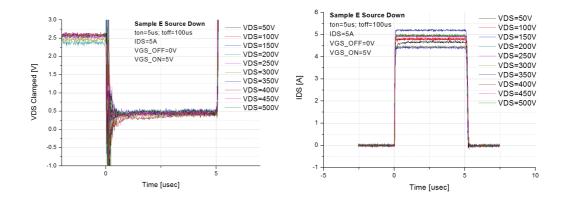

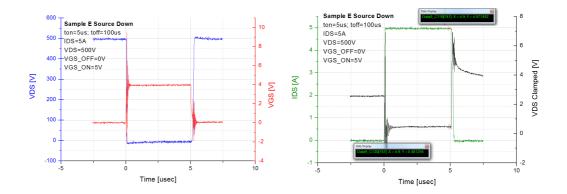

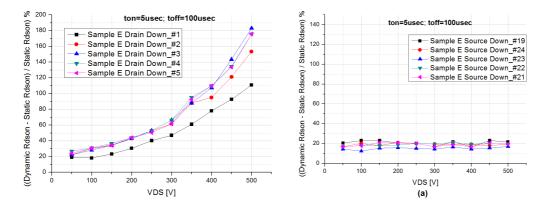

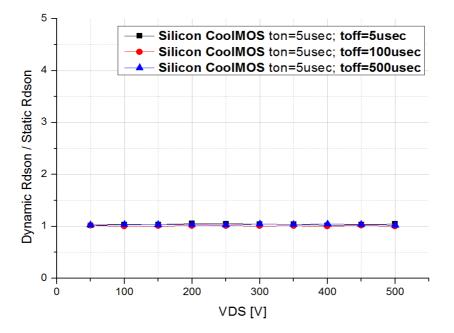

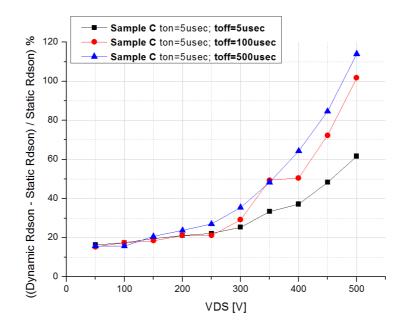

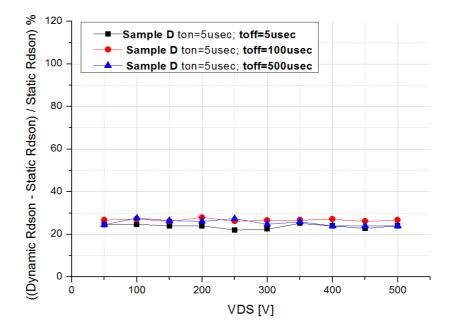

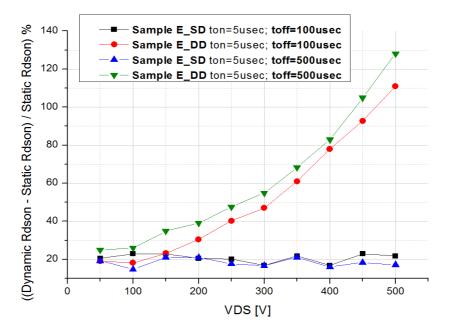

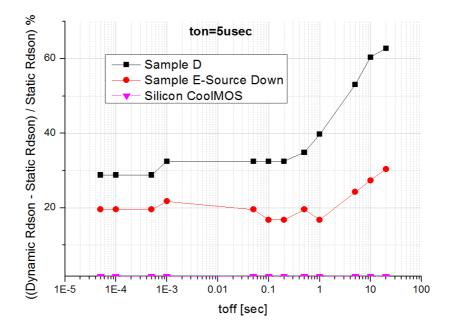

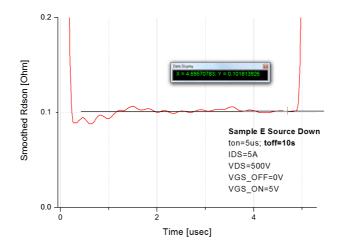

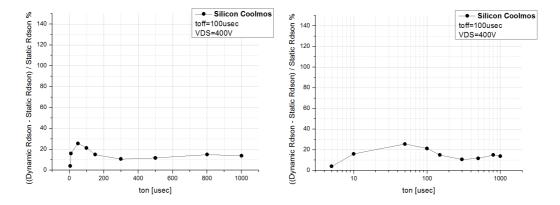

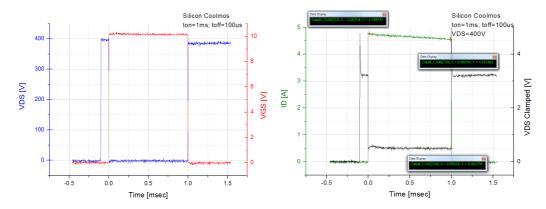

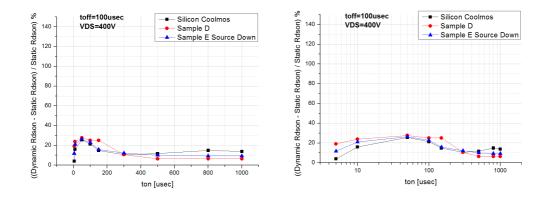

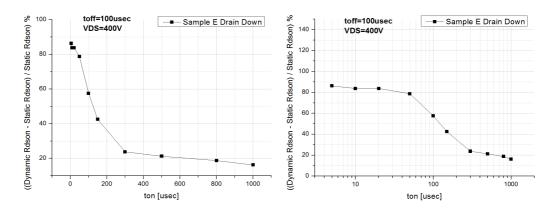

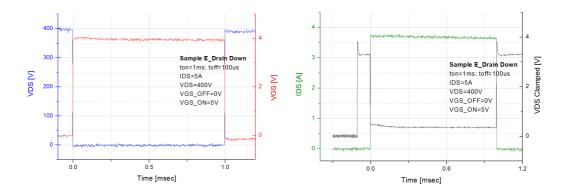

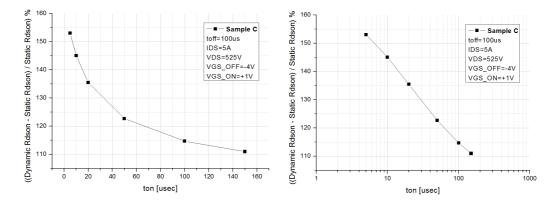

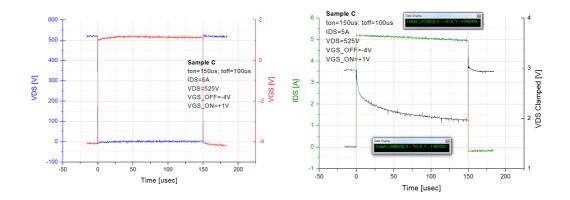

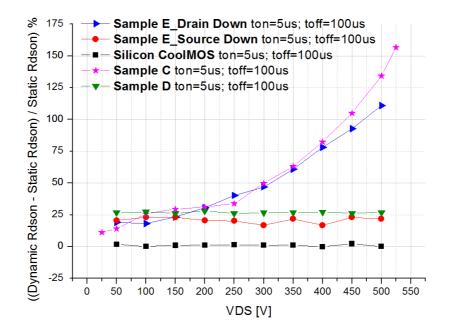

$$C_{bank} = 8 * 8\mu F = 64\mu F \tag{5.2}$$